# **JFET Characteristics**

# Objective

Although arguably the first transistor invented the field-effect transistor did not become established as an important semiconductor device until experience with the BJT had established a broadened understanding of semiconductor phenomena and technology. In this note distinctions between the Junction Field-Effect Transistor (JFET) and the Bipolar Junction Transistor are examined. Static terminal characteristics of two representative JFETs are examined using a PSpice computer analysis of a sophisticated device model.

Although the JFET is a different device from the BJT nevertheless various aspects of device use are similar in general concept if not in precise detail. The following paragraph is a modest paraphrase of that introducing the note on BJT Biasing.

In general all electronic devices are nonlinear, and operating characteristics can change significantly over the range of parameters under which the device operates. The junction field-effect transistor, for example, has a 'normal' amplifier operating drain voltage range bounded by the VCR range for low voltages and drain-gate junction breakdown for high voltages. It also is bounded by excessive drain current on the one hand and cutoff on the other hand. In order to function properly the transistor must be biased properly, i.e., the steady-state operating voltages and currents must suit the purpose involved. Our primary concern here however is not to determine what an appropriate operating point is; that determination depends on a particular context of use and even more so involves a degree of judgment. Rather we consider how to go about establishing and maintaining a given operating point. Where a specific context is needed for an illustration we assume usually that the transistor is to provide linear voltage amplification for a symmetrical signal, i.e., a signal with equal positive and negative excursions about a steady-state value.

# **Junction Field Effect Transistor**

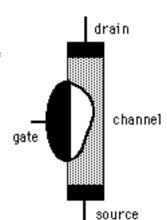

The Junction Field-Effect Transistor (JFET) is a device providing a controlled transport of <u>majority</u> carriers through a semiconductor. The figure illustrates the essential nature of the JFET <u>topology</u>, actual geometry varies depending on the intended application and fabrication techniques. The JFET is at its heart a nonlinear resistor fabricated from a doped semi-conductor material. To be specific we refer to an 'N-channel' device, meaning the conducting material is an N-type semiconductor. Operation of the complementary P-channel device operation is similar and can be inferred directly from the N-channel discussion. In the figure the lightly shaded region is the conducting channel. The darker regions at the ends of the channel are relatively heavily doped terminations for the channel to assure good connections to externally accessible terminals.

By convention the terminal designations are defined so that carriers (electrons for the N-channel device) flow <u>from</u> the source and <u>to</u> the drain. For the N-channel device, therefore, a voltage is assumed to be applied so that the drain is positive relative to the source.

The resistance of the channel is a function of its geometry and the electron transport parameters of the doped semiconductor. The device as described thus far is more or less a (temperature-sensitive) resistor. Suppose now that the channel geometry is changed, e.g., by gouging out the white area shown on the left side of the channel. This is a change of channel geometry, in particular a smaller channel cross-section , which increases the channel resistance, and therefore for a given drain-source voltage less current will flow after the gouging. Even less current flows with further gouging. We have then a variable resistance, although a mechanically 'gouged' the resistor would have a short service life.

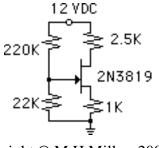

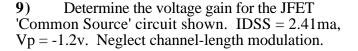

On the other hand the channel cross-section can be effectively varied without physically removing material. That is, charge carriers can be effectively removed from part of the cross-section <u>electrically</u> reducing the

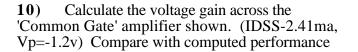

Introductory Electronics Notes The University of Michigan-Dearborn

60-1

channel cross-section and so reducing its conductivity, without actual removal of bulk material. To effectively remove carriers from a region we simply need to 'shove' them out of that region, and the way to shove a charged carrier is with an electric force. The JFET makes use of the fact that a very strong electric field exists across a PN junction, and that field effectively removes carriers from the junction region. The 'gate' electrode shown in the figure is formed as a PN junction, with the channel forming one side of the junction. The gate side of the junction is relatively heavily doped so that the junction depletion region extends largely into the channel.

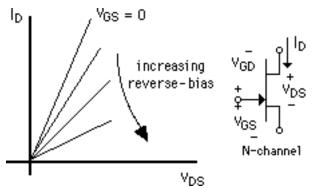

The width of the depletion region increases with increasing reverse-bias, extending further into the channel and further increasing the channel resistance. For <u>small</u> values of drain-source voltage the JFET characteristic is linear, as illustrated by the sketch. Increasing the magnitude of the (reverse-biased) gate-source voltage increases the depletion width and increases the channel resistance. The drain characteristics correspond to a variable resistor, with a voltage-controlled resistance.

The conventional JFET icon for an N-channel device also is shown in the figure, and is identified as to type by the gate terminal PN junction arrow. Note that following common convention the drain current is positive (in the direction of the current polarity arrow shown) for an electron carrier flow from source to drain.

The P-channel device icon would have the gate arrow reversed, and the voltage polarities also would be reversed so that normally the hole carriers flow from source to drain, and the gate junction is reverse-biased.

The reason for the emphasis on <u>small</u> values of drain-source voltage in the discussion above arises from the fact that the gate junction extends a significant distance <u>along</u> the channel length as well as across the channel width. Since the channel is a continuous resistor there is a voltage drop along the length of the channel, and so the gate reverse-bias actually varies along the gate perimeter. The general shape of the depleted region in the earlier illustration is not accidental. It is intended to reflect the increasing junction reverse-bias voltage, and the consequent increasing depletion region width, moving from the source towards the drain. In addition of course the reverse-bias changes as the drain-source voltage changes, and so there is an influence of the drain-source voltage on the resistance of the channel. In this respect make careful note of the fact that the junction voltage is <u>not</u> the same as the gate-source voltage; it is the channel and not the source terminal that forms one side of the junction. As already noted because of the voltage variation along the channel the width of the depletion region width changes as the drain-source voltage changes as the drain-source voltage.

ΙD

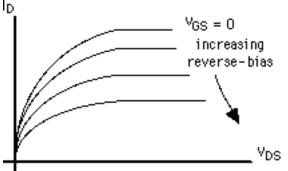

Indeed, as the drain-source voltage increases (for an Nchannel device) the reverse bias across the junction increases and the channel carries <u>less</u> current for a given voltage than it would otherwise. The drain characteristics viewed over a larger range of drain-source voltage than before appear (roughly) as shown to the right.

As the drain-source voltage increases further a condition known colloquially as 'pinch-off' occurs; this is the condition wherein (theoretically) the depletion region extends entirely across the channel. This occurs initially at the drain end of

Introductory Electronics Notes The University of Michigan-Dearborn Copyright © M H Miller: 2000 revised

′GS = 0

increasing

reverse-bias

modulation' effect is considered further later. The channel current is (to first-order) fixed by the conditions when pinch-off occurs; all carriers forming the source-end current are swept across pinch-off junction region by the strong electric field. This is (roughly) similar to the carrier injection through the base of a BJT, although the mechanism of carrier injection is different.

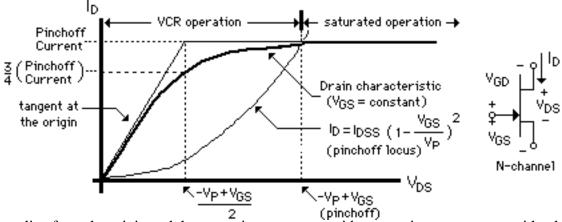

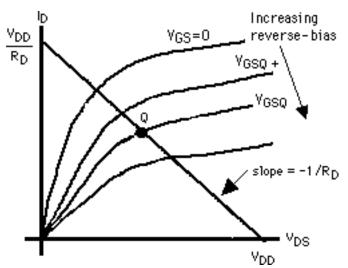

A still more extended range of variation of the drain characteristics is sketched to the right. The voltagecontrolled (VCR) region, i.e., operation before pinch-off, is conventionally called (mostly) just that, i.e., VCR region. The 'constant' current (pinch-off) region to the right is 'saturation' (probably all the remarks respecting a conflict with BJT terminology already have been said, repeatedly).

To summarize: the JFET carrier-transport channel conductivity is modified by the electric field associated with the depletion region of a reverse-biased junction which

extends into the channel. The nature of the control process is such that the ability of the channel to carry current is greatest when the control junction has zero bias (or slightly positive, but well below the diode 'knee') and decreases with increasing reverse bias. A JFET thus inherently is a device that is 'full on' with no control exerted, and is turned off with increasing reverse bias. This is 'depletion-mode' operation, so-called after the nature of the physical process through which control is exerted.

The details of the <u>physics</u> underlying the terminal behavior are complex. However it is the <u>terminal</u> behavior and not a quantitative physical explanation for that behavior that is the principal concern here. An exact form of a theoretical expression for a drain characteristic depends on details of both geometry and doping. However various theoretical expressions, despite major differences in mathematical appearance, actually produce very similar numerical characteristics. Thus we describe a commonly used 'working' expression, a quadratic first-order approximation for a drain characteristic <u>in the VCR region of operation</u>, which has the advantage of relative simplicity and adequacy for initial design purposes. This working expression is the quadratic equation:

$$I_{D} = 2I_{DSS} \left\{ (1 - \frac{V_{GS}}{V_{P}}) \frac{V_{DS}}{-V_{P}} - \frac{1}{2} \left( \frac{V_{DS}}{V_{P}} \right)^{2} \right\}$$

Vp is the 'pinch-off' voltage, i.e., the <u>gate-to-drain</u> voltage at which the channel first becomes pinched. 'Pinch-off' is defined as the point where maximum drain current (for a given gate voltage) occurs; the current is assumed to remain substantially unaffected by the drain voltage thereafter. Differentiate the expression to determine that the drain-source voltage at which pinch-off occurs is  $V_{DS} = -V_P + V_{GS}$ ; note (for a N-channel device) that -Vp is positive, that  $V_{GS}$  is negative, that 0 V<sub>GS</sub> Vp, and because of all this that  $V_{DS}$  0 at pinch-off!

As the expression indicates the drain current ID is zero for  $V_{DS} = 0$  whatever the gate bias. This is notably different from the BJT, where there is a small (millivolts) collector-emitter voltage for zero collector current, and zero offset can be an advantage in applications where the JFET is used as an analog switch.

The <u>maximum</u> current for a given gate bias occurs at  $V_{DS} = V_{GS} - V_P$ , i.e., at pinch-off, and is given by the first-order expression

$$I_{D(max)} = I_{DSS} \left(1 - \frac{V_{GS}}{V_{P}}\right)^2$$

This latter quadratic expression is the locus of the pinch-off points on the common source (ID vs. VDS, with VGS as a parameter) characteristics. The theoretical equations are described graphically in the figure following. The drain current follows the quadratic expression up to its apex (i.e., over the VCR range), at which point pinch-off occurs and the drain current then remains roughly constant into the saturation range. (Not shown is the drain-gate reverse-bias breakdown at higher drain voltages; 2N3819 device

Introductory Electronics Notes60-3Copyright © M H Miller: 2000The University of Michigan-Dearbornrevised

characteristics presented later show this phenomena.) The quadratic pinch-off characteristic, i.e., the locus of the drain current at pinch-off for different gate-source voltages also is drawn on the figure. Straightforward calculation shows that the extension of the tangent <u>at the origin</u> to the pinch-off current level intersects that current where VDS equals <u>half</u> the pinch-off voltage, i.e., (- VP+VGS)/2. The actual current at this voltage is 3/4 the pinch-off current.

The tangent line from the origin and the saturation current provide convenient asymptotes with which to sketch a characteristic fairly accurately; note again that the actual current is 3/4 that at the intersection of the asymptotes.

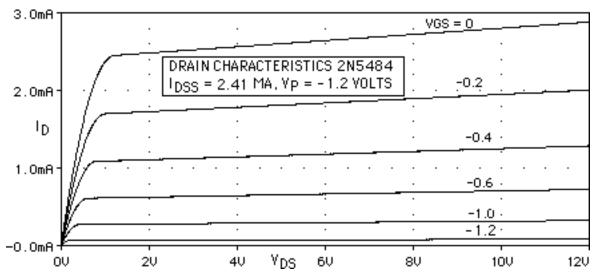

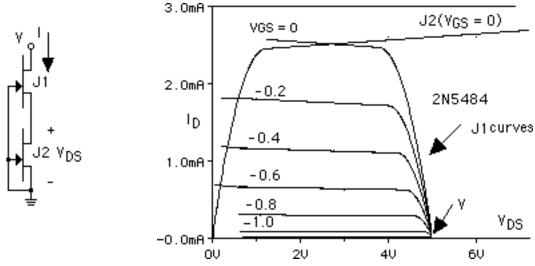

# **Drain Characteristics for 2N5484 N-Channel JFET**

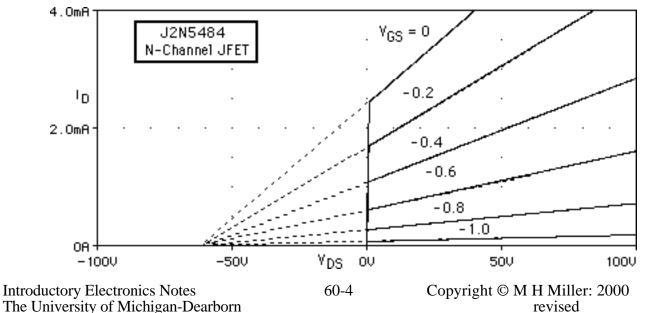

Common-Source drain characteristics <u>computed</u> for the 2N5484 N-channel JFET PSpice model are plotted below over a large voltage range; the voltage range is chosen to provide emphasis for certain aspects of the characteristics. Note however that operation with  $V_{DS} < 0$  is quite inappropriate. In effect the roles of the source and drain are interchanged, the gate junction becomes <u>forward-biased</u>, and the resulting large gate current is virtually certain to lead to destruction of the device.

| *JFET 2N5484 Characteristics |     |      |     |       |      |  |

|------------------------------|-----|------|-----|-------|------|--|

| VDS                          | 2   | 0    |     | DC    | 12   |  |

| VGS                          | 1   | 0    |     |       | 0    |  |

| J2N5484                      | 2   | 1    | 0   | J2N5  | 5484 |  |

| .LIB EVAL.LIB                |     |      |     |       |      |  |

| .OP                          |     |      |     |       |      |  |

| .PROBE                       |     |      |     |       |      |  |

| .DC VDS                      | 01. | 5.01 | VGS | -1.20 | 0.2  |  |

| .END                         |     |      |     |       |      |  |

The left half-plane is included only to display an effect similar to the Early Effect for the BJT, i.e., a <u>second-order</u> dependence of the drain current on the drain-source voltage. (The scale is chosen, as stated before, to overemphasize this dependence; the slope of the curves is only of the order of a few kilohms.)

The 'channel-length modulation effect causes the characteristics to converge at a common intersection, about -60 volts for the 2N5484.

To account for this effect analytically the saturation characteristics may be multiplied by a factor  $1+V_{DS}$ , essentially the leading terms of a series expansion:

$$|D(max)=|DSS(1-\frac{V_{GS}}{V_{P}})^{2}(1+\lambda V_{DS})$$

The <u>channel-length modulation parameter</u> is the inverse of the common drain-source voltage at which the several curves meet.

The VCR expression is multiplied by the same factor so as to make the two expressions predict the same current at pinch-off as well as  $V_{DS} = 0$ .

$$I_{\mathsf{D}} = 2I_{\mathsf{DSS}} \left\{ \left(1 - \frac{V_{\mathsf{GS}}}{V_{\mathsf{P}}}\right) \frac{V_{\mathsf{DS}}}{-V_{\mathsf{P}}} - \frac{1}{2} \left(\frac{V_{\mathsf{DS}}}{V_{\mathsf{P}}}\right)^2 \right\} \left(1 + \lambda \nabla_{\mathsf{DS}}\right)$$

(Note that the value of corresponding to the -60 volt common intersection for the 2N5484 is 0.017.) In general the second-order correction is small and generally can simply be neglected for preliminary design calculations. Computer models use these equations with the parameters IDSS, V<sub>p</sub>, and <math>chosen to match measured device characteristics.

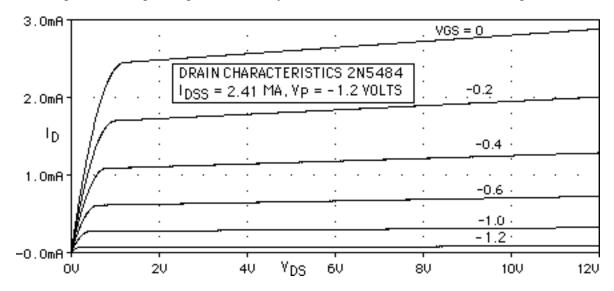

The common-source characteristics are redrawn below, this time to emphasize a more appropriate range of operation. Note that for  $V_{DS} > -V_P$ , i.e., when the device operates in saturation, the characteristics closely resemble in appearance those of the BJT. One notable distinction is that the control parameter is gate-source voltage, and not a (base) current as for the BJT. Indeed the gate current of a JFET corresponds to a reverse-biased junction, and therefore is very small.

Note also that the VCR operating range  $(0 V_{DS} - V_{P})$  is typically wider than the saturation range of a BJT, so that a greater voltage margin is necessary to avoid distortion at low drain voltages.

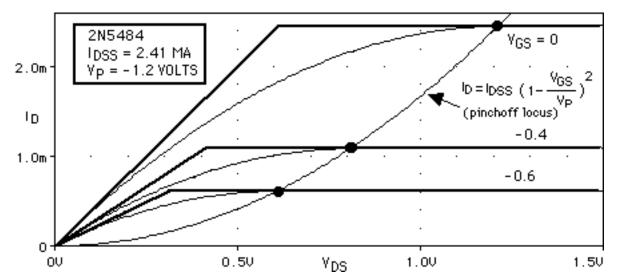

The 2N5484 drain characteristics are re-plotted once again, this time to emphasize the 'voltage-controlled resistance' range. The solid circles • in the figure below mark the intersection of the pinch-off locus with each characteristic (i.e., where  $V_{DS} = -V_P + V_{GS}$ ). The asymptotes for the  $V_{GS} = 0$  characteristic, for example, intersect at 0.6 volts, i.e., -V p/2, as expected theoretically. The actual current at this voltage is 1.8ma, i.e., 0.75 IDSS, also as expected theoretically.

Introductory Electronics Notes The University of Michigan-Dearborn

To obtain an <u>estimate</u> of the channel resistance in the VCR region (for small values of V<sub>DS</sub>) we can use the ratio of coordinates of the asymptote intercept point, i.e., the slope of the tangent at the origin.. For the VGS = 0 characteristic this estimate is  $(-V_P/2)/I_{DSS} = (1.21/2)/.00241 = 251$ ; the resistance increases for more negative gate voltages.

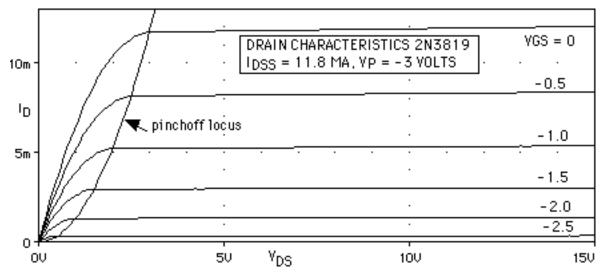

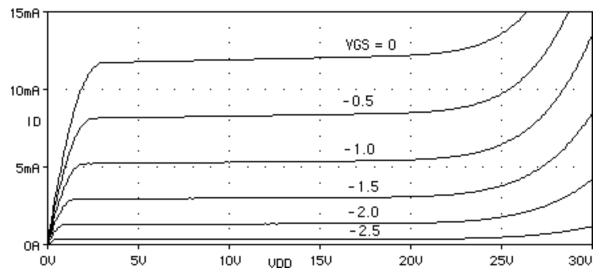

#### 2N3819 N-Channel JFET Characteristics (Another illustration)

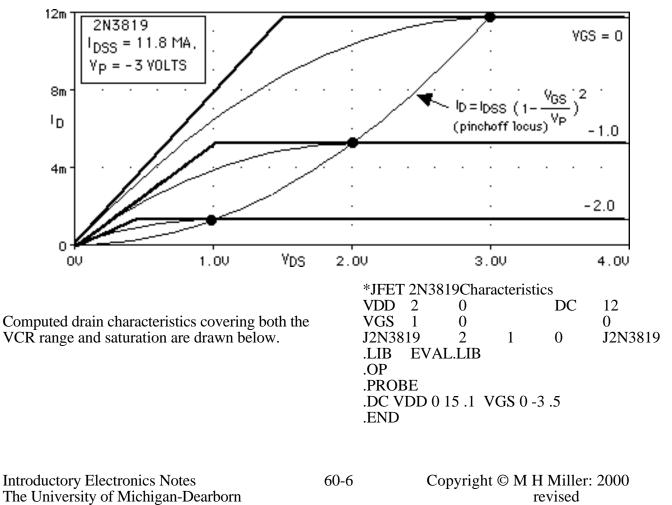

Drain characteristics emphasizing the 'voltage- controlled resistance' operating range of the 2N3918 JFET are plotted below. The circles identify the intersection of the pinch-off locus with each characteristic (i.e., where  $V_{DS} = -V_P + V_{GS}$ ). Estimate the channel resistance in the VCR region for  $V_{GS}=0$  as (3/2)/0.00118 = 1.27 K.

The drain characteristics are replotted below over a still larger range of drain-source voltage to show the inception of reverse-bias breakdown of the part of the gate junction near the drain for relatively large drain-source voltages.

# **JFET Amplifier**

We start with an examination of a more or less specific circuit to provide a broad background for a consideration of biasing. Some distinctions from the BJT case are underlined here to call special attention to them.

Consider the simplified N-channel JFET amplifier circuit drawn to the right. A voltage source in the base loop <u>reverse-biases</u> the gate junction, setting the gate-source voltage to a fixed value  $V_{GS}$  0. Provided the drain source voltage is large enough, and the voltage drop across the drain resistor is not too large, the JFET is in its normal saturated operating mode.

Introductory Electronics Notes The University of Michigan-Dearborn

| 60- | -7 |

|-----|----|

|     |    |

Copyright © M H Miller: 2000 revised

ΙD

VDS.

V<sub>DD</sub>

controlling the current the power provided by the battery and divided between the resistor and the transistor is controlled. (The power expended in the resistor should be interpreted as a general consumption of energy, for example by a loudspeaker or a small motor.)

The transistor provides the current-control capability by acting as a current valve; a change in gate voltage causes a corresponding drain current change. The change in power expended in the drain resistor can be considerably greater than the power needed to cause the change. Because the gate junction is (supposed to be) reverse-biased there is only a very small gate current. Moreover only a small gate-source voltage change is needed to change drain current significantly. The power that must be provided at the transistor gate to effect a power change in the collector loop is therefore the product of a quite small gate current and a small gate voltage change. On the other hand not only is the drain current much larger than the gate current but also the battery voltage ordinarily is much larger than the base voltage and can support larger voltage changes.

To solve for the loop current one could write in the usual manner a KVL loop equation  $V_{DS} = V_{DD} - I_D R_D$ , and substitute for  $V_{DS}$  from the volt-ampere relation of the transistor. It is convenient to illustrate the

solution graphically, particularly so because the transistor volt-ampere relation is nonlinear. Thus the transistor collector characteristics are plotted (sans numerical values for simplicity). and superimposed on the plot is a graph of the KVL loop equation. This latter equation plots as a line; a convenient way of doing this is by locating the axis intercepts as shown. Since the initial gate voltage is  $V_{GSO}$  the operating point (solution) must lie somewhere along the emphasized collector characteristic curve; in other words the transistor volt-ampere relationship must be satisfied. Concurrently the KVL expression must be satisfied; the operating point also must lie on the 'load' line. Therefore the operating point must be the intersection of the two curves, i.e., the point Q (for 'quiescent').

Suppose now the gate voltage is changed, say increased (i.e., made less negative) to  $V_{GS+}$ . There is a consequent increase in drain current, an increase in the voltage drop across the drain resistor, and a <u>decrease</u> in the drain-source voltage. Locating the new operating point graphically is a matter of moving 'up' the load line to the transistor characteristic identified by the gate voltage  $V_{GS+}$ .

#### **Biasing the JFET Amplifier**

The converse of analyzing a <u>specified</u> amplifier circuit to determine the quiescent point is 'biasing' the transistor, i.e., arranging for a specified quiescent point. There are two aspects to this synthesis: first deciding where the quiescent point is to be located, and then locating it there.

There is no unequivocal choice as to the proper quiescent point; it depends on what performance the amplifier is to provide. For example suppose the amplifier is to provide a symmetrical voltage swing about the Q point. For a maximum symmetrical swing the Q point should be located at roughly  $(V_{DD}-V_P)/2$ ; the (negative) pinch-off voltage provides an offset for the nonlinear VCR range. For a lesser amplitude swing the Q point might be located lower down on the load line; this would involve lower drain currents and therefore lowered requirements on the power supply.

For the present purpose we need not be overly concerned with a specific location of the Q point. Rather we concern ourselves here with just the means for establishing a given operating point, and not what the Q point values are. More than just this. Transistor parameters have significant uncertainties; parameters are quite temperature sensitive, and in addition have large manufacturing tolerances. Not only must a Introductory Electronics Notes 60-8 Copyright © M H Miller: 2000 The University of Michigan-Dearborn revised

specified Q point be <u>implemented</u> with uncertain circuit element parameters but also it must be <u>maintained</u> during environmental changes and despite device manufacturing tolerances.

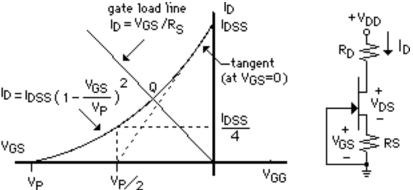

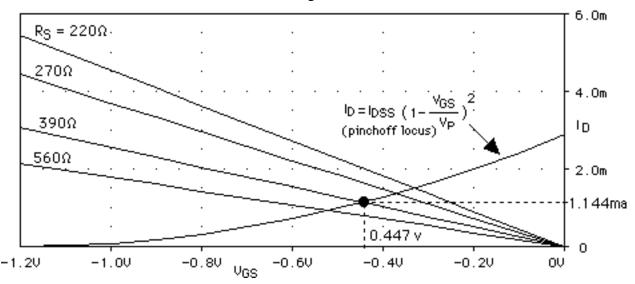

The theoretical relationship between the JFET drain current <u>in saturation</u>, neglecting the second-order slope of the characteristics, is a quadratic, shown below plotted on the ID-VGS plane. It is not difficult to verify that the tangent at  $V_{GS} = 0$  intercepts the abscissa at  $V_{P/2}$ ; the current for this gate voltage is IDSS/4. The asymptote and the VP intercept are helpful in sketching the quadratic.

The source resistor R accomplishes the biasing (within limitations to be discussed)S. Because of the negligible gate current the source and drain currents are essentially equal, and the voltage drop across the source resistor provides the reverse-bias for the gate. This gate 'load line' also is shown in the figure. The operating point is at the intercept Q. Note: Because the gate often serves as an input, for example

for an incremental signal, the short-circuit connection really is inappropriate. However the gate leakage current is quite small (about 1 nanoampere for the 2N5484) so that a rather large resistor can replace the short-circuit connection to provide an input resistance across which there is a negligible voltage drop due to the gate current.

A (rough) illustrative design using the 2N5484 JFET in the circuit described above follows; the common source characteristics (PSpice model) for the 2N5484 are reproduced below.

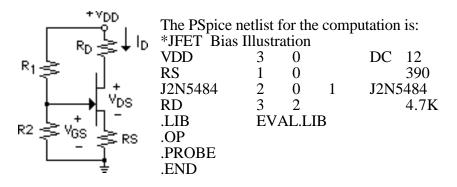

Suppose V<sub>DD</sub> is 12 volts. The pinch-off voltage for the JFET is V<sub>P</sub> = -1.2 volts , and to avoid low current nonlinearities near cutoff allow (say) a drain voltage maximum of 11 volts. Then for a symmetrical voltage swing over the remaining 9.8 volt range bias the JFET at about 1.2+(9.8/2) = 6.1 volts. From the characteristics we might chose a nominal middle' current of 1 ma, with the gate-source voltage needed being about -0.38 volts. This means we need a source resistance of 0.38/1 or 380 ; 390 is the closest 10% standard value. Finally to drop 4.9 volts with a drain current of 1 ma requires 4.9K; use R<sub>D</sub> = 4.7K

Recalculated values for the specified circuit parameters (substitute into and solve the quadratic expression using the <u>smaller</u> root (why?) are:  $I_D = 1.048$  ma, VGS = -0.408 volt, and VD = 7.074 volts. A PSpice computation (see netlist following) sets the operating point for the specified circuit parameters at  $I_D = 1.1$  ma,  $V_{GS} = -0.43$  volts, and  $V_D = 6.83$  volts.

Introductory Electronics Notes The University of Michigan-Dearborn

The biasing analysis may be computed by calculating the drain current (saturation) as a function of the gate-source voltage; the plot below is for  $V_{DS} = 12$  volts. Note that IDSS differs somewhat from the nominal value of 2.41 ma because of the channel length modulation.

#### **Biasing the JFET Better**

The preceding illustration may imply an impressive computational accuracy but it is not a overly practical calculation. In practice the transistor characteristics will be uncertain, particularly because of manufacturing tolerances. The figure to the right illustrates the problem this creates. Transistors manufactured to provide certain nominal characteristics ۱D. actually will show a spread of gate characteristics from DSS1 device to device roughly bounded as indicated. (Actually the characteristic with the most negative Vp does not DSS2 necessarily correspond to the characteristic with the largest IDSS. However it is conservative to presume this; the actual device characteristic then falls somewhere between the bounds. The difficulty, of course, is that except for the bounds the actual characteristic is not predictable.) ۷GS

The bias load line labeled 'A' corresponds to providing the bias with just a source resistor; the load line in this case

passes through the origin. Note that there is a difference in the drain current, depending on whether the device involved lies to one side or the other within the bounding gate characteristics. Note also that a load line such as 'B' has a smaller range of uncertainty; the gate-source bias then is  $V_{GG}$ -IDRS, where  $V_{GG}$  is the intercept on the abscissa. The larger  $V_{GG}$  the less the slope of the load line, and therefore the smaller the spread between the current intercepts on the bounding curves.

VP1

Introductory Electronics Notes The University of Michigan-Dearborn 60-10

Copyright © M H Miller: 2000 revised

VP2

VGG

A bias configuration to provide the VGG offset is shown to the left. The R1, R2 resistors form a voltage divider (the gate current is negligible if the resistors carry, say, a microampere or more of current) to bias the gate by  $V_{DD}(R_2/(R_1+R_2))$ ; this corresponds to VGG. Note the trade-off. VGG should be high to reduce the current intercept spread. But operation in saturation requires the drain voltage to exceed the gate voltage by at least the pinch-off voltage magnitude, and the gate bias should not force an excessive  $V_{DD}$  for a given drain voltage swing.

# **Better-Biasing Illustration**

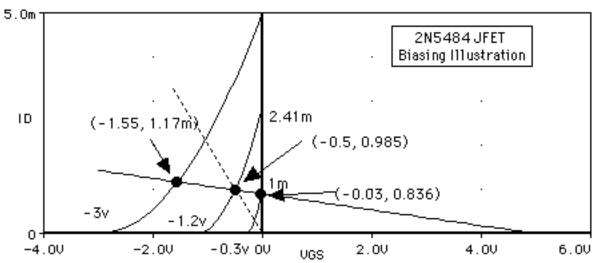

The manufacturer's data for the 2N5484 JFET indicates that the pinch-off voltage varies between -3 volts and -0.3 volts, and that IDSS varies between about 1ma and 5 ma. As noted before these data are interpreted conservatively by assuming that the extremes are correlated. Quadratic expressions using the respective pairs of parameters are plotted in the figure following as bounds on the actual gate characteristic. The nominal characteristic, computed from the PSpice model using Vp = -1.2 volts and IDSS = 2.41ma, also is plotted.

More or less arbitrarily, in lieu of an explicit specification, a nominal operating point is assumed at  $V_{GS} = -0.5$  volt (roughly centered). A load line with a 5 volt offset (again a more or less arbitrary choice) is drawn. The intercepts with the bounding curves as noted were determined (using the cursor capability of Probe). Note the comparatively modest range of current variation (0.836 ma to 1.17ma) for devices within the manufacturing tolerance limits. For comparison the load line for simple source biasing also is drawn (dotted); note the much larger range of current variation predicted.

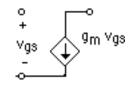

# JFET Incremental Parameter Equivalent Circuit

The formal development of an incremental parameter circuit for the JFET is essentially the same for the BJT. In both cases device characteristics in a small region about a DC operating point are approximated by tangent lines, and the topology of linear equivalent circuit representations is the same. There are, of course, significant differences in circuit element values for different devices.

A simplified incremental parameter circuit commonly used for JFET design calculations is as drawn to the right. For a JFET the input resistance is that of a reverse-biased junction diode, and is ordinarily so large compared to other circuit resistances in series with or shunting the gate-source terminals that it may be neglected.

In the saturation range of operation, and neglecting second order channel-length modulation

$$I_{D(max)} = I_{DSS} \left(1 - \frac{V_{GS}}{V_P}\right)^2$$

Introductory Electronics Notes The University of Michigan-Dearborn 60-11

Approximate this quadratic at a particular DC bias point by a tangent whose slope (the relation between an incremental change in gate-source voltage  $v_{gs}$  and an associated incremental change in drain current  $i_d$  is obtained by differentiating the quadratic:

$$i_d = 2 \frac{\sqrt{1DSS 1D}}{-Vp} v_{gs} \triangleq g_m v_{gs}$$

The coefficient  $g_m$  is the incremental transconductance of the JFET. Unlike the BJT the JFET is by its nature a (gate-source) voltage-controlled device. As noted above the incremental input resistance of the JFET corresponds to a reverse-biased diode, and except for very special cases the input current is negligible.

If the channel-length modulation is to be accounted for then a gate-drain resistor (not shown above) is added, i.e., the drain current includes a small dependence on the drain-source voltage. To account for this include the factor 1+ VDS factor in the expression for drain current, i.e.,

$$I_{D(max)} = I_{DSS} \left(1 - \frac{V_{GS}}{V_{P}}\right)^2 (1 + \lambda \nabla DS)$$

Calculate the incremental drain resistance

$$\frac{v_{ds}}{i_d} = \frac{1}{\lambda |_{\text{DSS}} (1 - \frac{V_{GS}}{V_{\text{P}}})^2} \le \frac{1}{\lambda |_{\text{DSS}}}$$

For the 2N5484 JFET for example IDSS = 2.41ma and 1/60; the minimum  $r_{ds}$  is 25K .) This is rarely important for preliminary design calculations for reasons similar to those applied to the BJT Early Effect. In general a JFET would be designed to transfer drain current into some sort of load and a comparatively low resistance load would be used. In any event initial design calculations would be adjusted by computer calculations using models which include various second order effects.

A more complete model accounts for small gate-drain and gate-source capacitances. However as for the BJT introduction of inherent reactive effects is postponed.

# **JFET Analog Switching Illustration**

Although generally less used for the purpose than other devices the JFET can approximate an analog switch, i.e., a two-state device which in one operating state is a short-circuit and in the other an opencircuit. Unlike the BJT, for example, JFET drain characteristics pass through the origin, so there is no inherent voltage 'offset' for a 'closed' switch.

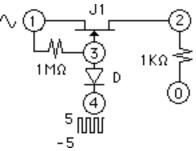

In the analog switch circuit drawn to the right a JFET is used, as an analog switch. J1 is a symmetrical N-channel transistor, i.e., the source and drain functions are interchangeable. Suppose that the diode D is reverse biased. Then if the voltage at node 1 is positive node 1 functions as the drain. The gate actually is forward-biased slightly, but because of the high resistance connection the gate current is limited. Because of the low channel resistance compared to load resistance the node 2 voltage essentially tracks the node 1 voltage.

Conversely if the node 1 voltage is negative node 2 acts as the drain. The gate is reverse biased but only slightly so because the leakage current is small. Again the low channel resistance means the node 2 voltage tracks the node 1 voltage.

The essential assumption made is that diode D is reverse biased. This is so if the gate control voltage is higher than the most positive signal voltage by a diode voltage drop or so. In the illustrative computation that follows the maximum signal voltage is 1 volt, while the control voltage to reverse bias the diode is 5 volts.

Introductory Electronics Notes The University of Michigan-Dearborn 60-12

Suppose now the control voltage applied is more negative than the most negative signal voltage. This assures that diode D will be forward biased. Moreover if this control voltage is less than the JFET pinchoff voltage the channel will be open and node 2 is effectively grounded.

A netlist for an illustrative switch circuit is shown to the left.

```

*JFET Chopper

VS

1

0

SIN(0, 1, 5K)

J1

2

3

J2N5484

1

3

RJ

1

1MEG

3

D1

4

D1N4148

2

RL

0

1K

VC8 4 0 PULSE(-5 5 0 1U 1U .4M 1M)

.LIB EVAL.LIB

.TRAN 1U 2.5M 0 1U

.PROBE

.END

```

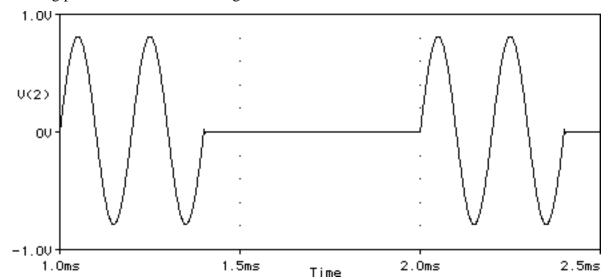

The following plot illustrates the switching action.

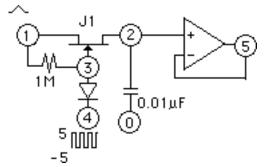

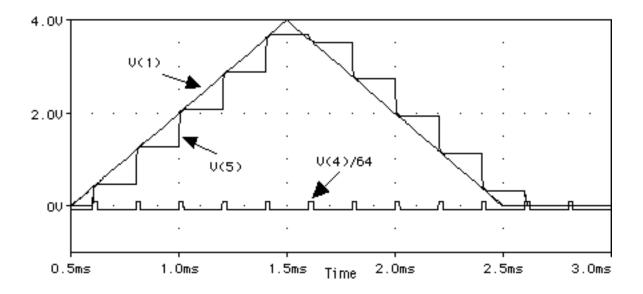

#### JFET Sample/Hold Switching Illustration

A simplified 'sample and hold' switching circuit is drawn to the right. A triangular waveform provides an illustrative input to an analog switch. When the switch is closed the input signal charges (or discharges) the capacitor through a lowresistance (i.e., small time constant) channel, and when the switch is opened the stored charge is retained for a period of time because of the high resistance discharge path in the closed condition. To illustrate the 'sample and hold' behavior a pulse train is applied to open and close the switch several times during the triangle period; the netlist following provides circuit details.)

| n 0) |

|------|

|      |

|      |

| 3    |

|      |

|      |

| VC8     | 4 0 PU | LSE(-5 | 501U | 1U .02M .2M) |

|---------|--------|--------|------|--------------|

| X1      | 2      | 5      | 675  | UA741        |

| V+      | 6      | 0      | DC   | 10           |

| V-      | 7      | 0      | DC   | -10          |

| .LIB EV | AL.LIE | 3      |      |              |

| .TRAN 1 |        |        |      |              |

| .PROBE  |        |        |      |              |

| .END    |        |        |      |              |

A plot of the output of the voltage follower follows. (The diode switching voltage is scaled to avoid clutter.) Note the capacitor charging/discharging during the small sampling interval (at the start of each step), and the very slight capacitor discharge during the 'hold' interval.

Introductory Electronics Notes The University of Michigan-Dearborn 60-13

# PROBLEMS

1) Compute the common source characteristics for the <u>P-channel</u> 2N 5460 JFET. A PSpice model for this device is given below ( $I_{DSS} = 1.9ma$ ,  $V_{P}=2.37$  v). Use the model and the circuit given to bias the JFET for a drain current of  $I_{DSS}/2$ .

.model J2N5460 PJF(Beta=334.7u Betatce=-.5 + Rd=1 Rs=1 Lambda=40m Vto=-2.37 + Vtotc=-2.5m Is=20p Cgd=6p M=.4582 Pb=1 + Fc=.5 Cgs=10.59p Kf=66.52E-18 Af=1)

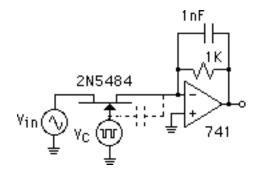

2) The <u>gate</u> of the 2N5484 JFET in the circuit shown is controlled by a square-wave whose period is 40 µseconds, and whose amplitude switches between -3 volts and 0 volts; this switches the JFET between 'full-on' and cutoff. The 'input' signal is a 3 volt sinusoid offset by 6 volts DC. Predict the voltage across the JFET and compare the prediction to a PSpice computation.

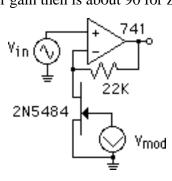

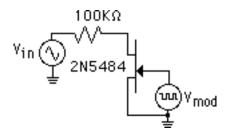

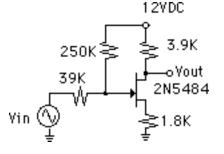

3) A JFET operating in the VCR range can be used as a gain control, as illustrated by the accompanying simplified circuit. The channel resistance for zero gate-source voltage is about (1.2/2)/2.41 250 . and increases as the gate is reverse-biased. The amplifier gain then is about 90 for zero gate

voltage, and decreases as the gate is reverse-biased. The gate control voltage used is a triangular (PWL) waveform varying linearly from 0 to -1.2 volts in 1.5 millisecond, and returning to 0 linearly at 3 milliseconds. Hence the amplifier gain should decrease during the first half-period, and increase in the second. To test this the transient response can be computed for an input 10 kHz sinusoid of amplitude 0.1 volt. Describe qualitatively the response to be expected, and then compute and compare the expected and computed response.

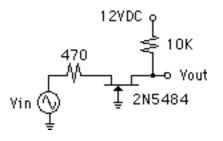

4) An incremental signal Vin is fed though a JFET used as an analog switch, i.e., the signal is passed to the opamp only when the switch enables this. Use a 10 millivolt, 10 kHz sinusoid for  $V_{in}$ , and for  $V_C$  use a square wave with a period of 4 millisecond switching between 0 and -2 volts. Describe operation of the switch in these circumstances. For example estimate the ON channel resistance to be about 250 , and therefore the amplifier voltage gain to be about -4. Why should  $V_{in}$  be 'small'? How would you decide what 'small' means quantitatively.

Perform a PSpice computation of the amplifier output waveform. Note that there is a parasitic capacitance between the gate and drain of the JFET which causes a switching 'spike' to appear at the amplifier input, i.e., the gate voltage switches faster than the gate-source capacitance can track. Filter this switching transient by adding a small capacitor (1 nF) across the 1K resistor.

Introductory Electronics Notes The University of Michigan-Dearborn

60-15

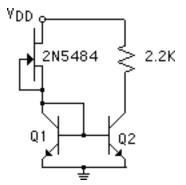

5) A JFET with its gate connected to the source provides a current-regulating action when operated in saturation. The circuit to the right uses a 2N5484 in this fashion to provide (to first order) a current equal to IDSS. However channel length modulation makes the current depend to an extent on the drain-source voltage. Compute the Q<sub>2</sub> current (both BJT are 2N3904) variation as VDD varies from 0 volts to 12 volts. Be sure to take account of the effect of BJT saturation and JFET cutoff.

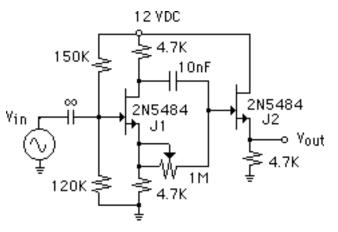

6) The current source of problem 4 is relatively constant for voltages above the pinchoff voltage (and below gate-drain breakdown). However channel length modulation introduces a slope to the drain characteristic, corresponding to a finite equivalent source resistance. The circuit shown to the left uses feedback to effectively increase this resistance. The drain characteristics on the right are used to illustrate the feedback action.

Drain characteristics for both J1 and J2 are sketched in the figure on the right Note that the drain-source voltage for J1 is V- VDS. This corresponds to a relocation of origin; the J1 drain characteristics emanate from the point V on the abscissa, and are drawn 'backwards'. The operating point must lie on the V<sub>GS</sub> = 0 curve for J2, and is at the intersection of that curve and the J1 curve whose reverse-bias is the drain-source voltage of J2. Since the two JFET currents are equal this forces J2 to operate in its VCR region (otherwise the zero-bias J1 current necessarily would be larger than the reverse-biased J2 current). The graph indicates (roughly, using 2N5484 FETs) that the J1 gate bias is about -0.4 volt. If V is increased the origin for the J2 curves moves to the right, and the slope of the characteristics would tend to increase the current at the intersection with the J1 curve. But the increased J2 gate reverse-bias moves the intersection to a lower characteristic. These two tendencies tend to balance and the JFET current stays fairly constant once J1 operates in saturation.

Compute the current for 0 V 12 volts. Also plot V<sub>DS</sub> over this range of variation.

7) Given the JFET circuit shown calculate the bias current and voltages first with channel-length modulation neglected and then estimate the influence of this effect. Compare with computed values. Nominal parameter values for the 2N3819 are IDSS = 11.6ma, Vp = -3v, and  $= .00225 v^{-1}$

Introductory Electronics Notes The University of Michigan-Dearborn 60-16

8) The JFET in the circuit shown has manufacturing tolerances such 15ma, and -5v Vp -2v. Bias the device so that that 10ma IDSS 8ma ID 6ma; neglect channel-length modulation. Compute bias currents and voltages for your calculated element values using the 2N3819 JFET (IDSS=11.6ma, Vp=-3v).

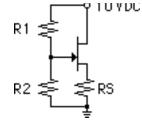

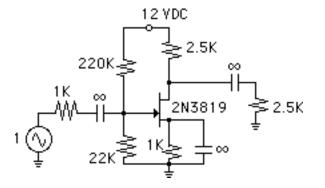

11) The biasing circuit of problem 6 is augmented as shown to form a 'Common Source' amplifier. Calculate the incremental voltage gain, and compare the calculated value with the computed value. Nominal parameter values for the 2N3819 are IDSS = 11.6ma, Vp = -3v, and  $= .00225 v^{-1}$ .

12) The phase-shift circuit shown to the right takes advantage of the JFET amplifier inversion to obtain copies of the input signal 180° apart. (The incremental voltage at node 3 is the negative of that at node 4, since the drain and source resistors carry the same incremental current.)

These two voltages then used to obtain a constant amplitude signal (at node 5) whose phase shift is - $\arctan(-2^* RC)$ , where R is the resistance between nodes 4 and 5, and C is the capacitance between nodes 3 and 5. The source follower unloads the amplifier to provide the output.

Verify the assertion made about the output.

Introductory Electronics Notes The University of Michigan-Dearborn

60-17

revised