# Flip flops and sequential circuits

Lecture 5 — § 1.6-1.7 **Computer Science 218**

Mike Feeley

### Overview

#### sequential circuits

- adding state to combinational circuits

- clocks

### flip-flops

- a state-holding component

- there are several of them: SR,D,JK and T

- excitation tables

### designing a sequential circuit

- state tables and diagrams

- some examples

2

### Flip flops

#### one-bit memory element

• latches input for one clock cycle

#### several types

# Building a flip flop

#### some initial attempts

- consider

- not good because x is unstable (i.e., x=x'

- a bit better

- y = x', x = y'

- possible states are xy=01 or 10

- can't set values

#### how about this?

- if S=0 and R=0

- -x=Q', Q=x'

- if S=1 and R=0

- -Q = (R+x)' = (R + (S+Q)')' = 1

- S→0, value is saved

- if S=0 and R=1

3

- Q = (R+x)' = (R + (S+Q)')' = 0

- R→0, value is saved

$Q = (1 + (1 + Q)^{2})^{2} = 0$ x = (1 + (1 + x)')' = 0

don't do this

### SR flip flop

#### characteristic table

| S | R | Q(t+1) |

|---|---|--------|

| 0 | 0 | Q(t)   |

| 0 | 1 | 0      |

| 1 | 0 | 1      |

| 1 | 1 | ?      |

$$S = set$$

$R = reset$

#### add a clock

- so we can ignore propagation delays

- but when C=1, have the same problem

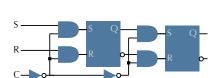

### master-slave SR flop flop

- solves problem

- when one FF is "pulsed" other is stable

- another approach in the

- clock-edge triggered

### Edge-triggered flip flops

### most common way to build synchronized flip-flop

- flip-flop latches on rising (falling) edge of clock

- rising edge is called positive, falling edge is called negative

- holds value until clock starts next rise (or fall for negative)

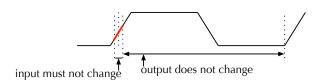

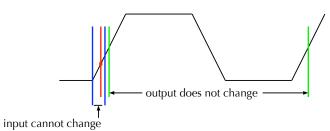

### how the flip flop latches

- setup time before transition when input cannot change

- threshold voltage transition

- hold time after transition when input cannot change

6

### Edge-triggered flip flops

#### key idea

- ensure stable FF output using narrow window to capture input

- most of the time output is saved FF state

- output=input only for narrow region on clock edge

### flip flop latching characteristic values

- threshold voltage

- voltage at which FF begins to produce new output

- setup time

- time before threshold voltage is reached when input cannot change

- allows input voltage to settle in FF

- hold time

- time after threshold voltage is reached when input cannot change

- ${\scriptscriptstyle -}$  allows input voltage to be reliably captured by FF

- propagational delay

- time after threshold voltage is reached that it takes FF to output a new value

- delay ≥ hold time

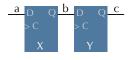

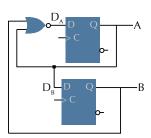

# How edge triggering works

#### exaggerated view of clock cycle

#### illustration of timing requirements

on each clock "pulse" (rising or falling edge):

- $\bullet \mathbb{C}_{i+1} = b_i$

- $\bullet b_{i+1} = a$

7

both flip flops are pulsed at once

• X's new output is delayed until after Y's hold time

### D flip flop

#### similar to SR

- D = S + R

- gets rid of S=1,R=1 undefined state

#### characteristic table

$$D = data$$

• Q(t+1) = D

#### to leave state unchanged

• don't pulse the clock

# T flip flop

#### characteristic table

$$T = toggle$$

•

$$Q(t+1) = Q(t) \oplus T$$

10

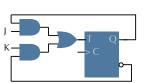

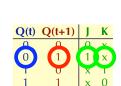

### JK flip flop

#### characteristic table

like SR, but with 11 defined

\_J Q \_\_ -> C -K 6-

### Flip flop excitation table

#### describes state transitions of flip-flop

• used when designing circuit using flip flops excitation tables for the flip flops we know

| Q(t) | Q(t+1) | S | R | Q(t) | Q(t+1) | D |

|------|--------|---|---|------|--------|---|

| 0    | 0      | 0 | Х | 0    | 0      | 0 |

| 0    | 1      | 1 | 0 | 0    | 1      | 1 |

| 1    | 0      | 0 | 1 | 1    | 0      | 0 |

| 1    | 1      | х | 0 | 1    | 1      | 1 |

| Q(t) | Q(t+1) | J | K | Q(t) | Q(t+1) | T |

|------|--------|---|---|------|--------|---|

| 0    | 0      | 0 | X | 0    | 0      | 0 |

| 0    | 1      | 1 | Χ | 0    | 1      | 1 |

| 1    | 0      | Х | 1 | 1    | 0      | 1 |

| 1    | 1      | Х | 0 | 1    | 1      | 0 |

most popular flip flop

### Sequential circuit behaviour

#### composed of

- combinational circuit

- just like before

- flip flops

#### inputs

• external inputs to combinational part

Understanding them

determine flip-flop input equations

- outputs of flip flops

- e.g., A

#### outputs

- external outputs

- outputs of flip flops

### flip flops

- inputs to flip flops

- e.g., D<sub>A</sub>

13

### Key idea

### sequential circuit is

- combination circuit plus memory (state)

- flip flops are its memory (one per bit)

- output is function of inputs + current state

### describe it using

- truth table, boolean functions or logic diagram

- for combinational part (truth table, boolean function, logic diagram)

- inputs are external inputs plus flop-flop outputs

- outputs are external outputs plus flip-flop inputs

- one boolean function for each output in terms of all inputs

- · finite state machine

- for sequential part

- finite state machine

- lists all possible states (memory settings)

- describes how current input and state determine external output and next state

14

u = g(a,b,c,d,e,f)

v = h(a,b,c,d,e,f)

w = i(a,b,c,d,e,f)

x = i(a,b,c,d,e,f)

y = k(a,b,c,d,e,f)

z = I(a,b,c,d,e,f)

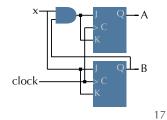

# Designing a sequential circuit

### example: a two-bit counter

- 1. draw a state diagram

- 2. draw excitation table

- · left hand columns

- all combinations of current state + input => next state

- right hand columns

- one flip flop for each state variable (e.g., A,B)

- column for each flip-flop input, from excitation table

| $\mathbf{Q}(\mathbf{t})$ |   | in | Q(t      | +1) | flip | -flop | inp | outs |

|--------------------------|---|----|----------|-----|------|-------|-----|------|

| Α                        | В | X  | Α        | В   | JA   | KA    | JB  | KB   |

| 0                        | 0 | 0  | 0        | 0   | 0    | X     | 0   | X    |

| 0                        | 0 | 1  | 0        | 1   | 0    | X     | 1   | X    |

| 0                        | 1 | 0  | 0        | 1   | 0    | X     | X   | 0    |

| 0                        | 1 | 1  | (1)      | 0   | 1    | x     | Х   | 1    |

|                          | 0 | 0  | <b>Y</b> | 0   | X    | U     | 0   | X    |

| 1                        | 0 | 1  | 1        | 1   | х    | 0     | 1   | X    |

| 1                        | 1 | 0  | 1        | 1   | х    | 0     | X   | 0    |

| 1                        | 1 | 1  | 0        | 0   | Х    | 1     | X   | 1    |

|                          |   |    |          |     |      |       |     |      |

combinational

circuit

# • $D_B = A$ create state table

•  $D_A = (A+B)^2$

| Q | (t) | Q(t+1) |   |  |  |  |

|---|-----|--------|---|--|--|--|

| Α | В   | Α      | В |  |  |  |

| 0 | 0   | 1      | 0 |  |  |  |

| 0 | 1   | 0      | 0 |  |  |  |

| 1 | 0   | 0      | 1 |  |  |  |

| 1 | 1   | 0      | 1 |  |  |  |

### draw state diagram

#### edges may be lablled a/b

- meaning that input a causes transition

- and output b is the result

# Designing a sequential circuit (II)

### 3. get boolean functions

- for

- flip-flop inputs and external outputs

- in terms of

- flip-flop outputs and external inputs

- using k-maps

| Bx JA                                        | $B_X$ $J_B$                   |

|----------------------------------------------|-------------------------------|

| A 00 01 11 10                                | A 00 01 11 10                 |

| 0 0 0 1 0                                    | 0 0 1 x x                     |

| 1 x x x x                                    | 1 0 1 x x                     |

| $J_A = Bx$                                   | $J_B = x$                     |

|                                              |                               |

| Bx KA                                        | ∖Bx K <sub>B</sub>            |

| <b>B</b> x <b>K</b> <sub>A</sub> 00 01 11 10 | Вх K <sub>в</sub> 00 01 11 10 |

| \DX                                          | \DX                           |

| A 00 01 11 10                                | A 00 01 11 10                 |

| Q(t) |   | in | Q(t | +1) | flip | -flop | inp | outs |

|------|---|----|-----|-----|------|-------|-----|------|

| Α    | В | X  | Α   | В   | JA   | KA    | JB  | KB   |

| 0    | 0 | 0  | 0   | 0   | 0    | Х     | 0   | Х    |

| 0    | 0 | 1  | 0   | 1   | 0    | X     | 1   | X    |

| 0    | 1 | 0  | 0   | 1   | 0    | X     | X   | 0    |

| 0    | 1 | 1  | 1   | 0   | 1    | X     | X   | 1    |

| 1    | 0 | 0  | 1   | 0   | x    | 0     | 0   | X    |

| 1    | 0 | 1  | 1   | 1   | x    | 0     | 1   | X    |

| 1    | 1 | 0  | 1   | 1   | x    | 0     | X   | 0    |

| 1    | 1 | 1  | 0   | 0   | x    | 1     | X   | 1    |

4. draw logic diagram