# AN-5067

Fairchild Semiconductor Application Note September 2005 Revised September 2005

# PCB Land Pattern Design and Surface Mount Guidelines for MLP Packages

## Introduction

The current miniaturization trend towards higher performance in smaller and lighter products has sped-up the evolution of packaging technology. Fairchild Semiconductor's Molded Leadless Package (MLP) has emerged as one of today's fastest growing packaging technologies due to a number of advantages over traditional leaded packages such as QFP or SO packages.

MLP advantages include:

- · Better board space utilization due to smaller footprint

- Smaller form factor, better electrical and thermal performance

- Reduced lead inductance

- Thinner profile and lighter weight components

## **MLP Package Construction Overview**

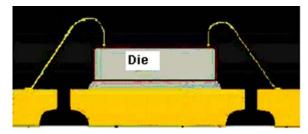

Figure 1 illustrates how the semiconductor is connected to the adjacent leads using wire bond. The construction of both wire bond pads and the die on the same plane of an MLP lead frame is key to achieving thin package profile.

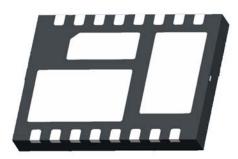

Figure 2 illustrates how increasing the flexibility in the external lead and DAP layout, within the same footprint, can optimize die size requirements---critical for multi-chip applications.

Fairchild's MLP has a Pb-free finish with pre-plated Nickel Palladium Gold (NiPdAu). The exposed die attach pad allows direct soldiering to the PCB for grounding and heat dissipation purposes. This means that more heat is dissipated from the package to the PCB, which improves thermal performance.

All MLP packages are molded in a 4x1 array lead frame and singulated via a sawing process. MLP Quad and Dual are compliant to JEDEC Outline MO-220 and JEDEC Outline MO-226, respectively.

FIGURE 1. Exposed Pad MLP Cross Section

FIGURE 2. Bottom View of a Triple DAP MLP Package

MicroPak™ is a trademark of Fairchild Semiconductor Corporation.

# **MLP Package Physical Characteristics**

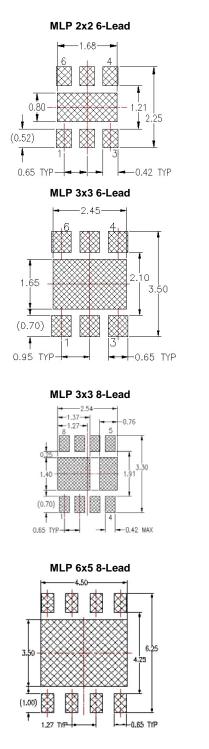

Typical package I/O pad dimensions are shown for reference only. Please refer to Fairchild's website for the latest package drawings.

Note: The shear strength values noted in Table 1 represent the minimum shear strength obtained using Fairchild MLP components vs. recommended land pattern. PCB substrate material deficiency, insufficient solder reflow, different chemistry or viscosity of solder paste flux matrix, solder void percentage, or different land pattern designs will produce different shear strength. Therefore, the values in this table should not be treated as industrial standards of minimum shear strength requirements for MLP packages.

| Size and Pin  | Pad Pitch | tch Pad Width | Pad Length | Component Shear Strength<br>(N) |         |

|---------------|-----------|---------------|------------|---------------------------------|---------|

| Count         | nom. (mm) | nom. (mm)     | nom. (mm)  | SnPp                            | Pb-Free |

| 2 X 2 6-Lead  | 0.95      | 0.30          | 0.32       | >50                             | >50     |

| 3 X 3 6-Lead  | 0.95      | 0.40          | 0.45       | >100                            | >100    |

| 3 X 3 8-Lead  | 0.65      | 0.30          | 0.50       | >100                            | >100    |

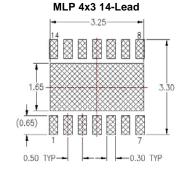

| 4 X 3 14-Lead | 0.50      | 0.25          | 0.48       | >80                             | >80     |

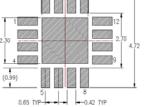

| 4 X 4 16-Lead | 0.65      | 0.33          | 0.55       | >160                            | >160    |

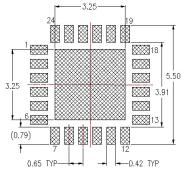

| 5 X 5 24-Lead | 0.65      | 0.30          | 0.45       | >200                            | >200    |

| 6 X 5 8-Lead  | 1.27      | 0.45          | 0.75       | >180                            | >180    |

| 5 X 6 16-Lead | 0.65      | 0.32          | 0.42       | >200                            | >200    |

# **Qualified by Extension**

Since the Printed Circuit Board (PCB) level qualification data shown in Table is representative of the entire population of Fairchild's MLP packages (see Appendix 1), not every MLP was tested. Customers can expect the same performance as shown in this application note from any Fairchild part in an MLP package with pitches from 0.5 to 1.27, thickness from 0.7 to 1.1, and sizes that are from 2X2mm to 5X6mm.

# **PCB Design Considerations**

IPC-SM-782 was used as the industrial standard for land pattern design. Fairchild, however, recommends using this application note as a guide for MLP land pattern design for Fairchild MLP parts, in conjunction with the broader MLP guidelines specified in IPC-SM-782.

#### Solder Mask Guideline

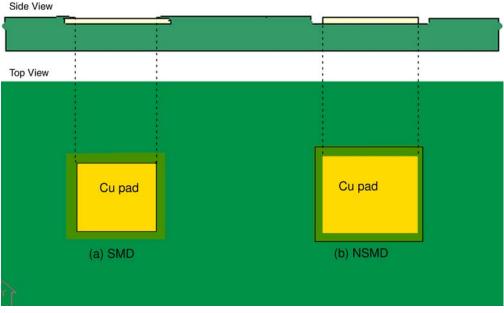

Generally there are two types of PCB configurations for surface mount leadless MLP type packages. These configurations are shown in Figure 3.

- Solder Mask Defined (SMD) Solder mask over the edge of mounting pads. Typically, there is an overlay of 0.050mm between the solder mask and the SMD Cu pads.

- Non-Solder Mask Defined (NSMD) Solder mask larger than mounting pads or pulled away from the solderable mounting pads. Typically, the solder mask should be 0.125mm ~ 0.150mm larger than the pad size, and around 0.060mm ~ 0.075mm clearance between the Cu pads and solder mask on all sides.

For lead pitch 0.65mm and above, the solder mask can be designed around each individual lead finger. NSMD mounting pads have advantages over SMD mounting pads as the NSMD improve the solder joint reliability by having solder flow around both the top and side of the mounting pads. SMD pads will inherently create a concentrated stress point where the solder wets to the pad on top of the lead.

FIGURE 3. Solder Mask Defined Pad (a), and Non-Solder Mask Defined Pad (b)

#### PCB Surface Finishes

There are a variety of PCB surface finishes. The following factors must be considered when selecting the proper PCB surface finish:

- 1. The finish should be flat and uniform (planar) to allow good lead connection and uniform component placement.

- 2. The finish should be economically favorable. It should be comparable to the standard pricing currently used with Hot Air Solder Level (HASL).

- 3. The finish should promote good solderability. The assembly process should be as easy as the process for a HASL and it should have good solder joint reliability.

Since the MLP is a thin profile leadless package, it is imperative that the plating is uniform, conforming and free of impurities to insure a consistent solderable system. Irregular PCB land surface can reduce the overall surface mount yields. For this reason, Electroless Nickel Immersion Gold (ENIG) and Organic Solderability Preservation (OSP) coating over copper pad are more desirable than a Hot Air Solder Level (HASL) surface finish.

An HASL surface finish has an inherent non-coplanar surface with typical surface thicknesses ranging from 50 to 1000 micro inches and 0.5 to 1 mil in the hole. Moreover, HASL contains lead which is not acceptable in Pb-free manufacturing.

#### Land Pattern Design

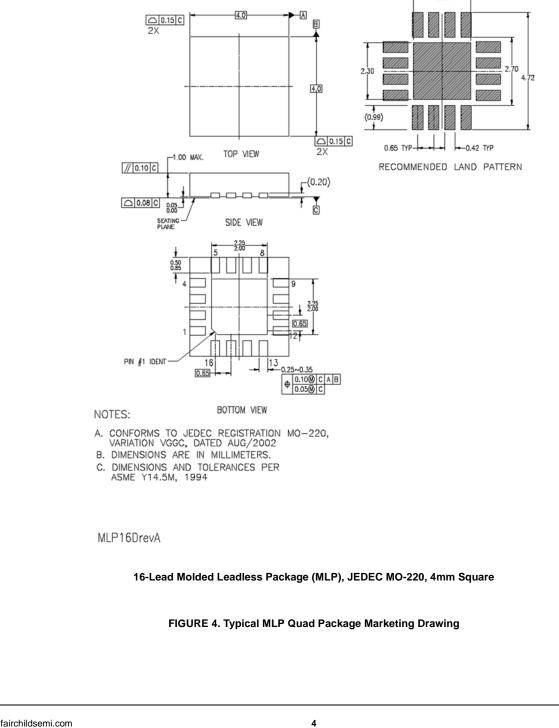

Figure 4 shows a typical MLP-Quad package drawing. The dimensions of the recommended land pattern are specified in the drawing.

Note: The information in this application note should only be used as a guideline. Please refer to the package drawings in the datasheet for a particular Fairchild part for the latest information.

In general, the land pattern dimensions should match those of the pads on the package. PCB terminal pads should be designed 0.2mm ~ 0.5mm away from the package center to

obtain a good solder fillet. Additionally, the pads should be extended 0.03mm ~ 0.05mm toward the center line of the package. The pad width should extend at least 0.02mm beyond each side of the package. However, Fairchild recommends that the maximum width of the component terminal for lead pitch not exceed 0.5mm to avoid solder bridging.

Other factors, such as end-user layout and design, product specific application, and actual experience must be taken into consideration to define the final PBC design for optimum component mounting process.

# AN-5067

AN-5067

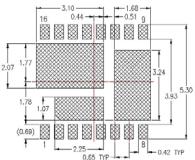

Figure 5 shows some suggested MLP land pattern designs as per standard drawings. Please refer to the Fairchild website for the latest drawings. The land patterns shown here should only

be used as a reference when designing a stencil aperture opening for individual package types.

MLP 5x5 24-Lead

FIGURE 5. Suggested MLP Land Pattern Designs as per Standard Marketing Drawings

#### **Thermal Via Design**

In order to effectively transfer heat from the top metal layer of the PCB to the backside of the board and heat sink, thermal vias need to be incorporated into the thermal pad design. A grid of 1.2mm pitch thermal vias, dropped down and connected to buried copper plane(s) should be placed under the thermal land.

Fairchild does not recommend using an exposed thermal via on solderable areas/thermal pad since solder will be pulled away from the thermal pad (solder wicking) during solder reflow process. This may result in the formation of undesirable and possibly detrimental solder voids.

To minimize/avoid wicking, thermal vias should be plugged by tenting the via during the solder mask process. The via solder mask diameter should be  $100\mu$ m larger than the via hole diameter. A finished via of 0.25mm ~ 0.30mm diameter is recommended. Another way to prevent solder from being pulled away from the thermal pad is to bury the vias.

The minimum thermal requirement for heat sinking should be determined during the board development stage. The thermal performance requirements vary from one application to another. Actual evaluations and appropriate reliability tests must be done to verify performance.

## **MLP Board Mounting Guidelines**

The following sections give general recommendations for mounting exposed pad MLP packages on the board. Fairchild recommends the use of low residue, non-clean type 3 or type 4 solder paste during the board mounting process. Non-clean paste is preferred over clean paste due to:

- 1. Elimination of solvent and aqueous cleaning.

- 2. Environmental concerns on solvent cleaning process.

- 3. No post reflow cleaning required.

- 4. Performance close to rosin based.

- 5. Reduced flux activity/reactivity after reflow.

However, water-soluble clean pastes can be used as well. Both Sn63Pb37 and Pb-free paste will give good solderability results.

#### Stencil Design

An electro-polished laser cut stencil with a thickness of 5 mils is recommended for these specific MLP packages. Typically, solder joint thickness/standoff height for MLP leads should be 0.05mm ~ 0.075mm. For maximum thermal and electrical performance, the exposed pad on the package must be soldered on the PCB. The large differential area between the large exposed pad and the small lead of the MLP can present a challenge in producing an even solder thickness. The use of a metal squeegee is recommended for a uniform pressure printing process, thus avoiding the paste from scooping-out from the large exposed pad apertures.

Unlike their rubber counterparts, metal squeegees do not wear easily and do not need to be sharpened.

For exposed pad size more than 25mm<sup>2</sup>, an array pattern of stencil aperture openings which will normalize the standoff height for the expose pad is recommended.

The stencil's area of aperture opening to aperture wall area ratio is critical for the release of the printed solder paste and is dependent on the aperture dimension.

For very small aperture where the area ratio is less than 0.66, the stencil must be nickel-formed which will provide superior paste release characteristics.

Area Ratio/Surface Tension Ratio = Area of Aperture Opening

Aperture Wall Area

The aspect ratio relates to the manufacture of stencil and it should be greater than 1.5. Reference IPC-7525: Stencil Design Guidelines.

Aspect Ratio = Aperture Width / Stencil Thickness

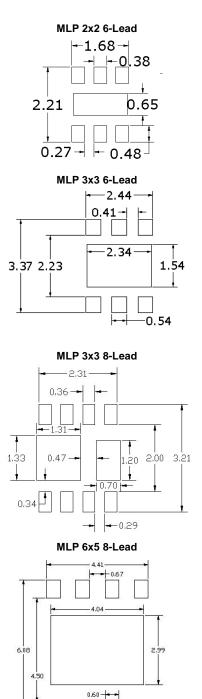

Figure 6 shows some suggested screen printing patterns. Please note that the stencil design shown below is applicable

for the land pattern shown in Figure 5. Stencil designs should be reviewed for any land pattern change.

#### Assembly Process Flow

AN-5067

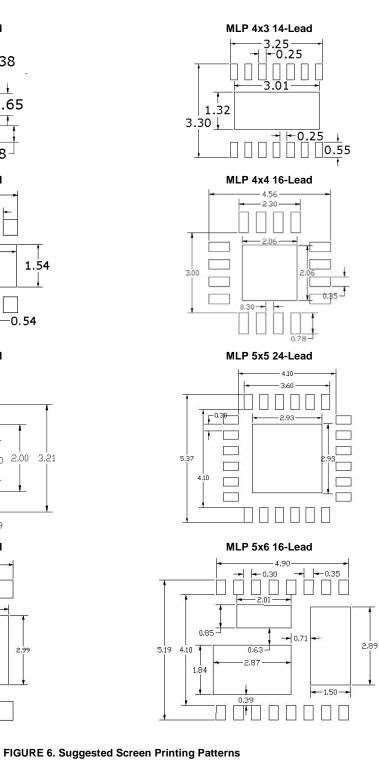

Figure 7 shows a recommended board mounting assembly process flow.

FIGURE 7. Recommended Board Mounting Assembly Process Flow

#### Solder Reflow

The NiPdAu finish is compatible with SnPb and Pb-free pastes. Once the solder paste is printed, the MLP component should be placed and convection/IR reflowed within 4 hours. A nitrogen (N2) reflow environment is desirable as it will improve wetting and higher surface tension which promotes "component self alignment".

Solder reflow in air is not ideal since the environment allows the formation of oxides which may impact the component's solderability. Nevertheless, both reflow atmosphere in N2 and air is acceptable as Fairchild Semiconductor's board level qualification includes board level reliability data per IPC9701 (Performance Test Methods and Qualification Requirements for Surface Mount Solder Attachments), IPC-SM-785 (Guidelines for Accelerated Reliability Testing of Surface Mount Solder Attachment) and JEDEC JESD22-B103-B (Vibration, Variable Frequency test) for vibration test. For solder void acceptance criteria, Fairchild has done internal accelerated reliability tests as per IPC-SM-785 and results showed that voiding with the MLP package/lead to board interconnection for up to 25% will not cause any solder joint reliability issues after 1000 cycles. However, it is recommended that the customer determines the acceptable solder void percent during the board level development which may vary according to individual customer requirements.

A typical reflow profile composed of four distinct sections:

- Preheat Zone: PCB assembly preheated at a rate < 4°C per sec., to start the solvent evaporation and to avoid thermal shock.

- 2. Soaking Zone: Thermal soak zone to remove solder paste violates and for activation of flux.

- 3. Reflow Zone: Zone where temperature above liquidus of the solder alloy.

- 4. Cooling Zone: Maximum 6°C/sec.

Figure 8 is an example of a standard reflow profile. The actual profile parameters depend on the solder paste used and the

recommendations from paste suppliers where the chemistry and viscosity of the flux matrix can vary.

182.70 Left Cur 28.0 TC #3 182.70 Right Cu Delta Rate: 128.9 32.4 Temp: Time: Temp: 182.6 Temp: 53.7 Low Temp: 3.58 1.67 Time: Time: 1.92 High Temp: Critical temperature: 183.0 Time above critical 1.16 one 3 Entrance one ' one 2 230.00 218.50 207.00 195.50 195.50 184.00 172.50 161.00 149.50 138.00 126.55 115.00 103.50 92.00 80.50 69.00 57.550 46.00 34.50 23.00 Preheat Up emperature, degrees Cooling Zone Zone Soaking Reflow Zone Zone 11.50 0.00 0.00 0.35 0.70 1.05 1.40 1.75 2.10 2.45 2.80 3.15 3.50 3.85 4.20 4.55 4.90 5.25 5.60 5.95 6.30 6.65 7.00 FIGURE 8. Typical Sn63Pb37 Reflow Profile

#### **TABLE 2. General Solder Reflow Requirement**

|                     | Sn63Pb37       | Pb-Free              |

|---------------------|----------------|----------------------|

| Ramp Rate           | < 4°C/sec. Max | < 4°C/sec. Max       |

| Soaking             | 135°C to 165°C | 150°C to 180°C       |

|                     | 60 to 120 sec. | 60 to 120 sec.       |

| Time above liquidus | 183°C          | 220°C                |

|                     | 30 ~ 90 sec.   | 30 ~ 90 sec.         |

| Peak Temperature    | 215 ± 5'C      | $245\pm\mathbf{5'C}$ |

| Cooling Rate        | 6°C/sec. Max   | 6°C/sec. Max         |

#### **Final Solder Inspection**

Unlike peripherally-leaded packages, the solder joint of an MLP is difficult to visually inspect to determine solder joint quality. Only the outer row lead can be visually inspected, depending on the proximity and location of the adjacent components.

MLP solder joints can be inspected with an x-ray system to detect defects such as bridging, or solder void. The open joint can be inspected by rotating the package on its side to inspect the side of the solder joints and using an x-ray system or high magnification scope to check for solder joint cracks.

www.fairchildsemi.com

## **Rework Process**

Since MLPs are leadless packages, the rework process is very similar to the BGA rework process. The entire package must be removed from the PCB if solder joint problems are detected.

The rework process of exposed-pad MLP is comprised of the following steps:

- 1. Removal of defective/old component.

- 2. Solder dressing and cleaning.

- 3. Manual solder paste printing.

- 4. Re-attach new component and reflow.

A special nozzle should be used to locally heat the part. To avoid heating the adjacent components, high temperature tape should be used to cover the adjacent area before undergoing the local heating process. The bottom of the PCB should be heated using a convective preheater. The reflow profile should be the same as the profile used for mounting the parts.

The reflow period can be shortened by using an automated vacuum pick-up head to lift the part off during the transition from reflow to cool down cycles. Once the part is removed, clean the pads on the PCB with a blade-style solder iron tip and solder wick. Use an appropriate solvent, such as IPA, to clean the remaining residue and flux.

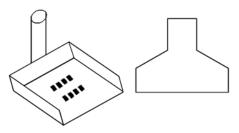

For MLP 3x3 and above body sizes, use a special mini stencil to print the solder paste on the PCB pads. The mini stencil must be aligned properly before the manual printing process. Use a mini squeegee to manually print solder paste on the pad. Due to the small pad configurations of the MLP and the fact that the pad is located on the underside of the package, it is not advisable to manually place the package without the aid of magnification. Use a Vision Overlay System (VOS) to ensure proper alignment during component placement to the PCB. For MLP 2x2 and below body sizes, it is difficult to perform a manual solder paste printing using a mini stencil and a mini squeegee. Typically, a dispenser system can be used to aid the process.

A VOS typically consists of a prism to collect two images, one from above and one from below. The images are projected onto a series of mirrors and reflected to the camera lens where they are displayed on a video monitor as two separate overlaid images. The component or the board is repositioned until the component lead and land array pattern match exactly.

The reflow process can be accomplished by passing the board through the original reflow oven or by selectively heating the MLP package.

FIGURE 9. Manual Solder Printing Stencil and Mini Squeegee

## References

Technical Journal - Surface Finish Options; May 2002, The Newsletter of PWB Technologies

IPC-SM-785: Guidelines for Accelerated Reliability Testing of Surface Mount Solder Attachments

IPC-9701: Performance Test Models and Qualification Requirements for Surface Mount Solder Attachments

JEDEC JESD22-B103-B: Vibration, Variable Frequency

IPC-7525: Stencil Design Guidelines

Fairchild Semiconductor MLP Package Outline Drawings

AN-5067

### Appendix I

Depopulated Quad Very-Thin Flat Pack No Leads (DQFN) Molded Leadless Package (MLP)

#### **Package Description** Marketing Outline Drawing 6LD, MLP, DUAL, NON-JEDEC, MicroPak™ MAC06A MLP06A 6LD, MLP, JEDEC MO-229, DUAL, 3mm SQUARE 6LD, MLP, DUAL, JEDEC MO-229, 2mm SQUARE MLP06B 6LD, MLP DUAL, JEDEC MO-229, 3mm X 2mm MLP06C 6LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE MLP06D 6LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE MLP06E 6LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE, EXTENDED DAP MLP06F 6LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE MLP06G 6LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE, DUAL DAP MLP06H 6LD, MLP, DUAL, NON-JEDEC, 2mm X 5mm MLP06I 6LD, MLP, DUAL, NON-JEDEC, 2mm SQUARE, DUAL DAP MLP06J 6LD, MLP, DUAL, JEDEC MO-229, 2mm SQUARE MLP06K 6LD, MLP, DUAL, NON-JEDEC, 2mm SQUARE, SINGLE TIED DAP MLP06L 8LD, MLP, DUAL, NON-JEDEC, 5mm X 6mm MLP08A 8LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE MLP08B 8LD, MLP DUAL, JEDEC MO-229, 2mm SQUARE MLP08C 8LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE MLP08D MLP08E 8LD, MLP, JEDEC, MO-229, DUAL, 3mm SQUARE, DUAL DAP 8LD, MLP, DUAL, JEDEC MO-229, 3mm SQUARE MLP08F 8LD, MLP, DUAL, NON-JEDEC, 5mm X 6mm, SINGLE TIED DAP MLP08G 8LD, MLP, DUAL, NON-JEDEC, 3mm X 1.9mm, DUAL TIED DAP MLP08H 8LD, MLP, DUAL, NON-JEDEC, 3mm X 1.9mm, SINGLE TIED DAP MLP08I 10LD, MLP, JEDEC MO-220, DUAL, 3mm SQUARE MLP10A 10LD, MLP, DUAL, JEDEC M0-229, 3mm SQUARE MLP10B MLP12A 12LD, MLP DUAL, JEDEC MO-229, 4mm X 3mm 12LD, MLP, QUAD, JEDEC MO-220, 4mm SQUARE DUAL DIE MLP12B 12LD, MLP, QUAD, JEDEC MO-220, 4mm SQUARE MLP12C 14LD, DQFN, JEDEC MO-241, 2.mm X 3.0mm MLP14A 14LD, MLP, DUAL, JEDEC M0-229, 4mm X 3mm MLP14B 14LD, MLP, DUAL, JEDEC MO-229, 4mm SQUARE MLP14C 14LD, MLP, 2.5mm SQUARE MLP14D 16LD, MLP, QUAD, JEDEC MO-220, 4mm SQUARE MLP16A 16LD, MLP, QUAD, JEDEC MO-220, 3mm SQUARE MLP16B 16LD, MLP, JEDEC MO-220, 3mm SQUARE MLP16C 16LD, MLP, QUAD, JEDEC MO-220, 4mm SQUARE MLP16D 16LD, DQFN, JEDEC MO-241, 2.5mm X 3.5mm MLP16E 16LD, MLP, JEDEC MO-220, DUAL, 5mm X 6mm, TRIPLE DAP MLP16F MLP16G 16LD, MLP, QUAD, JEDEC MO-220, 4mm SQUARE 16LD, MLP, QUAD, MO-217 EQUIVALENT, 3mm SQUARE PHILLIPS BCC16 MLP16HB 18LD, MLP, DISD MODULE, TRIPLE DAP, 8mm X 12mm MLP18A

| Package Description                                           | Marketing Outline Drawing |

|---------------------------------------------------------------|---------------------------|

| 20LD, MLP, QUAD, JEDEC MO-220, 5mm SQUARE                     | MLP20A                    |

| 20LD, DQFN, JEDEC MO-241, 2.5mm X 4.5mm                       | MLP20B                    |

| 20LD, MLP, JEDEC MO220, 3mm X 4mm BODY                        | MLP20C                    |

| 24LD, MLP, QUAD, JEDEC MO-220, 5mm SQUARE                     | MLP24A                    |

| 24LD, MLP, QUAD, JEDEC MO-220, 3.5mm X 4.5mm                  | MLP24B                    |

| 24LD, MLP, QUAD, CUSTOM, 5mm SQUARE, DUAL DAP                 | MLP24C                    |

| 24LD, MLP, QUAD, JEDEC MO-220, 4mm SQUARE                     | MLP24D                    |

| 32LD, MLP, QUAD, JEDEC MO-220, 5mm SQUARE                     | MLP32A                    |

| 40LD, MLP, QUAD, JEDEC MO-220, 6mm SQUARE                     | MLP40A                    |

| 48LD, MLP, QUAD, JEDEC MO-220, 7mm SQUARE                     | MLP48A                    |

| 56LD, MLP, QUAD, NON-JEDEC, 5mm X 7mm, DUAL ROW               | MLP56A                    |

| 64LD, MLP, QUAD, JEDEC MO-220, 9mm SQUARE, FUSED 1, 2, 47, 48 | MLP64A                    |

| 64LD, MLP, QUAD, JEDEC MO-220, 9mm SQUARE                     | MLP64B                    |

|                                                               |                           |

## DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION

#### As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.