# **Application Note AN6016**

# LCD Backlight Inverter Drive IC (FAN7311)

# 1. Description

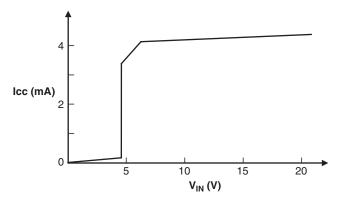

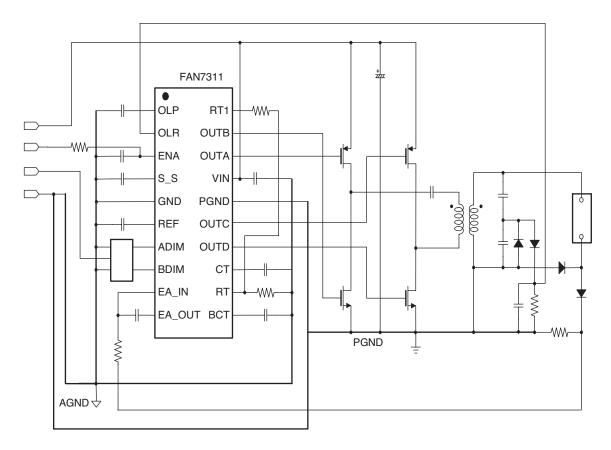

Design goals for a Cold Cathode Fluorescent Lamp (CCFL) inverter for use in a notebook computer or other portable applications include small size, high efficiency, and low cost. The FAN7311 provides the necessary circuit blocks to implement a highly efficient CCFL backlight power supply in 20-SSOP and 20-SOIC packages. The FAN7311 typically consumes less than 4mA of operating current, improving overall system efficiency. External parts count is minimized and system cost is reduced by the integration of features including; feedback-controlled Pulse Width Modulation

(PWM) driver stage, soft start, open lamp regulation, and Under Voltage Lockout protection (UVLO). The FAN7311 includes an internal shunt regulator that allows operation with an input voltage from 5V to 25.5V. It supports analog and burst dimming modes of operation. The FAN7311 provides open lamp regulation and protection. Open lamp regulation protects the transformer from over-voltage during start up or when an open lamp occurs. The transformer voltage is regulated by reducing duty cycle when an over-voltage is detected. Open lamp protection can be used to shut down an IC when an open lamp condition continues longer than a specified time.

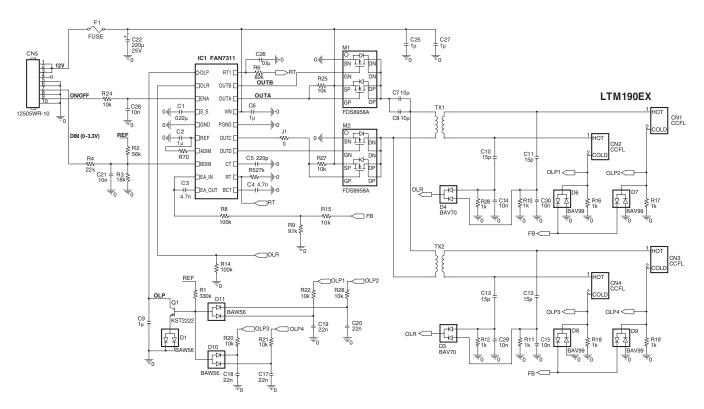

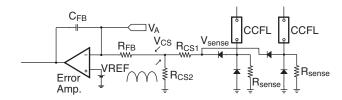

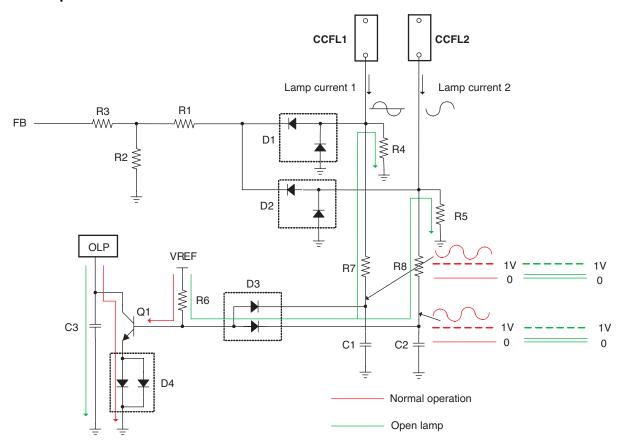

**Figure 1. Application Circuit**

# 2. Block Diagram and Basic Operation

# 2.1 Block Diagram

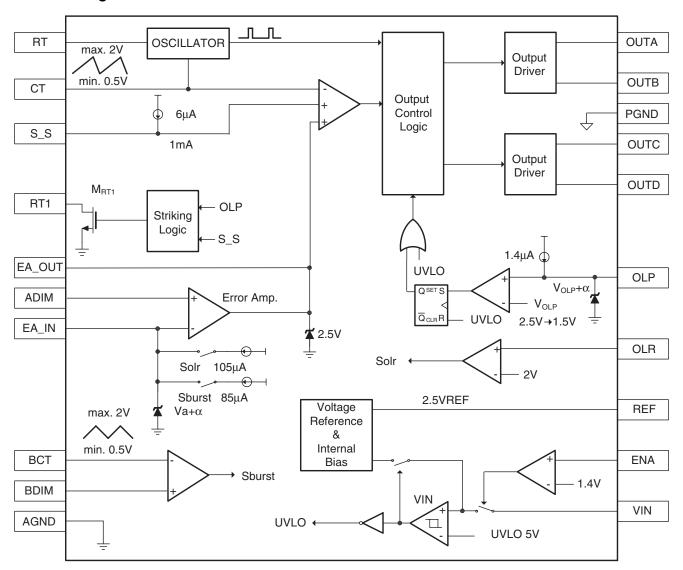

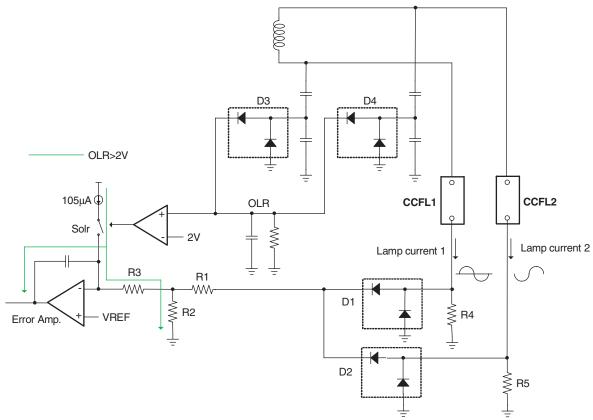

Figure 2. Block Diagram

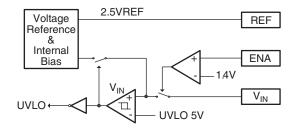

## 2.2 Under Voltage Lockout (UVLO)

The UVLO circuit guarantees stable operation of the IC's control circuit by stopping and starting it as a function of the  $V_{IN}$  value. The UVLO circuit turns on the control circuit when  $V_{IN}$  exceeds 5V. When  $V_{IN}$  is lower than 5V, the IC's standby current is less than  $200\mu A$ .

#### **2.3 ENA**

Applying voltage higher than 2V to ENA pin enables the operation of the IC. Applying voltage lower than 0.7V to ENA pin disables the operation of the inverter.

Figure 3. Under Voltage Lockout and ENA Circuits

Figure 4. Start Voltage and Operating Current

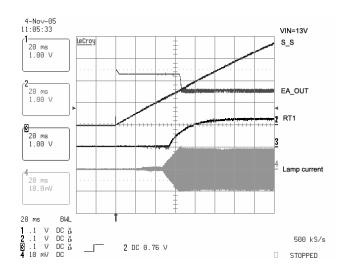

#### 2.4 Soft Start

The soft-start function is provided by the  $S_S$  pin and is connected through a capacitor to GND. A soft-start circuit ensures a gradual increase in the input and output power. The capacitor connected to  $S_S$  pin determines the rise rate of the duty ratio. It is charged by a current source of  $6\mu A$ .

Figure 5. Soft Start During Initial Operation

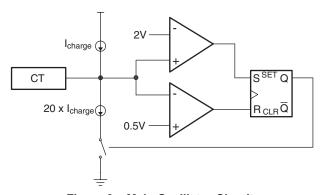

#### 2.5 Oscillator

#### 2.5.1 Main Oscillator

Timing capacitor  $C_T$  is charged by the reference current source. The source is formed by the timing resistor  $R_T$  whose voltage is regulated at 1.25V. The sawtooth waveform of the main oscillator circuit charges up to 2V, then the capacitor begins discharging down to 0.5V. The capacitor starts charging again and a new switching cycle begins.

$$I_{\text{charge}} = \frac{3}{4} \frac{1.25}{R_T}$$

(2.1)

The main frequency can be programmed by adjusting the values of  $R_T$  and  $C_T$ . The main frequency can be calculated as shown below.

$$f_{\rm op} = \frac{19}{32 R_{\rm T} C_{\rm T}} \tag{2.2}$$

Figure 6a. Main Oscillator Circuit

Figure 6b. Main Oscillator Waveform

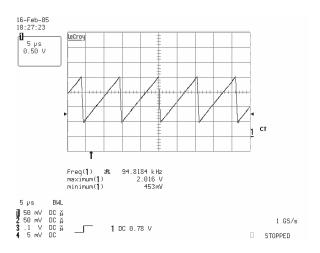

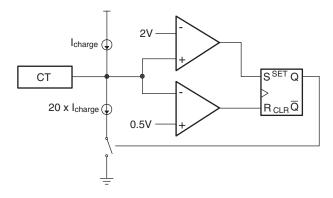

#### 2.5.2 Burst Dimming Oscillator

Burst dimming timing capacitor  $BC_T$  is charged by the reference current source, formed by the timing resistor  $R_T$  whose voltage is regulated at 1.25V. The sawtooth waveform charges up to 2V. Once reached, the capacitor begins discharging down to 0.5V, then starts charging again and a new switching cycle begins.

$$I_{\text{charge}} = \frac{3}{32} \frac{1.25}{R_T}$$

(2.3)

The burst dimming frequency can be programmed by adjusting the values of  $R_T$  and  $BC_T$ . The burst dimming frequency can be calculated as below.

$$f_{burst} = \frac{3.75}{96 R_T B C_T}$$

(2.4)

The burst dimming frequency should be greater than 120Hz to avoid visible flicker. To compare the input of BDIM pin with the  $0.5{\sim}2V$  triangular wave of burst oscillator makes the PWM pulse for burst dimming. The PWM pulse controls EA\_OUT voltage by summing  $85\mu A$  into the EA\_IN pin. Figure 7 shows burst dimming oscillator circuit and waveform.

Figure 7a. Burst Oscillator Circuit

Figure 7b. Burst Oscillator Waveform

## 2.6 Analog Dimming

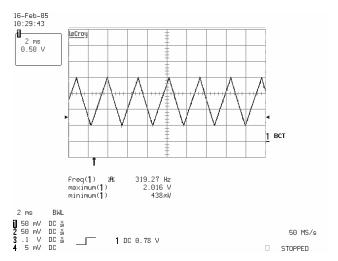

For analog dimming, the lamp intensity is controlled with the ADIM signal. A 2.5V on ADIM brings full brightness. Analog dimming waveforms are shown in Figures 8 and 9.

Figure 8. Analog Dimming at Maximum

Figure 9. Analog Dimming at Minimum

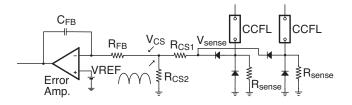

#### 2.6.1 Setting Lamp Current Sensing Resistors

#### 1) Positive Polarity Analog Dimming

Figure 10. Calculating Value of the **Analog Dimming Circuit Parameter**

Lamp current is sensed at R<sub>sense</sub> and the sensed voltage is divided by R<sub>CS1</sub> and R<sub>CS2</sub> and is averaged at Error Amp. by  $R_{FB}$  and  $C_{FB}$ .

$$R_{\text{sense\_eq}} = \frac{1 + \frac{V_{DF}}{I_{\text{lamp}} \cdot (R_{cs1} + R_{cs2})}}{R} \approx R_{\text{sense}} \| (R_{cs1} + R_{cs2}),$$

V<sub>DE</sub> is diode forward voltage

$$\begin{split} V_{sense} &= \left(\frac{1}{\pi} \int_{0}^{\pi} \sqrt{2} \cdot I_{Lamp} \cdot R_{sense\_eq} \cdot \sin\theta \cdot d\theta\right) - V_{DF} \\ &= \frac{2}{\pi} \cdot \sqrt{2} \cdot I_{Lamp} \cdot R_{sense\_eq} - V_{DF} \ (1) \end{split}$$

$$\begin{aligned} V_{CS} &= V_{sense} \cdot \frac{R_{cs2}}{R_{cs1} + R_{cs2}} = \left(\frac{2}{\pi} \cdot \sqrt{2} \cdot I_{Lamp} \cdot R_{sense} - V_{DF}\right) \\ &\cdot \frac{R_{cs2}}{R_{cs1} + R_{cs2}} \end{aligned} \tag{2.5}$$

Equation (2.5) assumes that the error amplifier loop is closed. The relationship between V<sub>CS</sub> and V<sub>ref</sub> is given in equation (2.6).

$$V_{\text{ref}} = V_{\text{CS}} = V_{\text{sense}} \cdot \frac{R_{\text{cs2}}}{R_{\text{cs1}} + R_{\text{cs2}}}$$

$$= \left(\frac{2}{\pi} \cdot \sqrt{2} \cdot I_{\text{Lamp}} \cdot R_{\text{sense}} - V_{\text{DF}}\right) \cdot \frac{R_{\text{cs2}}}{R_{\text{cs1}} + R_{\text{cs2}}}$$

$$\frac{R_{\text{cs1}}}{R_{\text{cs2}}} = \frac{V_{\text{sense}}}{V_{\text{ref}}} - 1$$

(2.6)

For example, suppose:

$$V_{ref} = 2.5V$$

,  $I_{Lamp} = 6.5mA$ ,  $R_{sense} = 1k\Omega$ ,  $R_{cs1} = 10k\Omega$

From these values, an approximate value of  $R_{cs2}$  can be derived. To get a more precise value for R<sub>CS2</sub>, use an iterative calculation. Use R<sub>sense</sub> to calculate R<sub>CS2</sub>, because the R<sub>sense\_eq</sub> value is unknown. After finding the value of R<sub>sense\_eq</sub>, use R<sub>sense\_eq</sub> to calculate R<sub>CS2</sub>. Calculate iteratively until the previous R<sub>sense\_eq</sub> value is almost equal to the current R<sub>sense\_eq</sub> value.

| $V_{REF}$                          | 2.5         |    |   |

|------------------------------------|-------------|----|---|

| I <sub>lamp</sub>                  | 6.5         |    |   |

| R <sub>sense</sub>                 | 1           | kΩ |   |

| Rsense_eff                         | 0.95        | kΩ | • |

| Diode drop voltage                 | 0.3         | V  |   |

| Vsense                             | 5.259453252 | V  |   |

| R <sub>CS1</sub> /R <sub>CS2</sub> | 1.103781301 |    |   |

| R <sub>CS1</sub>                   | 10          | kΩ |   |

| R <sub>CS2</sub>                   | 9.059765727 | kΩ |   |

$R_{\text{sense effective}} = 0.950148969 \text{k}\Omega = R_{\text{sense}} / (R_{\text{CS1}} + R_{\text{CS2}})$

#### 2) Negative Polarity Analog Dimming

Figure 11. Calculating Value of the Analog Dimming **Inverting Circuit Parameter**

Lamp current is sensed at R<sub>sense</sub> and the sensed voltage is divided by R<sub>cs1</sub> and R<sub>cs2</sub> and is averaged at Error Amp. by  $R_{FB}$  and  $C_{FB}$ .

$$R_{sense\_eq} = \frac{1 + \frac{V_{DF}}{I_{lamp} \cdot (R_{cs1} + R_{cs2})}}{R} \approx R_{sense} \parallel (R_{cs1} + R_{cs2}),$$

V<sub>DF</sub> is diode forward voltage

$$\begin{aligned} \mathbf{V}_{sense} &= \left(\frac{1}{\pi} \int_{0}^{\pi} \sqrt{2} \cdot \mathbf{I}_{Lamp} \cdot \mathbf{R}_{sense\_eq} \cdot \sin\theta \cdot d\theta\right) - \mathbf{V}_{DF} \\ &= \frac{2}{\pi} \cdot \sqrt{2} \cdot \mathbf{I}_{Lamp} \cdot \mathbf{R}_{sense\_eq} - \mathbf{V}_{DF} \ (1) \end{aligned}$$

$$\begin{aligned} V_{CS} &= V_{sense} \cdot \frac{R_{cs2}}{R_{cs1} + R_{cs2}} = \left(\frac{2}{\pi} \cdot \sqrt{2} \cdot I_{Lamp} \cdot R_{sense} - V_{DF}\right) \\ &\cdot \frac{R_{cs2}}{R_{cs1} + R_{cs2}} \end{aligned} \tag{2.8}$$

Equation (2.8) assumes the error amplifier loop is closed. The relationship between V<sub>CS</sub> and V<sub>A</sub> (dimming control voltage) is given in equation (2.9).

$$V_{ref} = \frac{V_A \cdot R_{FB} + V_{CS} \cdot R_A}{R_{FR} + R_A}$$

(2.9)

5 REV. 1.0.1 4/20/06

(2.7)

The relationship between dimming control voltage and lamp current can be programmed for the application. For example, suppose:

$$V_{Amin.} = 0, I_{Lamp.max} = 7mA$$

(2.10)

$$V_{Amax.} = 3.3, I_{Lamp.min} = 3mA$$

(2.11)

$$I_{Lamp.min} = \alpha \cdot I_{Lamp.max}$$

(2.12)

Substituting for  $V_A$  and  $V_{CS}$  in equation (2.9) from equation (2.10) results in:

$$V_{REF} = \frac{V_{CSmax} \cdot R_A}{R_{FB} + R_A}$$

(2.13)

Substituting for  $V_A$  and  $V_{CS}$  in equation (2.9) from equation (2.11) results in:

$$V_{ref} = \frac{V_{Amax} \cdot R_{FB} + V_{CSmin} \cdot R_A}{R_{FB} + R_A}$$

$$= \frac{V_{Amax} \cdot R_{FB} + \alpha \cdot V_{CSmax} \cdot R_{A}}{R_{FB} + R_{\Delta}}$$

(2.14)

Multiplying equation (2.13) by  $R_{FR} + R_A$  gives:

$$V_{ref} \cdot R_{FB} + V_{ref} \cdot R_A = V_{CSmax} \cdot R_A$$

(2.15)

Multiplying equation (2.14) by  $R_{FB} + R_A$  gives:

$$V_{ref} \cdot R_{FB} + V_{ref} \cdot R_A = V_{Amax} \cdot R_{FB} + \alpha \cdot V_{CSmax} \cdot R_A$$

(2.16)

$$(V_{ref} - V_{Amax}) \cdot R_{FB} + V_{ref} \cdot R_A = \alpha \cdot V_{CSmax} \cdot R_A$$

(2.17)

Multiplying equation (2.15) by  $\alpha$  gives:

$$\alpha \cdot V_{ref} \cdot R_{FB} + \alpha \cdot V_{ref} \cdot R_A = \alpha \cdot V_{CSmax} \cdot R_A$$

(2.18)

Subtracting equation (2.17) from equation (2.18) gives:

$$(V_{Amax} + V_{ref}^{(\alpha-1)}) \cdot R_{FB} + V_{ref}^{(\alpha-1)} \cdot R_A = 0$$

(2.19)

$$(V_{Amax} + V_{ref}^{(\alpha-1)}) \cdot R_{FB} = V_{ref}^{(\alpha-1)} \cdot R_A$$

(2.20)

Equation (2.20) can be rewritten as:

$$R_{A} = \frac{(V_{Amax} + V_{ref}^{(\alpha-1)}) \cdot R_{FB}}{V_{c}^{(\alpha-1)}} = \beta \cdot R_{FB}$$

(2.21)

$R_A$  is calculated by selecting  $R_{FB}$  and solving equation (2.21). Substituting for  $R_A$  in equation (2.13) from equation (2.21) and rewriting gives:

$$\begin{split} V_{CSmax} &= \frac{V_{ref} \cdot (R_{FB} + R_A)}{R_A} = \frac{V_{ref} \cdot (1 + \beta) \cdot R_{FB}}{\beta \cdot R_{FB}} \\ &= \frac{V_{ref} \cdot (1 + \beta)}{\beta} = V_{ref} \cdot \left(1 + \frac{1}{\beta}\right) \\ &= V_{sense} \cdot \frac{R_{cs2}}{R_{cs1} + R_{cs2}} \\ &= \left(\frac{2}{\pi} \cdot \sqrt{2} \cdot I_{Lamp} \cdot R_{sense} - V_{DF}\right) \cdot \frac{R_{cs2}}{R_{cs1} + R_{cs2}} \end{split} \tag{2.22}$$

$$\frac{R_{cs1}}{R_{cs2}} = \frac{V_{sense}}{V_{ref}\left(1 + \frac{1}{\beta}\right)} - 1$$

(2.23)

For example:

$$V_{ref} = 2.5V$$

,  $I_{lampmax} = 6.7mA$ ,  $I_{lampmin} = 4mA$ ,  $R_{FB} = 100k\Omega$ ,  $R_{sense} = 1.5k\Omega$ ,  $R_{CSI} = 10k\Omega$

From these values, it is possible to obtain the value of  $R_{CS2}.$  To get more precise value of RCS2, use an iterative calculation. Use  $R_{sense}$  to calculate  $R_{CS2},$  because  $R_{sense\_eq}$  is unknown. After the first calculation,  $R_{sense\_eq}$  can be resolved. Calculate the  $R_{CS2}$  value using  $R_{sense\_eq}.$  Calculate iteratively until the previous  $R_{sense\_eq}$  value becomes almost equal to the current  $R_{sense\_eq}$  value.

The data to input

The calculated data

|      | V <sub>REF</sub> | V <sub>A</sub> | I <sub>lamp</sub>                            |

|------|------------------|----------------|----------------------------------------------|

| Min. | -                | 0              | 4                                            |

| Тур. | 2.5              | -              | -                                            |

| Max. | -                | 3.2            | 6.7                                          |

|      |                  |                | α 0.597014925 6.7                            |

|      |                  |                | I <sub>lamp_max</sub> /I <sub>lamp_min</sub> |

| $R_{FB}$                           | 100         | kΩ |   |

|------------------------------------|-------------|----|---|

| R <sub>A</sub>                     | 217.6296296 | kΩ |   |

| b                                  | 2.176296296 |    |   |

| V <sub>CSmax</sub>                 | 3.64874064  |    |   |

| R <sub>sense</sub>                 | 1.5         | kΩ |   |

| R <sub>sense_eff</sub>             | 1.3861      |    | ◀ |

| Diode drop voltage                 | 0.3         | V  |   |

| Avg_max <sub>Vsense</sub>          | 8.061120587 | V  |   |

| R <sub>CS1</sub> /R <sub>CS2</sub> | 1.209288459 |    |   |

| R <sub>CS1</sub>                   | 10          | kΩ |   |

| R <sub>CS2</sub>                   | 8.269325588 | kΩ |   |

$R_{\text{sense effective}}$  1.386187316k $\Omega = R_{\text{sense}} / (R_{\text{CS1}} + R_{\text{CS2}})$

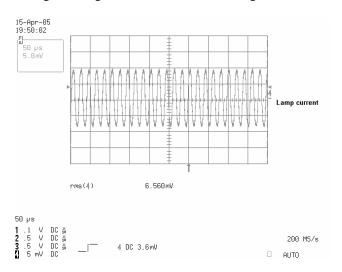

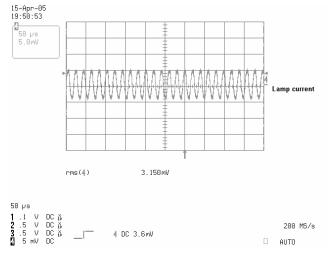

## 2.7 Burst Dimming

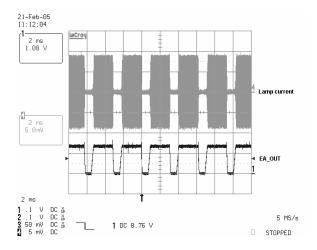

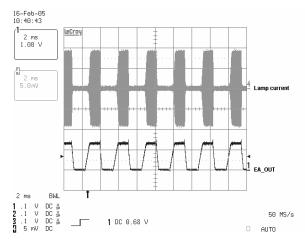

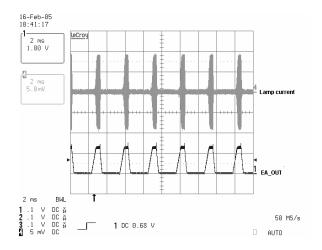

Lamp intensity is controlled with the BDIM signal. 0V on BDIM commands full brightness. The duty cycle of the burst dimming comparator determines the lamp brightness as a percent of the rated lamp current. Burst dimming is implemented by summing 85µA into the feedback node to turn down the lamp. If there is sufficient voltage for the lamp to strike, the feedback loop controls the lamp at the rated current using a fixed current-sense resistor. When the voltage of EA\_IN is brought higher than V<sub>ref</sub>, EA\_OUT becomes low and the MOSFET stops switching. At this time, the resonant tank voltage decays until the lamp extinguishes. C<sub>FB</sub> is reduced, if possible, to speed up the lamp re-strike. Burst dimming waveforms are shown in Figures 12, 13, and 14.

Figure 12. Burst Dimming at 75%

Figure 13. Burst Dimming at 50%

Figure 14. Burst Dimming at 25%

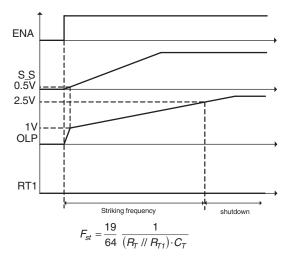

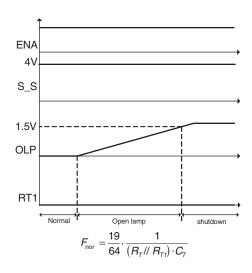

# 2.8 Open Lamp Regulation and Open Lamp Protection

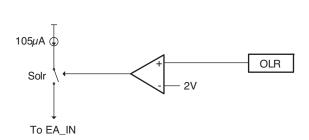

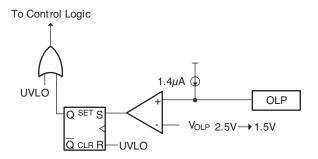

Power stage operation must be suspended if an open lamp occurs, because the power stage is at high gain. When a voltage higher than 2V is applied to the OLR (Open Lamp Regulation) pin, the part enters the regulation mode and controls EA\_OUT voltage to limit the lamp voltage by adding  $105\mu A$  into the feedback node. The OLP (Open Lamp Protection) capacitor, which is connected to the OLP pin, is charged by the  $1.4\mu A$  internal current source.

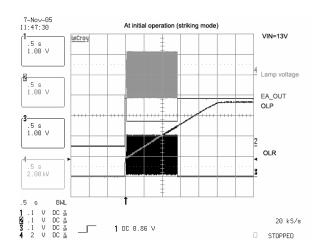

#### 2.8.1 Open Lamp at Initial Operation

OLP voltage starts from 1V. After reaching 2.5V, the IC shuts down when all the output are high.

The relationship between the OLP capacitor and the time  $\Delta T$  before the IC shuts down is calculated using the approximation  $I = C\Delta V/\Delta T$ , where  $I = 1.4\mu A$ ,  $\Delta V = 1.5V$ , resulting in  $\Delta T(s) = 1.1C(\mu F)$ .

#### 2.8.2 Normal Operation and Open Lamp

OLP voltage starts at 0V. After reaching 1.5V, the IC shuts down when all the outputs are high.

The relationship between the OLP capacitor and the time  $\Delta T$  before the IC shuts down is calculated using the approximation  $I = C\Delta V/\Delta T$ , where  $I = 1.4\mu A$ ,  $\Delta V = 1.5V$ , resulting in  $\Delta T(s) = 1.1C(\mu F)$ .

## 2.8.3 OLP Operation

Figure 15. Operating OLP

In normal operation, the voltage of D3's cathode is over 1V and D3 is turned off; Q1 is on; and OLP remains low. When open lamp occurs, the voltage of D3's cathode is under 1V and either D3 is turned on. Then Q1 is turned off and OLP start charging by an internal current source of  $1.4\mu A.$  If OLP reaches 2V, the IC is shut down. The base current of Q1 should be more than  $1.4\mu A/hfe.\ R6$  is determined by this condition. R4, R5, R7, and R8 are determined so that Q1 and D4 are turned off in the open lamp condition. C1 and C2 are determined so that the voltage of D3's cathode is over 1V in normal operation.

## 2.8.4 OLR Operation

$\begin{array}{l} OLR > 2V \uparrow \rightarrow Solr \ on \ duty \uparrow \rightarrow EA\_IN \uparrow \rightarrow EA\_OUT \uparrow \rightarrow Switching \ duty \uparrow \rightarrow Lamp \ voltage \downarrow \\ \rightarrow OLR > 2V \downarrow \rightarrow Solr \ on \ duty \downarrow \rightarrow EA\_IN \rightarrow EA\_OUT \downarrow \rightarrow Switching \ duty \uparrow \rightarrow Lamp \ voltage \uparrow \end{array}$

Figure 16. Operating OLR

Figure 17. Open Lamp Regulation Circuit

Figure 18. Open Lamp Protection Circuit

Figure 19. OLR Voltage During Striking Mode

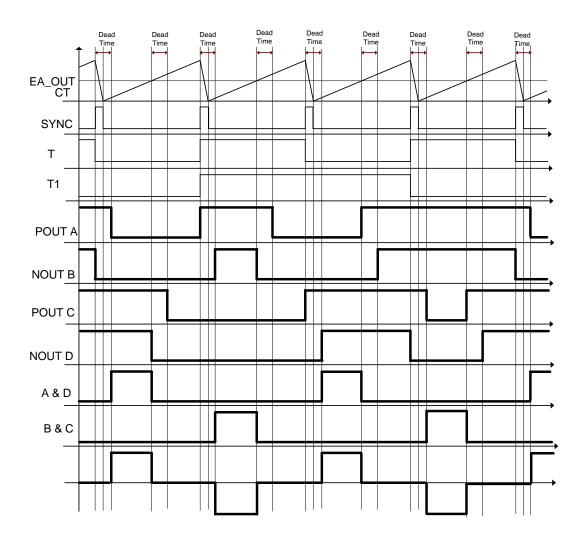

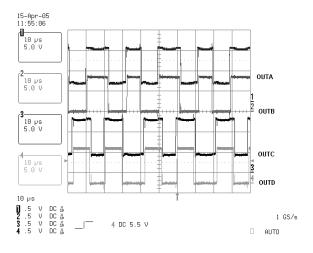

# 2.9 Output Driver

The four output drives are designed so that the two pairs of switches, pair A and B and pair C and D, never turn on simultaneously. The OUTA-OUTB pair is intended to drive

one half-bridge in the external power stage. The OUTC-OUTD pair drives the other half-bridge. The detailed timing relationship is shown below.

Figure 20. New Phase Shift Control Waveforms

# 2.10 CCFL Striking Sequence

Figure 21. CCFL Ignites

Figure 22. CCFL Does Not Ignite

Figure 23. Open Lamp

## 2.11 PCB Layout Guideline

- 1. Separating ground for analog and power portions of circuitry is one of the simplest and most effective methods of noise suppression. This is shown in Figure 24.

- 2. The traces between drive output and the MOSFET gates should be as short as possible and as wide as possible.

- 3. The traces of  $R_T$ ,  $C_T$ , and  $BC_T$  should be kept away from high-current components and traces.

Figure 24. PCB Layout

# 3. Power Stage Design

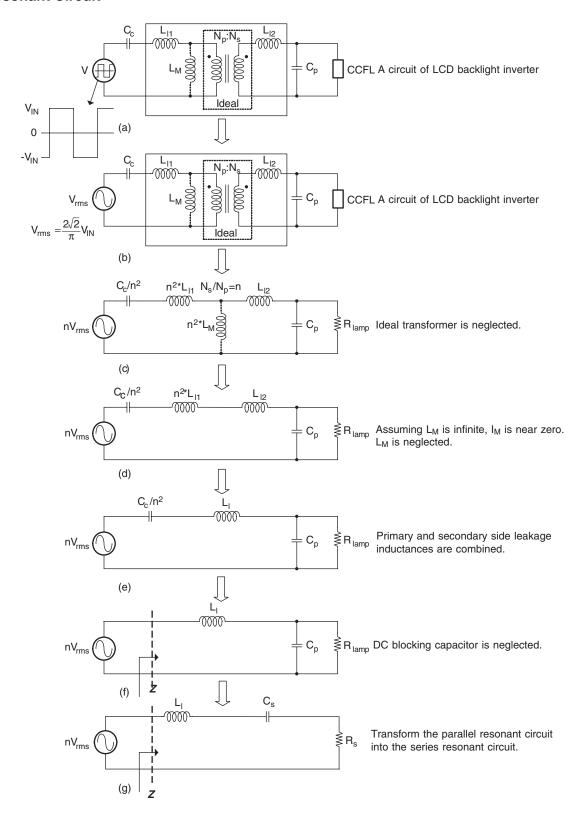

## 3.1 Resonant Circuit

Figure 25. Resonant Circuit

The resonant circuit (f) in Fig. 25 is a second-order low-pass filter and can be described by the following normalized parameters:

• The corner frequency:

$$\omega_0 = \frac{1}{\sqrt{L_1 C_p}} \tag{3.1}$$

• The characteristic impedance:

$$Z_0 = \omega_0 L_I = \frac{1}{\omega_0 C_p} = \sqrt{\frac{L_I}{C_p}}$$

(3.2)

The loaded quality factor at the corner frequency f<sub>o</sub>:

$$Q_{L} = \omega_{0}C_{p}R_{lamp} = \frac{R_{lamp}}{\omega_{0}L_{I}} = \frac{R_{lamp}}{Z_{0}}$$

(3.3)

The resonant frequency that forms the boundary between capacitive and inductive loads:

$$\omega_{\rm r} = \frac{1}{\sqrt{L_{\rm I}C_{\rm s}}} \tag{3.4}$$

• The loaded quality factor at the resonant frequency f<sub>r</sub>:

$$Q_{r} = \frac{\omega_{r} L_{I}}{R_{s}} = \frac{1}{\omega_{r} C_{s} R_{s}}$$

(3.5)

The input impedance of the resonant circuit (f) in Fig. 25 is:

$$Z = j\omega L + \frac{R_{lamp} \cdot \frac{1}{j\omega C_p}}{R_{lamp} + \frac{1}{j\omega C_p}} = \frac{R_{lamp} \bigg[ 1 - \bigg( \frac{\omega}{\omega_0} \bigg)^2 + j \frac{1}{Q_L} \bigg( \frac{\omega}{\omega_0} \bigg) \bigg]}{1 + j Q_L \bigg( \frac{\omega}{\omega_0} \bigg)}$$

$$= Ze^{j\phi} = R_S + jX_s \tag{3.6}$$

where,

$$\frac{Z}{Z_0} = \sqrt{\frac{Q_L^2 \left[1 - \left(\frac{\omega}{\omega_0}\right)^2\right]^2 + \left(\frac{\omega}{\omega_0}\right)^2}{1 + \left(Q_L \frac{\omega}{\omega_0}\right)^2}}$$

(3.7)

$$\varphi = \arctan \left\{ Q_{L} \left( \frac{\omega}{\omega_{0}} \right) \left[ \left( \frac{\omega}{\omega_{0}} \right)^{2} + \frac{1}{Q_{L}^{2}} - 1 \right] \right\}$$

(3.8)

$$R_{S} = Z\cos\varphi \tag{3.9}$$

$$X_{S} = Z \sin \varphi \tag{3.10}$$

The resonant frequency, f<sub>r</sub>, is defined as a frequency at which the phase shift is zero. The ratio of f<sub>r</sub> to the corner frequency, f<sub>o</sub>, is:

$$\frac{f_r}{f_0} = \sqrt{1 - \frac{1}{Q_L^2}}, \text{ for } Q_L \ge 1$$

(3.11)

The loaded quality factors  $Q_L$  and  $Q_r$  are related by:

$$\begin{split} &Q_r = \frac{\omega_r L}{R_s} = \frac{1}{\omega_r C_s R_s} = \omega_r C_p R_{lamp} \\ &= Q_r \Big( \frac{\omega_p}{\omega_0} \Big) = \sqrt{Q_L^2 - 1} \,, \ \, \text{for} \ \, Q_L \geq 1 \end{split} \tag{3.12}$$

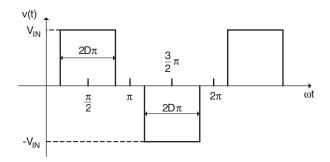

## 3.2 Voltage Transfer Function

Figure 26. Input Voltage of the Resonant Circuit

As shown in Fig. 26, the input voltage of the resonant circuit v is a square wave of magnitude  $V_{IN}$ , given by:

$$v = 0, \text{ for } 0 < \omega t \le \left(\frac{1}{2} - D\right)\pi$$

$$v = V_{IN}, \text{ for } \left(\frac{1}{2} - D\right)\pi < \omega t \le \left(\frac{1}{2} - D\right)\pi$$

$$v = 0, \text{ for } \left(\frac{1}{2} + D\right)\pi < \omega t \le \left(\frac{3}{2} - D\right)\pi$$

$$v = -V_{IN}, \text{ for } \left(\frac{3}{2} - D\right)\pi < \omega t \le \left(\frac{3}{2} - D\right)\pi$$

$$v = 0, \text{ for } \left(\frac{3}{2} - D\right)\pi < \omega t \le 2\pi$$

$$(3.13)$$

The fundamental component of this voltage is:

$$v_{i1} = V_m \sin(\omega t), \qquad (3.14)$$

in which the amplitude of  $v_{i1}$  can be found from Fourier analysis as:

$$V_{\rm m} = \frac{4}{\pi} V_{\rm IN} \sin D\pi \tag{3.15}$$

You can obtain the rms value of v<sub>i1</sub>:

$$V_{\rm rms} = \frac{V_{\rm m}}{\sqrt{2}} = \frac{2\sqrt{2}}{\pi} V_{\rm IN} \sin D\pi$$

(3.16)

Which leads to the voltage transfer function from  $V_{IN}$  to the fundamental component at the input of the resonant circuit:

$$M_{V_S} = \frac{V_{rms}}{V_{IN}} = \frac{2\sqrt{2}}{\pi} \sin D\pi$$

(3.17)

According to Fig. 25(f), the voltage transfer function of the resonant circuit is:

$$M_{Vr} = \frac{V_{Ri}}{\sqrt{2} \cdot nV_{rms}} = \frac{\frac{\frac{R_{lamp}}{j\omega C_p}}{R_{lamp} + \frac{1}{j\omega C_p}}}{\frac{R_{lamp}}{j\omega C_p} + \frac{R_{lamp}}{j\omega C_p}}$$

$$= \frac{1}{1 - \left(\frac{\omega}{\omega_0}\right)^2 + j\frac{1}{Q_L}\left(\frac{\omega}{\omega_0}\right)} = M_{Vr}^{ej\phi}$$

(3.18)

where,

$$M_{Vr} = \frac{V_{Ri}}{nV_{rms}} = \frac{1}{\sqrt{\left[1 - \left(\frac{\omega}{\omega_0}\right)^2\right]^2 + \frac{1}{Q_L^2} \left(\frac{\omega}{\omega_0}\right)^2}}$$

(3.19)

$$\varphi = -\arctan \left[ \frac{1}{Q_{L}} \left( \frac{\omega}{\omega_{0}} \right)^{2} \right]$$

(3.20)

The maximum value of MVr is obtained by differentiating the quantity under the square-root sign with respect to f/fo and setting the result equal to zero. Hence, the normalized peak frequency is:

$$\frac{f_{pk}}{f_0} = 0$$

, for  $0 \le Q_L \le \frac{1}{\sqrt{2}}$  (3.21)

$$\frac{f_{pk}}{f_0} = \sqrt{1 - \frac{1}{4Q_1^2}}, \text{ for } Q_L \le \frac{1}{\sqrt{2}}$$

resulting in the maximum magnitude of the voltage transfer function of the resonant circuit:

$$M_{Vr(max)} = 1$$

, for  $0 \le Q_L \le \frac{1}{\sqrt{2}}$

$$M_{Vr(max)} = \frac{Q_L}{\sqrt{1 - \frac{1}{4Q_L^2}}}, \text{ for } Q_L \le \frac{1}{\sqrt{2}}$$

(3.22)

The magnitude of the DC-to-AC voltage transfer function of the LCD backlight inverter without losses is obtained from (3.17) and (3.22):

$$M_{VI} = \frac{V_{lamp}}{V_{IN}} = M_{Vs} \cdot (nM_{Vr})$$

$$= \frac{2\sqrt{2} \cdot n \sin D\pi}{\pi \sqrt{\left[1 - \left(\frac{\omega}{\omega_0}\right)^2\right] + \frac{1}{Q_L^2} \left(\frac{\omega}{\omega_0}\right)^2}}$$

(3.23)

The maximum magnitude of the DC-to-AC voltage transfer function of the LCD backlight inverter without losses is:

$$M_{Vl(max)} = \frac{2\sqrt{2} \cdot n}{\pi}, \text{ for } 0 \le Q_{L} \le \frac{1}{\sqrt{2}}$$

$$M_{Vl(max)} = \frac{2\sqrt{2} \cdot nQ_{L}}{\pi \sqrt{1 - \frac{1}{4Q_{L}^{2}}}}, \text{ for } Q_{L} \ge \frac{1}{\sqrt{2}}$$

(3.24)

## 3.2 Design Procedure

A LCD monitor backlight circuit illustrates a design based on the FAN7311. The inverter is designed to drive two CCFLs with the following specifications.

| Panel Model              | LM151X2(LG.PHILIPS LCD) |  |

|--------------------------|-------------------------|--|

| Input Voltage            | 9 ~ 15V                 |  |

| Striking Voltage 880Vrms |                         |  |

| Operating Voltage        | 585Vrms (Typ.)          |  |

| Operating Current        | 8mArms (Typ.)           |  |

| Operating Frequency      | 50kHz (Typ.)            |  |

| Rated Power              | 4.68W/CCFL              |  |

| Efficiency               | 85% (Typ.)              |  |

#### 1) Select Transformer's Primary Turns

The number of primary turns is determined by Faraday's law.  $N_{p,min}$  is fixed by the minimum voltage across the primary and the maximum on time.

$$N_{p, min} = \frac{V_{IN, min} \cdot \Delta t_{max}}{\Delta B \cdot A}$$

where  $N_{p,min}$  = Minimum number of primary turns

$V_{IN.min}$  = Minimum input voltage (Volts)

$\Delta B$  = Core magnetic flux density change (Tesla)

Δt<sub>max</sub> = Maximum overlap on-time of diagonal MOSFET switches (us)

$A_e$  = Core cross-sectional area (mm<sup>2</sup>)

A transformer used in a full-bridge topology operates in two quadrants of the B-H curve such that the maximum magnetic flux density is  $B_{max}=0.5\Delta B.$  For most cores, saturation magnetic flux density is about 400mT. Margin considered, determine that the maximum magnetic flux density  $B_{max}=0.5$  Bsat, so the maximum magnetic flux density is  $B_{max}=200\text{mT}.$  In an example with a minimum voltage of 9V, operating frequency 50KHz, maximum on time of diagonal MOSFET switches of  $10\mu s$  and a core cross-sectional area (EPC17, EPC19, EFD1820) of  $22\text{mm}^2$ , the minimum number of primary turns required is:

$$N_{p, min} = \frac{V_{IN, min} \cdot \Delta t_{max}}{\Delta B \cdot A_e} = \frac{9 \cdot 10}{400 \cdot 22} \approx 10 T_s$$

# 2) Select $\mathbf{Q}_{L}$ and Operation Frequency to Determine the Turns Ratio

Select a value of 1 for  $Q_L$ . Assume that  $f_{op} = f_{pk} = 50 kHz$  based on the LCD panel specification. From (3.21), the corner frequency is:

$$f_o = \frac{f_{pk}}{\sqrt{1 - \frac{1}{2Q_L^2}}} = \frac{50}{\sqrt{1 - \frac{1}{2 \cdot 1.1^2}}} = 70.7(kHz)$$

From (3.11), the resonant frequency that forms the boundary between capacitive and inductive loads is:

$$f_{r} = f_{o} \cdot \sqrt{1 - \frac{1}{Q_{L}^{2}}} = f_{pk} \cdot \frac{\sqrt{1 - \frac{1}{Q_{L}^{2}}}}{\sqrt{1 - \frac{1}{2Q_{L}^{2}}}} = 0(kHz)$$

Therefore, zero-voltage switching (ZVS) can be achieved at any operating frequency. For the reference design, the required secondary lamp voltage is 585V and the minimum voltage is 9V. Therefore, from (3.23), the minimum number of the turns ratio is:

$$n \ge \frac{585}{9} \cdot \frac{\pi \sqrt{\left[1 - \left(\frac{\omega_{op}}{\omega_{0}}\right)^{2}\right]^{2} + \frac{1}{Q_{L}^{2}} \left(\frac{\omega_{op}}{\omega_{0}}\right)^{2}}}{2\sqrt{2} \sin D\pi} \approx 62.5 T_{s},$$

$$\therefore \mathbf{M_{VI}} = \frac{2\sqrt{2} \cdot \mathbf{n} \sin \mathbf{D}\pi}{\pi \sqrt{\left[1 - \left(\frac{\omega}{\omega_0}\right)^2\right]^2 + \frac{1}{Q_L^2} \left(\frac{\omega}{\omega_0}\right)^2}} \ge \frac{585}{9}$$

#### 3) Determine the Required Output Capacitance

Using the above specifications, the equivalent resistance of a CCFL is:

$$R_{lamp} = \frac{V_{lamp}}{I_{lamp}} = \frac{585}{0.008} \approx 75(k\Omega)$$

The corner frequency is 70.7kHz. Assume a parasitic capacitance per lamp of 10pF. Each parasitic capacitance is effectively in parallel with each of the output capacitors.

The output capacitor is:

$$C_{\text{out}} = C_p - C_{\text{para}} = \frac{Q_L}{\omega_o R_{\text{lamp}}} - 10 \text{pF} \approx 21 \text{pF},$$

$$\therefore Q_L = \omega_o R_{\text{lamp}} C_p$$

Using (3.3), the value of the leakage inductance is:

$$L_{\rm I} = \frac{1}{\omega_{\rm o}^2 C_{\rm p}} \approx 164.6 (\rm mH)$$

**Note:** Considering minimum primary turns, minimum turns ratio, and leakage inductance, determine primary turns, turns ratio, and the gap of core to get the required leakage inductance. For the sample design, the number of primary turns is  $30T_s$  and that of the secondary turns is  $2200T_s$ . Turns ratio is 66.7.

# 4) Select the Proper Wire Gauges for the Primary and Secondary Transformer Windings

The approximate primary winding rms current  $I_p$  and approximate secondary winding rms current  $I_s$  are determined by the following equations.

$$\begin{split} I_p &= \frac{\pi}{2\sqrt{2}} \cdot \frac{P_{lamp}}{\eta V_{IN}}, \\ &\therefore P_{lamp} = \eta V_{IN} I_{IN}, I_{IN} = \frac{2\sqrt{2}}{\pi} I_p \\ I_s &= \sqrt{I_{lamp}}^2 + \left[2\pi f_{op} C_{out} V_{lamp}\right]^2 \end{split}$$

Values that must be known or selected initially:

| Parameter             | Description                           | Typical Value | Units             |

|-----------------------|---------------------------------------|---------------|-------------------|

| V <sub>lamp</sub>     | Nominal lamp operating voltage        | 585           | V                 |

| I <sub>lamp</sub>     | Nominal lamp operating current        | 8             | mA                |

| f <sub>op</sub>       | Operating frequency                   | 50            | kHz               |

| f <sub>pk</sub>       | Peak frequency                        | 50            | kHz               |

| V <sub>in</sub>       | Input voltage                         | 9             | V                 |

| D                     | Duty ratio at input voltage           | 50            | %                 |

| Q <sub>L</sub>        | Loaded factor at the corner frequency | 1             |                   |

| C <sub>para</sub>     | Parasitic capacitance                 | 10            | pF                |

| A <sub>e</sub>        | Core cross-sectional area             | 22            | mm <sup>2</sup>   |

| B <sub>sat</sub>      | Saturation magnetic flux density      | 0.4           | Т                 |

| AL <sub>leakage</sub> | AL value of leakage inductance        | 22            | nH/N <sup>2</sup> |

## Values that are calculated:

| B <sub>max</sub>     | Maximum magnetic flux density                     | 0.2         | T     |

|----------------------|---------------------------------------------------|-------------|-------|

| ΔΒ                   | Core magnetic flux density change                 | 0.4         | Т     |

| $\Delta t_{\sf max}$ | Maximum overlap on-time of diagonal switches      | 10          | μs    |

| f <sub>o</sub>       | Corner frequency                                  | 70.71067812 | kHz   |

| f <sub>r</sub>       | Resonant frequency                                | 0           | kHz   |

| R <sub>lamp</sub>    | Equivalent resistance of a CCFL                   | 73.125      | k¾    |

| $N_{p,min}$          | The minimum number of transformer's primary turns | 10          | Turns |

| n <sub>min</sub>     | The minimum number of the turns ratio             | 62.5        |       |

| C <sub>out</sub>     | The output capacitor                              | 20.78       | pF    |

| L <sub>l</sub>       | The leakage inductance of the transformer         | 164.59      | mH    |

| N <sub>p</sub>       | The number of transformer's primary turns         | 31          | Turns |

Values that must be selected with more than minimum turn ratio.

| n The number of the turns ratio | 62.5 |  |

|---------------------------------|------|--|

|---------------------------------|------|--|

The values that are calculated:

| $N_s$ | The number of transformer's secondary turns | 1934.1 | Turns |

|-------|---------------------------------------------|--------|-------|

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems

- which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support.