# EE 560 FABRICATION OF MOS CIRCUITS

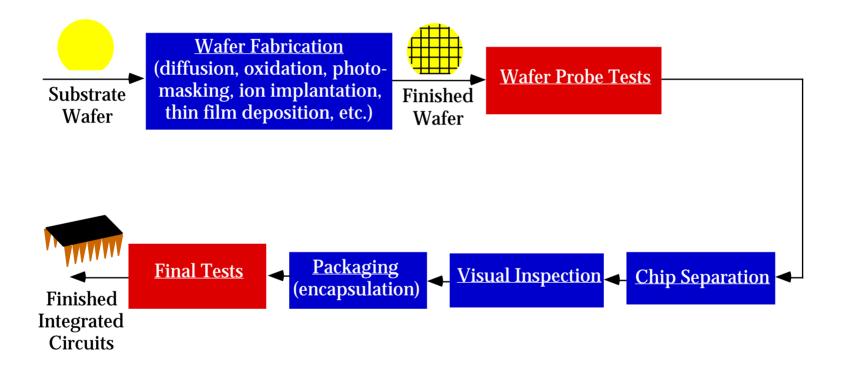

# **CMOS CHIP MANUFACTRING STEPS**

# **CMOS PROCESSING TECHNOLOGY**

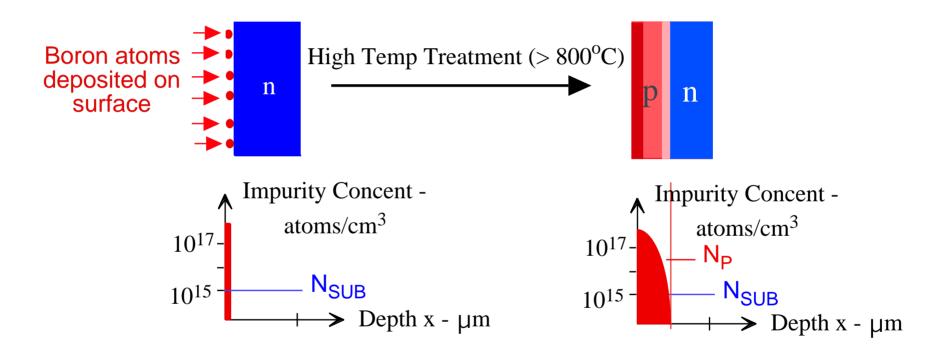

#### **DIFFUSION PROCESS**

- -> Boron typically used for p-type doping

- -> Arsenic and Phosphorus are typically used for n-type doping.

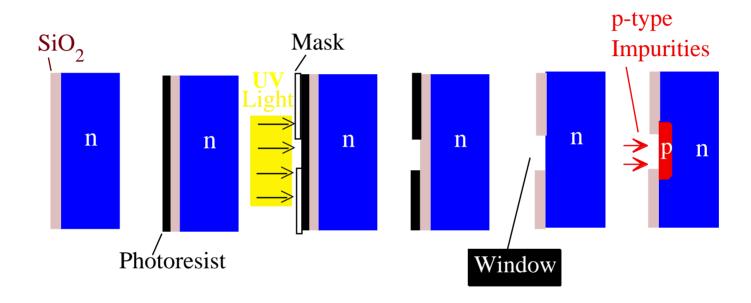

#### **PHOTOLITHOGRAPHY**

#### Methods for inserting impurity atoms into Si substrate

- Diffusion (high temperature)

- X Epitaxial growth followed by diffusion

- X Ion implantation (high velocity)

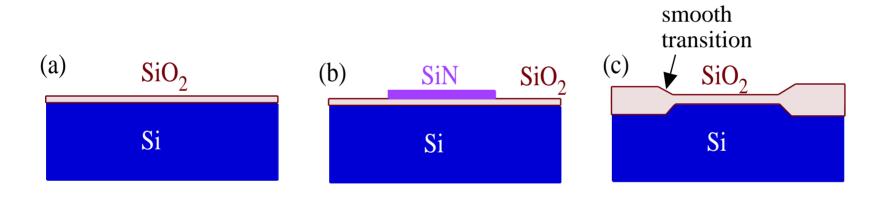

# Local Oxidation of Silicon (LOCOS)

- -> Fabricate thin SiO, layer adjacent to THICK SiO, layers.

- -> Transition from THICK to thin SiO<sub>2</sub> layers fabricated WITHOUT creating sharp vertical transitions.

SiN acts as barrier to oxygen atoms, stops further oxidation at SiN-SiO<sub>2</sub> interface.

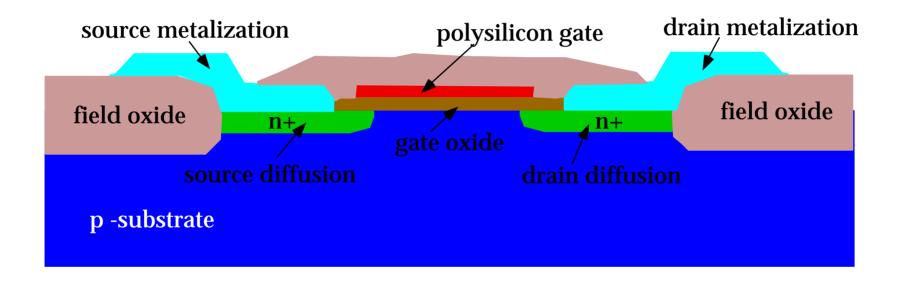

#### A FABRICATED n-MOS TRANSISTOR

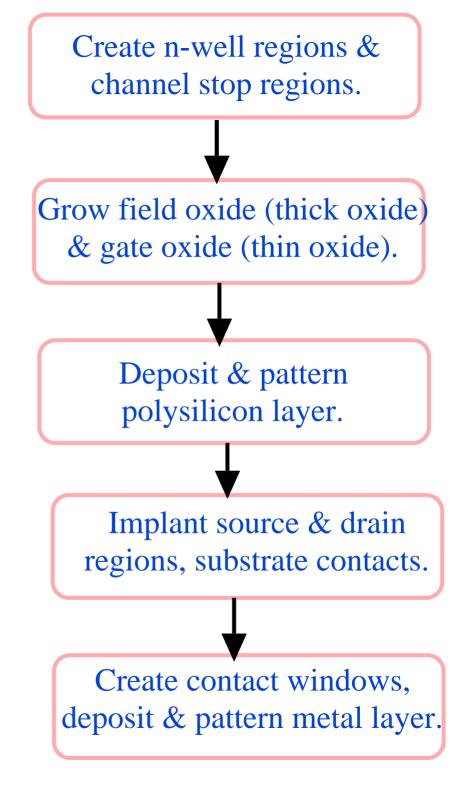

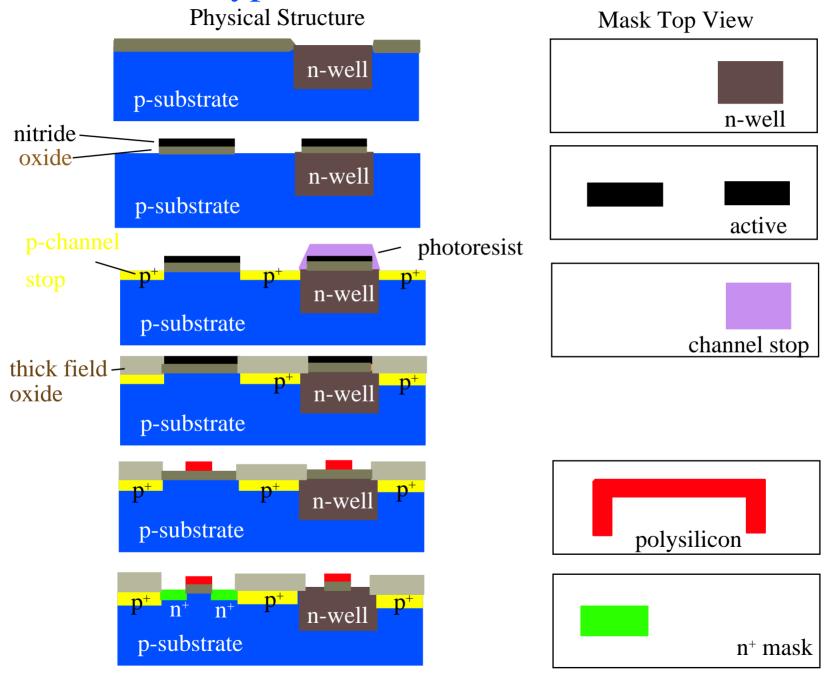

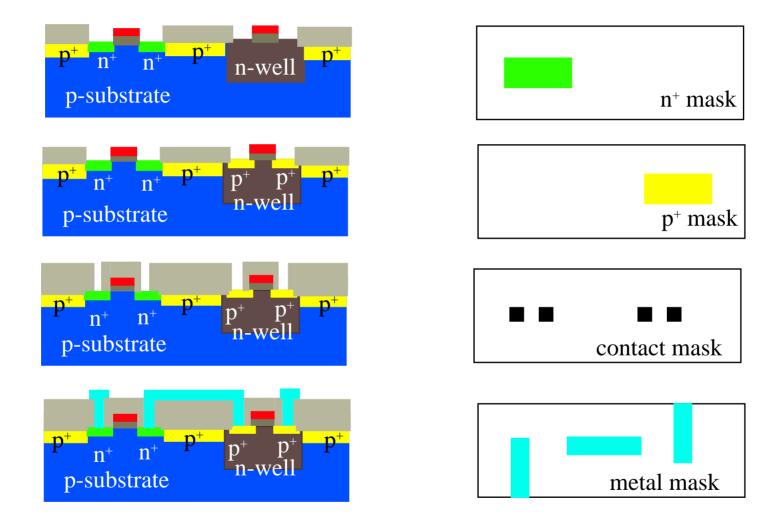

Simplified process sequence for the fabrication of an n-well CMOS IC with a single polysilicon layer

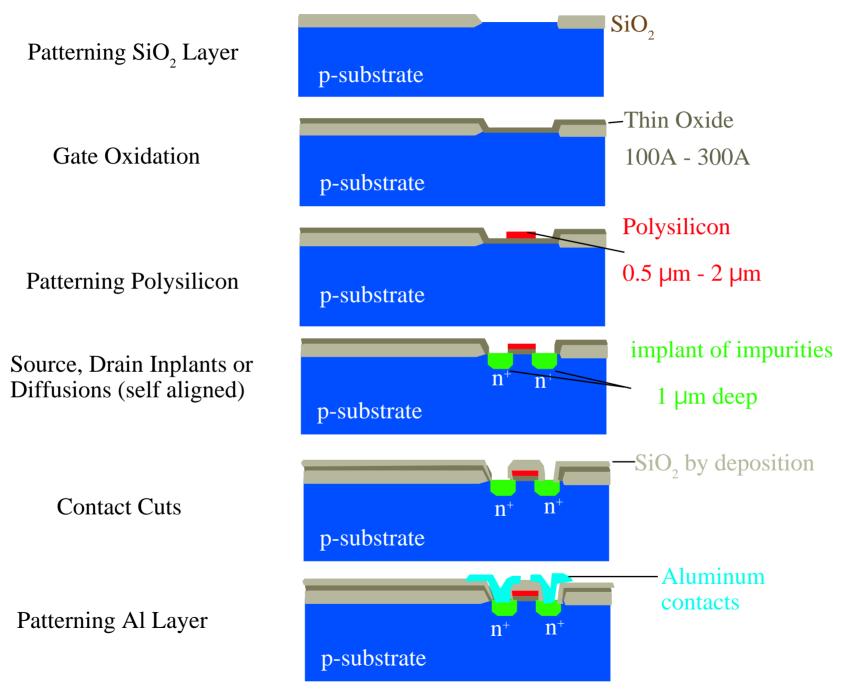

## Fabrication Steps in Si-Gate NMOS Process

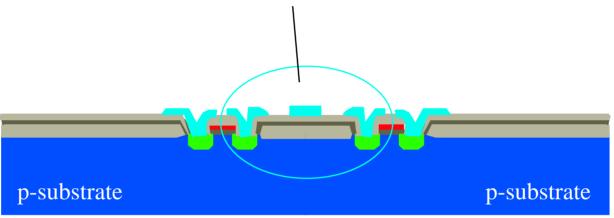

# Parasite MOS Transistor or Field Device

# Typical N-Well CMOS Process

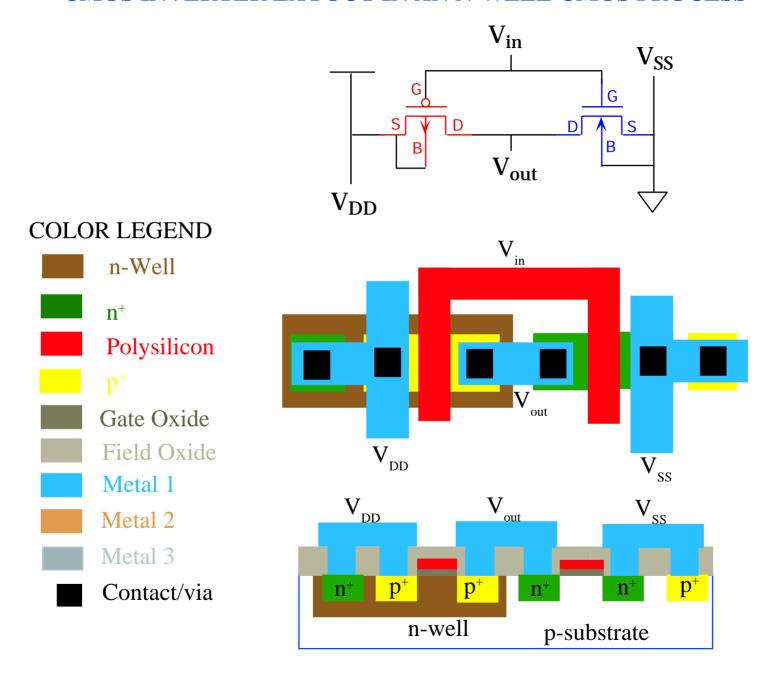

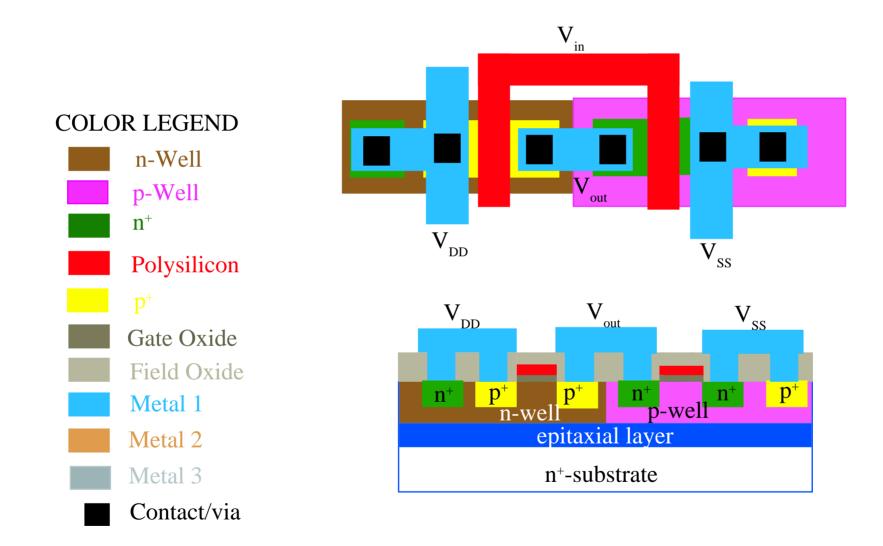

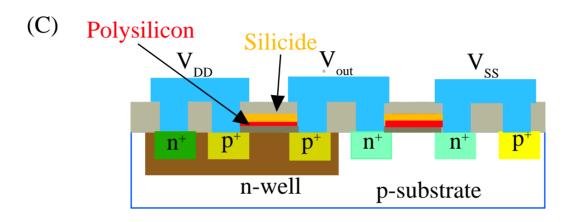

#### **CMOS INVERTER LAYOUT IN AN N-WELL CMOS PROCESS**

#### **CMOS INVERTER IN TWIN-WELL CMOS PROCESS**

# **CMOS PROCESS ENHANCEMENTS**

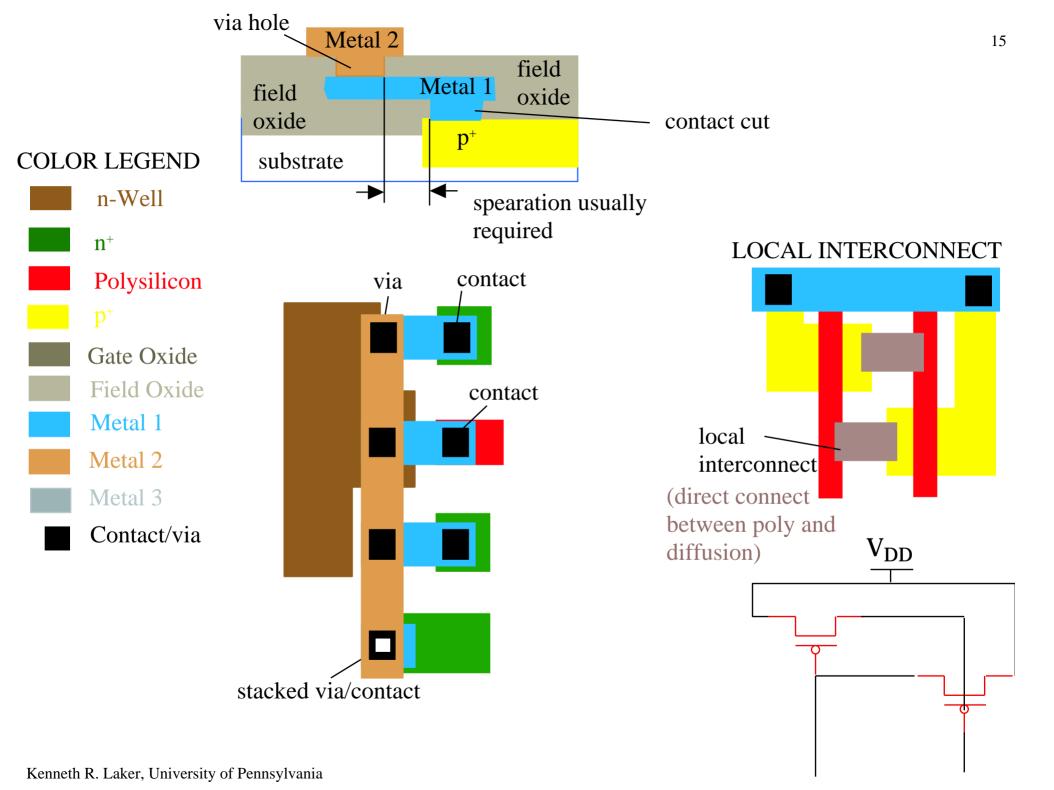

#### 1. INTERCONNECT

- A. Metal Interconnect (two, three, four or more levels)

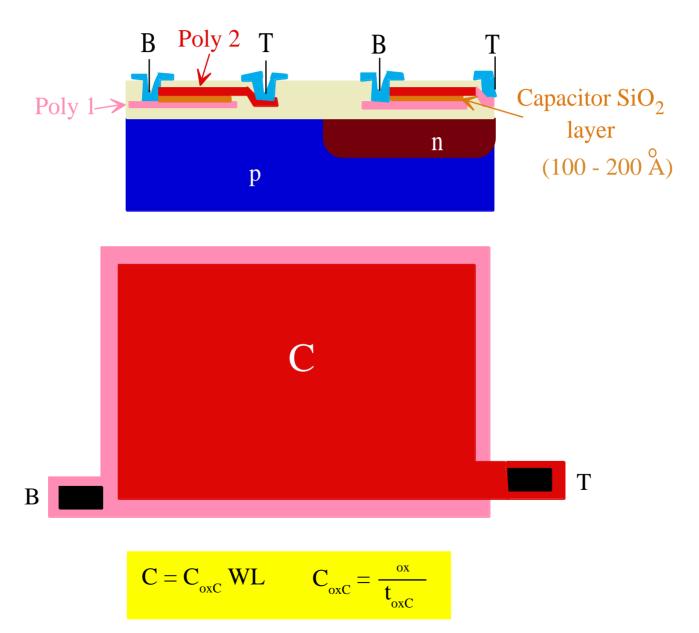

- B. Polysilicon (two or more levels, also for high quality capacitors)

- C. Polysilicon/Refractory Metal Inteconnect

- D. Local Inteconnect

#### 2. CIRCUIT ELEMENTS

- A. Resistors

- B. Capacitors

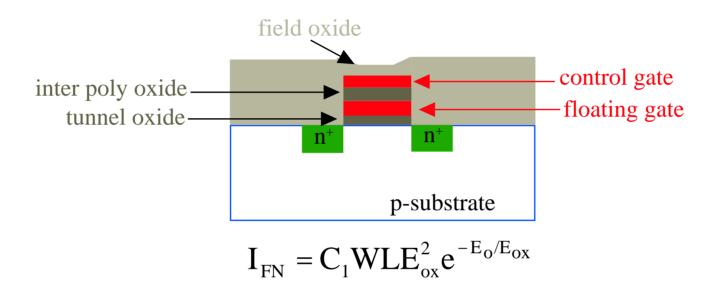

- C. Electrically Alterable ROM (EAROM EEROM EEPROM)

- D. Bipolar Transistors

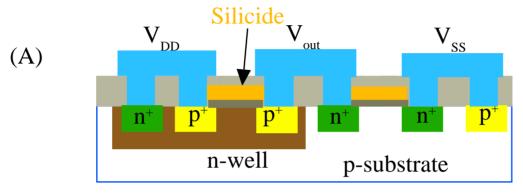

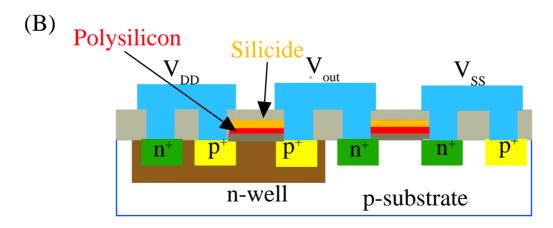

# Polysilicon/Refractory Metal or Silicide Gate/Interconnect Structures

Silicide Gate (e.g. silicon and tantalum)

Doped Polysilicon:  $R_{\text{sheet}} = 20 \text{ to } 40$  /Square

Silicide:  $R_{sheet} = 1 \text{ to } 5$  /Square

Polysilicon/Silicide (Polycide) Gate

Self-Aligned Polysilicon/Silicide (Salicide)

- (i) Polysilicon/silicide gate,

- (ii) Silicide source/drain(s) p<sup>+</sup> n<sup>+</sup>

# **CMOS DOUBLE POLY CAPACITORS**

Kenneth R. Laker, University of Pennsylvania

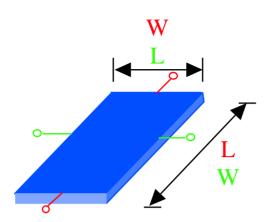

# **RESISTORS**

$$R = -\frac{L}{t} \frac{L}{W} = R_s \frac{L}{W}$$

= resistivity

t = thickness

L = conductor length

W = conductor width

$R_s$  = sheet resistance /sq

$$R_c = k \frac{L}{W}$$

Typical Sheet Resistance for Conductors (R<sub>s</sub> - /sq)

| Material         | Min  | Typ  | Max  |

|------------------|------|------|------|

| Metal - Meal 2   | 0.05 | 0.07 | 0.1  |

| Metal 3          | 0.03 | 0.04 | 0.05 |

| Polysilicon      | 15   | 20   | 30   |

| Silicide         | 2    | 3    | 6    |

| n+, p+ Diffusion | 10   | 25   | 100  |

| n-Well           | 1K   | 2K   | 5K   |

$$R_c = k \frac{L}{W}$$

$$k = \frac{1}{\mu C_{ox}(V_{gs} - V_T)}$$

n-Well

MOS Resistor

# **EEPROM TECHNOLOGY**

where

$$E_{ox} = \frac{V_{gs}}{t_{ox}} \quad \text{electric field across tunnel oxide}$$

E<sub>0</sub> and C<sub>1</sub> are process dependent constants

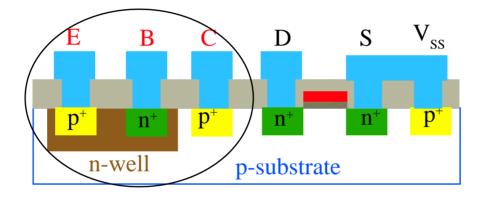

# BIPOLAR TRANSISTORS IN STANDARD CMOS

#### Substrate pnp Bipolar Transistor

## LAYOUT DESIGN RULES

PHYSICAL LAYER: prescription for preparing photomasks used in fabrication of ICs. Specify to the designer geometric constraints on the layout artwork so that patterns on the processed wafer will preserve the intended topology and geometry of the design.

PURPOSE: realize fabricated circuits optimum yield in smallest area possible without compromising the reliability of the circuit.

DESIGN RULE WAIVER: any significant and/or frequent departure from design rules.

#### TWO TYPES OF DESIGN RULES:

- a. line widths and separations

- b. interlayer registration

#### **DESIGN RULE SPECS:**

- a. 'micron' rules minimum feature sizes and spacings in µm units (normal spec in industry)

- b. 'lambda ( )' rules minimum feature sizes and spacings speced in terms of a single parameter (popularized by Mead and Conway and permits first order scaling)

# LAYOUT DESIGN RULES

The Design Process can be Abstracted to Manageable Number of Layout Levels that Represent the Physical Features on the Processed Silicon Wafer, i.e.

- -> Two different substrates (i.e. original substrate + well or twin wells)

- -> Doped regions p- and n- transistor forming materials (e.g. sources and drains)

- -> Transistor gate electrodes

- -> Interconnect paths

- -> Interlayer contacts

Kenneth R. Laker, University of Pennsylvan

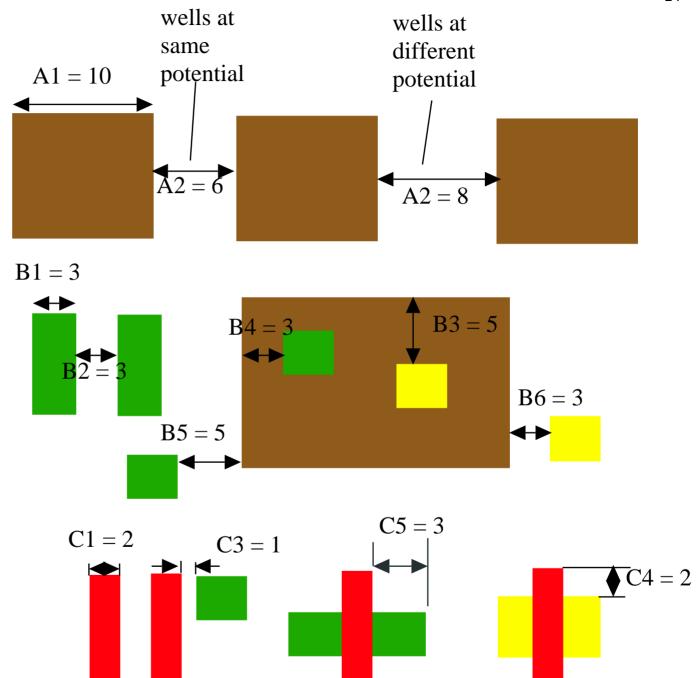

#### CMOS N-WELL DESIGN RULES

#### **COLOR LEGEND**

- n-Well

- p-Well

- $n^+$

- Polysilicon

- p<sup>r</sup>

- Gate Oxide

- Field Oxide

- Metal 1

- Metal 2

- Metal 3

- Contact/via

- B1 = TEXT R1

- B2 = TEXT R2

- C1 = TEXT R3

- C2 = TEXT R4

- C3 = TEXT R6

- C4 = TEXT R5 C5

- = TEXT R7

#### **COLOR LEGEND** E5 = 125 E3 = 2E1 = 2n-Well F2 = 3p-Well F1 = 3 $n^+$ | = | = 1Polysilicon E2 = 2E4 = 1E7 = 1Gate Oxide Field Oxide Metal 1 E8 = 3E9 = 6Metal 2 Metal 3 Contact/via J3 = 2 $E10 = 3 \longrightarrow$ I2 = 3E1 = TEXT - R10E2 = TEXT - R11J1 = 8E5 = TEXT - R12G1 = 2 $\mathbf{G}$ 3 = 1 E6 = TEXT - R13E3 = TEXT - R16H1 = 3E4 = TEXT - R17J2 = 5E7 = TEXT - R18H2 = 4G2 = 3E8 = TEXT - R14E9 = TEXT - R20E10 = TEXT - R19F1 = TEXT - R8F2 = TEXT - R9Kenneth R. Laker, University of Pennsylvania

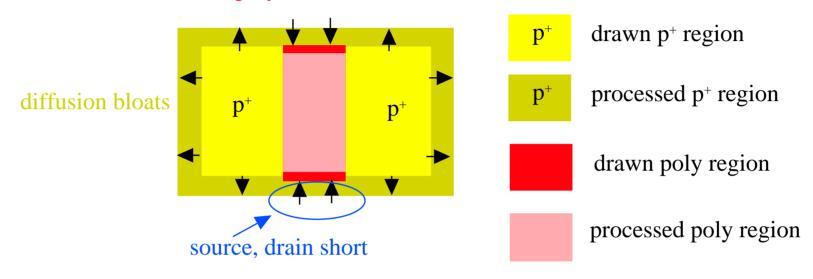

# EFFECT OF INSUFFICENT GATE EXTENSION

#### over-etched poly shrinks

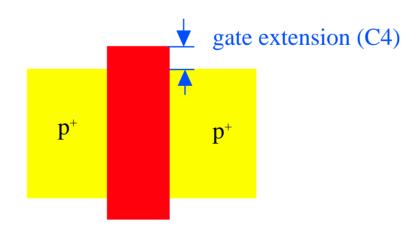

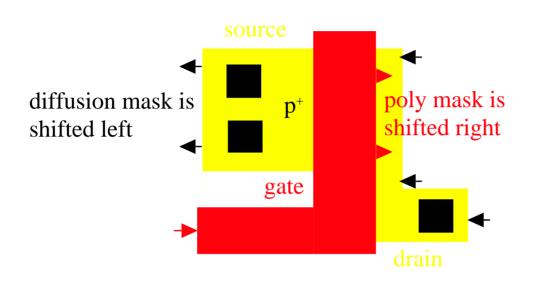

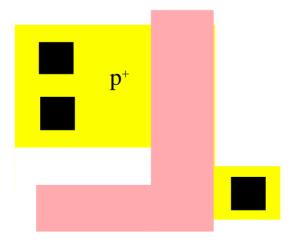

# EFFECT OF INSUFFICENT SOURCE-DRAIN EXTENSION

mask misalignment changes width of device and sometimes completely eleminates it.

p+ drawn p+ region

p+ processed p+ region

drawn poly region

processed poly region

# TECHNOLOGY RELATED CAD ISSUES

# TWO BASIC CHECKS MUST BE COMPLETED TO ENSURE THE MASK DATBASE DEVELOPED IN LAYOUT CAN BE TURNED INTO A WORKING CHIP:

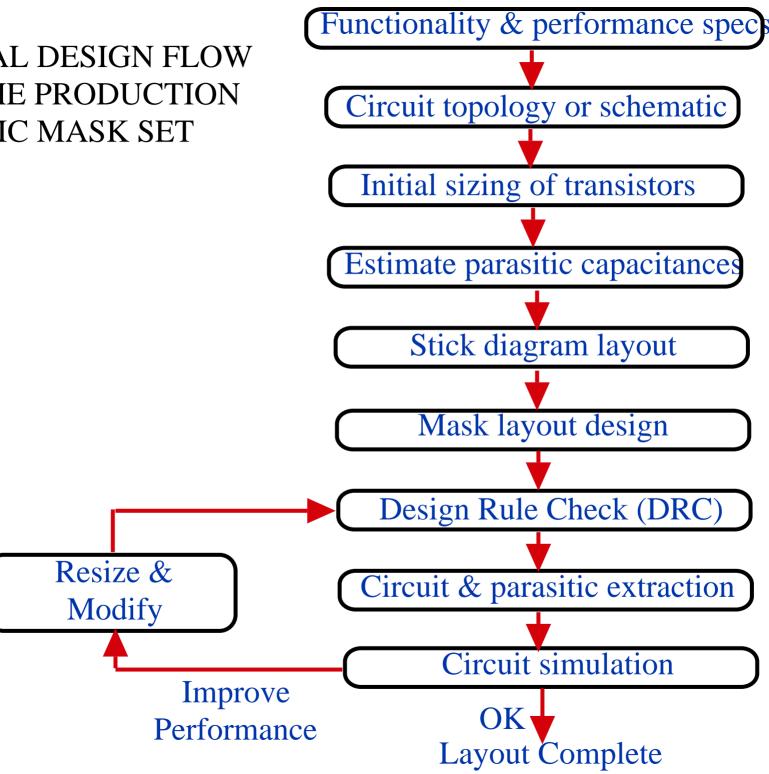

a. To verify specified Design Rules have been obeyed

(DESIGN RULE CHECK or DRC)

b. To verify masks produce correct interconnected set of circuit elements

(MASK CIRCUIT-EXTRACTION)

TYPICAL DESIGN FLOW FOR THE PRODUCTION OF AN IC MASK SET