## Message from the Author

I first became familiar with PLLs by working for National Semiconductor as an applications engineer. While supporting customers, I noticed that there were many repeat questions. Instead of creating the same response over and over, it made more sense to create a document, worksheet, or program to address these recurring questions in greater detail and just re-send the file. From all of these documents, worksheets, and programs, this book was born.

Many questions concerning PLLs can be answered through a greater understanding of the problem and the mathematics involved. By approaching problems in a rigorous mathematical way one gains a greater level of understanding, a greater level of satisfaction, and the ability to apply the concepts learned to other problems.

Many of the formulas that are commonly used for PLL design and simulation contain gross approximations with no or little justification of how they were derived. Others

are rigorously derived, but from outdated textbooks that make assumptions not true of the PLL systems today. It is therefore no surprise that there are so many rules of thumb to be born which yield unreliable results. Another fault of these formulas is that many of them have not been compared to measured data to ensure that they account for all relevant factors.

There is also the other approach, not trusting formulas enough and trusting only measured results. The fault with this is that many great insights are lost and it is difficult to learn and grow in PLL knowledge this way. Furthermore, by knowing what a result should theoretically be, it makes it easier to spot and diagnose problems with a PLL circuit. This book takes a unique approach to PLL design by combining rigorous mathematical derivations for formulas with actual measured data. When there is agreement between these two, then one can feel much more confident with the results.

## Credits

I would like to thank the following people for their assistance in producing this book.Useful Insights:Ian Thompson (Phase Noise of the phase – frequency detector), Bill Keese<br/>(AN-1001/Loop Filter Design), Yuko Kanagy (General PLL)Editing:Shigura Matsuda, Deborah Brown, Tom Mathews, Ahmed Salem<br/>Bill Burdette (1<sup>st</sup> Edition)

## **Table of Contents**

## Part I Introduction

| i.   | What's All of this PLL stuff?             | 5 |

|------|-------------------------------------------|---|

| ii.  | The Charge Pump PLL with a Passive Filter | 7 |

| iii. | The PLL as Viewed from a System Level     | 9 |

## Part II PLL Performance

1.

**Reference Spurs and their Causes**

## Spurs

|     | Addresses the causes of reference spurs and what can be done about them.        |    |  |  |

|-----|---------------------------------------------------------------------------------|----|--|--|

| 2.  | Non-Reference Spurs and their Causes                                            | 25 |  |  |

|     | Addresses different types of spurs, their causes, and their cures.              |    |  |  |

|     | Phase Noise                                                                     |    |  |  |

| 3.  | Noise Sources in a PLL System                                                   | 33 |  |  |

|     | Discusses the causes of phase noise and how to roughly predict it.              |    |  |  |

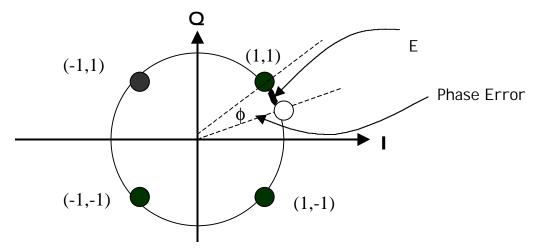

| 4.  | RMS Phase Error and Signal to Noise Ratio                                       | 49 |  |  |

|     | Discusses the meaning, calculation, and significance of RMS phase error.        |    |  |  |

|     | Lock Time                                                                       |    |  |  |

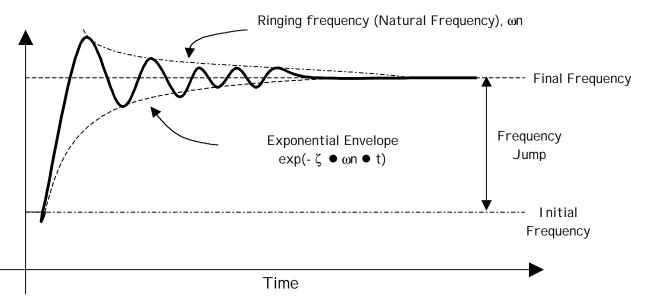

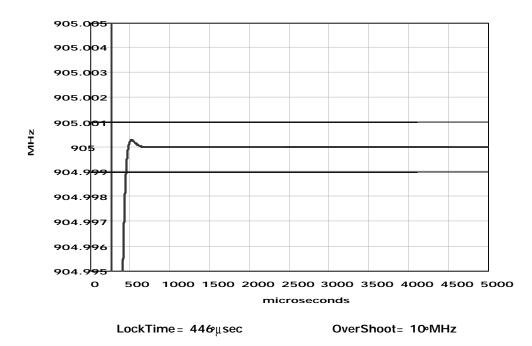

| 5.  | Transient Response of PLL Frequency Synthesizers                                | 55 |  |  |

|     | Addresses in depth lock time issues and derives all relevant equations.         |    |  |  |

|     | Other Topics                                                                    |    |  |  |

| 6.  | Discussions of the Phase/Frequency Detector for the Armchair<br>Philosopher     | 69 |  |  |

|     | Discusses the how's and why's of the operation of the phase-frequency detector. |    |  |  |

|     | Part III PLL Design                                                             |    |  |  |

|     | Methods for Passive Loop Filter Design                                          |    |  |  |

| 7.  | Fundamentals of Loop Filter Design                                              | 77 |  |  |

|     | Gives design equations for PLL Loop Filter Design.                              |    |  |  |

| 8.  | Equations for a Passive Second Order Loop Filter                                |    |  |  |

|     | Gives design equations for a second PLL Loop Filter Design.                     | 81 |  |  |

| 9.  | Equations for a Passive Third Order Loop Filter                                 |    |  |  |

|     | Gives design equations for third PLL Loop Filter Design.                        |    |  |  |

| 10. | Fourth and Higher Order Passive Loop Filter Designs                             | 97 |  |  |

|     | Gives design equations for fourth and higher order loop filter designs.         |    |  |  |

13

|     | Active Filters for High Voltage Tuning for a VCO                              |     |

|-----|-------------------------------------------------------------------------------|-----|

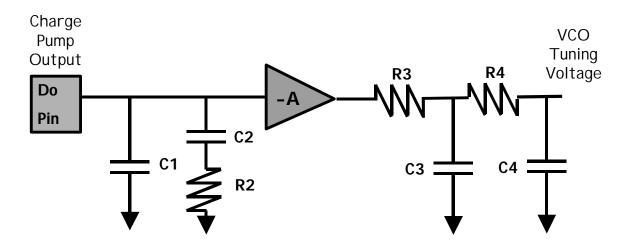

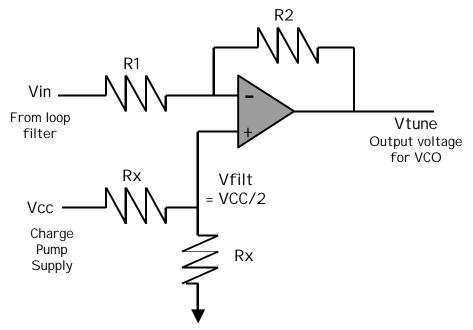

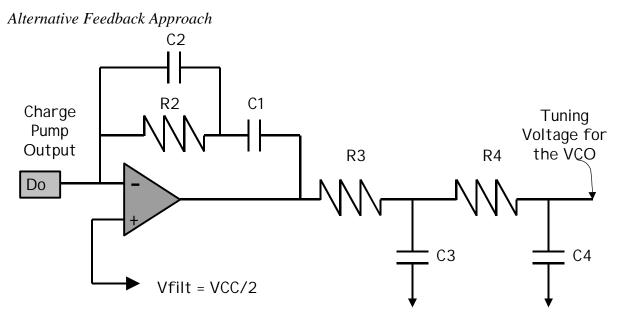

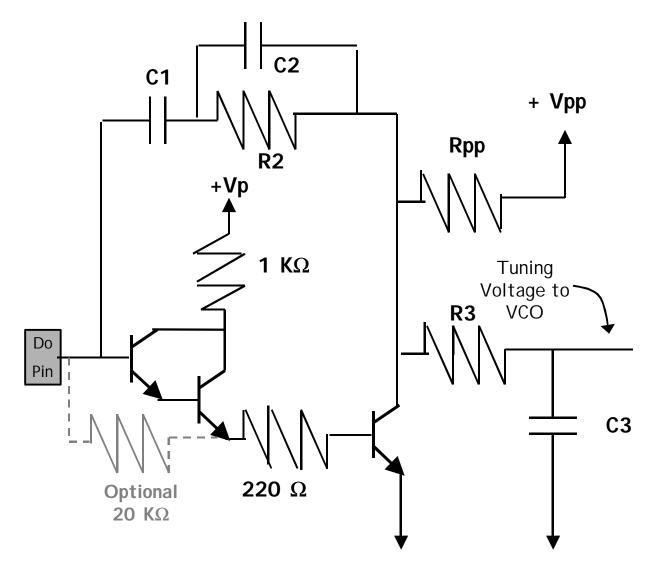

| 11. | Fundamentals of Active PLL Loop Filter Design                                 | 105 |

|     | Discusses all sorts of active filters using the charge pump output pin        |     |

| 12. | Design of an Active Loop Filter Using the Differential Phase Detector Outputs | 115 |

|     | Discusses a design using the differential phase detector outputs              |     |

|     | Spur Reducing PLL Design Techniques                                           |     |

| 13. | The Impact of Loop Filter Parameters and Filter Order on Reference Spurs      | 121 |

|     | Discusses how to add an op-amp for an active filter using the Do pin.         |     |

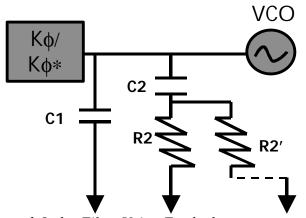

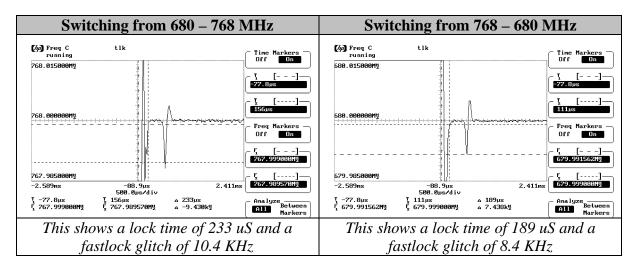

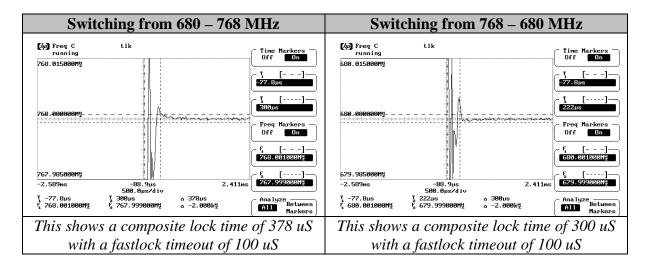

| 14. | Using the Fastlock Feature for PLL Design                                     | 127 |

Using the Fastlock Feature for PLL Design Discusses using these pins with an op-amp to design an active filter.

## Part IV Additional Topics

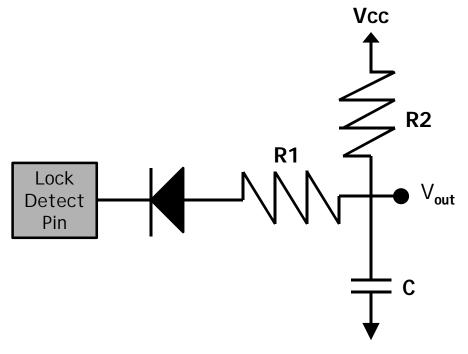

| 15. | Lock Detect Circuit Construction and Analysis                                     | 133 |

|-----|-----------------------------------------------------------------------------------|-----|

|     | Discusses how to build a more sensitive lock detect circuit and how it works.     |     |

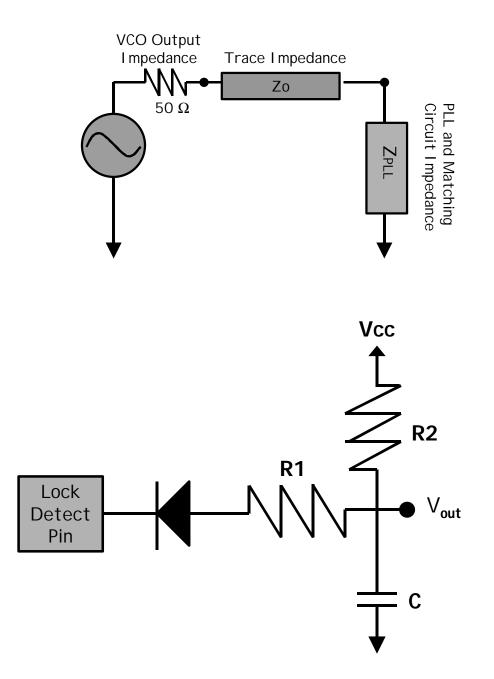

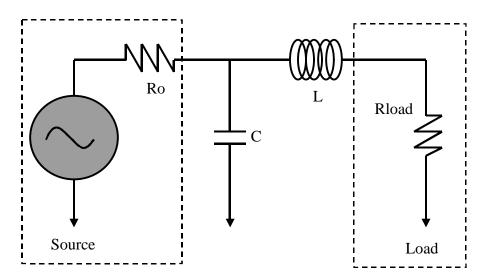

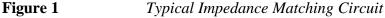

| 16. | Impedance Matching Issues and Techniques for PLLs                                 | 139 |

|     | Discusses how to match the VCO output to the PLL input                            |     |

| 17. | Routh Stability for PLL Loop Filters                                              | 145 |

|     | Discusses Routh's Stability Criterion as it applies to PLL Loop Filter Design.    |     |

| 18. | A Sample Loop Filter Analysis                                                     | 149 |

|     | Shows a sample loop filter analysis using a Mathcad Simulation tool               |     |

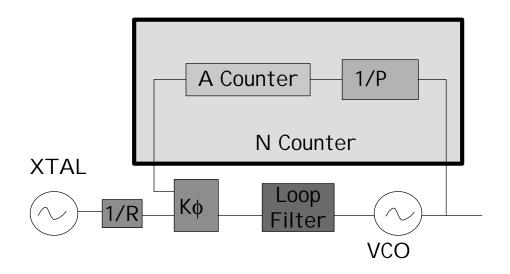

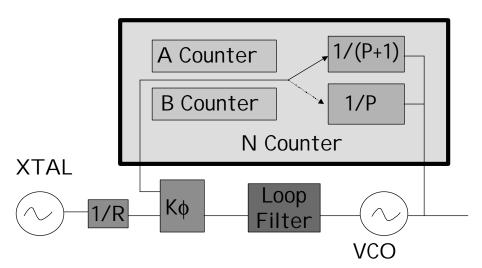

| 19. | Basic Prescaler Operation                                                         | 159 |

|     | Describes the operation of the single, dual, and quadruple modulus prescaler.     |     |

| 20. | Fundamentals of Fractional N PLLs                                                 | 163 |

|     | Discusses how fractional N PLLs work and when to use them.                        |     |

| 21. | Other PLL Design and Performance Issues                                           | 167 |

|     | N value determination, peaking and phase margin, sensitivity, concluding remarks. |     |

|     |                                                                                   |     |

## Part V Supplemental Information

| 22. | Glossary and Abbreviation List                                                | 173 |

|-----|-------------------------------------------------------------------------------|-----|

|     | Lists various PLL terms and symbols used in this book with their definitions. |     |

| 23. | References                                                                    | 183 |

| 24. | Useful Websites and Online RF Tools                                           | 185 |

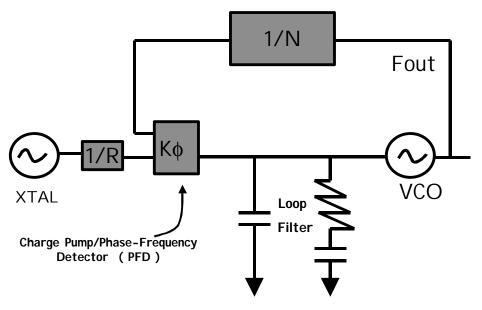

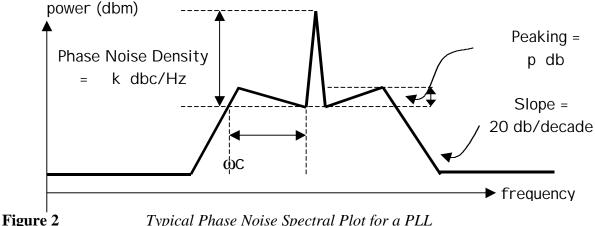

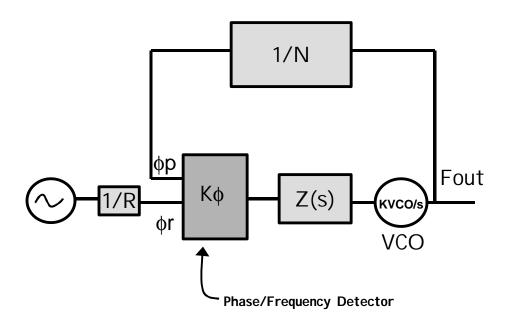

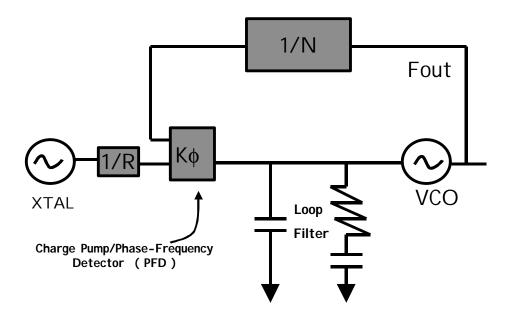

**Figure 1** The Basic PLL

#### **Basic PLL Operation and Terminology**

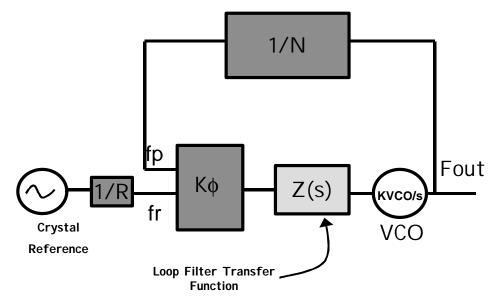

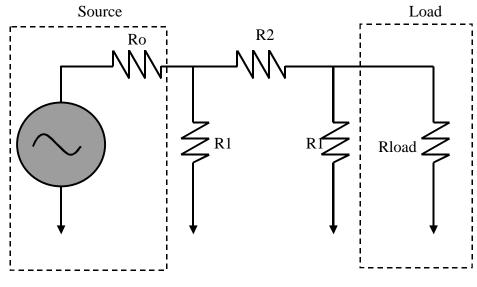

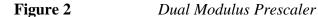

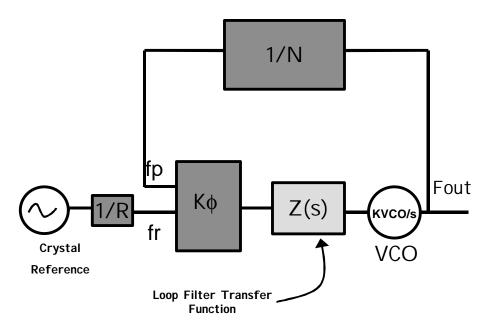

This section describes basic *PLL* (Phased Locked Loop) operation and introduces terminology that will be used throughout this book. The PLL starts with a stable crystal reference frequency (*XTAL*). This frequency is divided by R to a lower frequency, which is called the comparison frequency (*Fcomp*). This is one of the inputs to the phase detector. The phase-frequency detector outputs a current that has an average DC value proportional to the phase error between the comparison frequency and the output frequency, after it is divided by the *N* divider. The constant of proportionality is called *Kf*. Note that this constant turns out to be the magnitude of the current that the charge pump can source or sink. Although it is technically correct to divide this term by  $2\pi$ , it is unnecessary since it is canceled out by another factor of  $2\pi$  which comes from the VCO gain for all of the equations in this book. So technically, the units of *Kf* are expressed in mA/( $2\pi$  radians).

If one takes this average DC current value from the phase detector and multiplies it by the impedance of the loop filter (Z(s)), then the input voltage to the *VCO* (Voltage Controlled Oscillator) can be found. The VCO is a voltage to frequency converter and has a proportionality constant of *Kvco*. Note that the loop filter is a low pass filter, often implemented with discrete components. This loop filter is application specific, and much of this book is devoted to the loop filter. This tuning voltage adjusts the output phase of the VCO, such that its phase, when divided by N, is equal to the phase of the comparison frequency. Since phase is the integral of frequency, this implies that the frequencies will also be matched, and the output frequency will be given by:

$$Fout = \frac{N}{R} \bullet XTAL$$

This applies only when the PLL is in the locked state; this does not apply during the time when the PLL is acquiring a new frequency. For a given application, R is typically fixed, and the N value can easily be changed. If one assumes that N and R must be an integer, then this implies that the PLL can only generate frequencies that are a multiple of *Fcomp*. For this reason, many people think that *Fcomp* and the channel spacing are the same. Although this is often the case, this is not necessarily true. For a fractional N PLL, N is not restricted to an integer, and therefore the comparison frequency can be chosen to be much larger than the channel spacing. There are also less common cases where the comparison frequency is chosen smaller than the channel spacing to overcome restrictions on the allowable values of N, due to the prescaler. In general, it is preferable to have the comparison frequency as high as possible for optimum performance.

Note that the term PLL technically refers to the entire system shown in Figure 1; however, sometimes it is meant to refer to the entire system except for the crystal and VCO. This is due to the fact that these components are difficult to integrate on a PLL synthesizer chip.

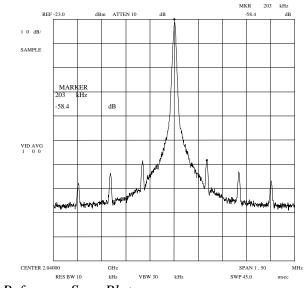

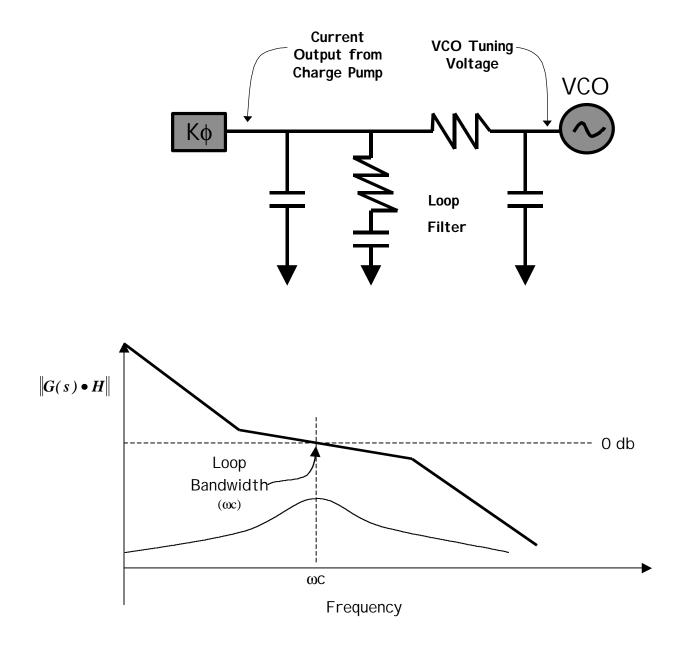

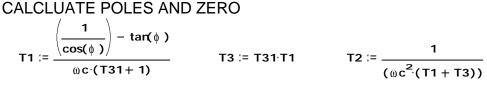

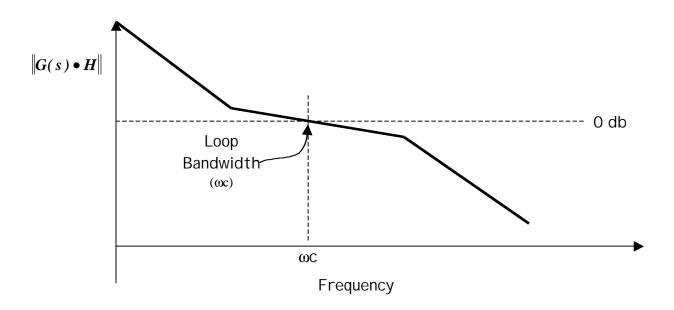

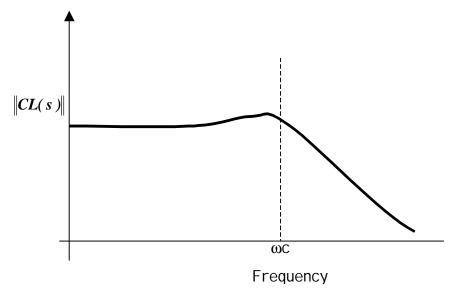

The transfer function from the output of the R counter to the output of the VCO determines a lot of the critical performance characteristics of the PLL. The closed loop bandwidth of this closed loop system is referred to as the loop bandwidth (wc), which is an important parameter for both the design of the loop filter and the performance of the PLL. Another parameter, phase margin (**f**) refers to 180 degrees minus the phase of the open loop phase transfer function from the output of the R counter to the output of the VCO. The phase margin is evaluated at the frequency that is equal to the loop bandwidth. This parameter has less of an impact on performance than the loop bandwidth, but still does have a significant impact and is a measure of the stability of the system.

## The PLL as a Frequency Synthesizer

The PLL has been around for many decades. Some of its earlier applications included keeping power generators in phase and synchronizing to the sync pulse in a TV Set. Still other applications include recovering a clock from asynchronous data and demodulating an FM modulated signal. However, the focus of this book is the use of a PLL as a frequency synthesizer.

In this type of application, the PLL is used to generate a set of discrete frequencies. A good example of this is FM radio. In FM radio, the valid stations range from 88 to 108 MHz, and are spaced 0.1 MHz apart. The PLL generates a frequency that is 10.7 MHz less than the desired channel, since the received signal is mixed with the PLL signal to always generate an IF (Intermediate Frequency) of 10.7 MHz. Therefore, the PLL generates frequencies ranging from 77.3 MHz to 97.3 MHz. The channel spacing would be equal to the comparison frequency, which would is 100 KHz.

A fixed crystal frequency of 10 MHz can be divided by an R value of 100 to yield a comparison frequency of 100 KHz. Then the N value ranging from 773 to 973 is programmed into the PLL. If the user is listening to a station at 99.3 MHz and decides to change the channel to 103.4 MHz, then the R value remains at 100, but the N value changes from 886 to 927. The performance of the radio will be impacted by the spectral purity of the PLL signal produced and also the time it takes for the PLL to switch frequencies.

The loop filter has a large impact on how long it takes for the PLL to switch frequencies and also on how spectrally pure the PLL signal produced is. For this reason, loop filter design is the central focus of this book.

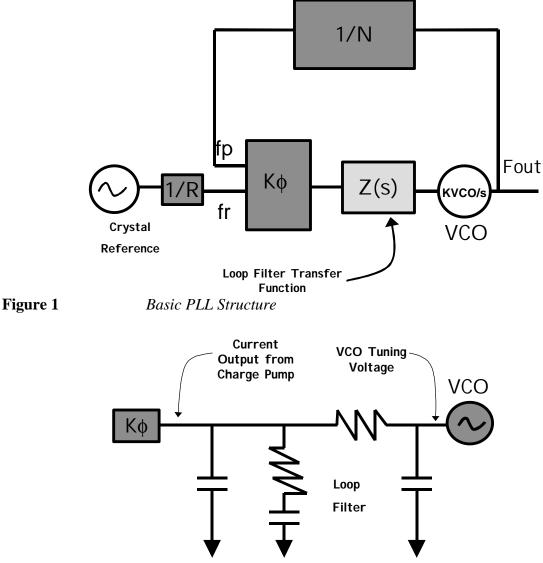

## ii. The Charge Pump PLL with a Passive Loop Filter

## Why this Book Focuses on Charge Pump PLLs

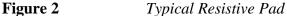

This book is focused primarily on the charge pump PLL, since vast majority of PLLs available in the market today are of this type. The charge pump PLL offers many advantages over the classical voltage phase detector PLL including an infinite pull-in range and zero steady state phase error. Furthermore, there is already a considerable amount of literature that discusses features that are specific only to the voltage phase detector in great depth. By not focusing on the classical voltage phase detector, there is more time to focus on other features of the PLL. The charge pump PLL allows the use of a passive filter while still retaining the benefits of an active filter with the voltage phase detector. Passive filters are generally recommended, because they have the advantages of lower cost and no active devices to add noise. The exception to this case is when the VCO tuning voltage needs to be higher than the charge pump can supply – in this case, an active filter is necessary.

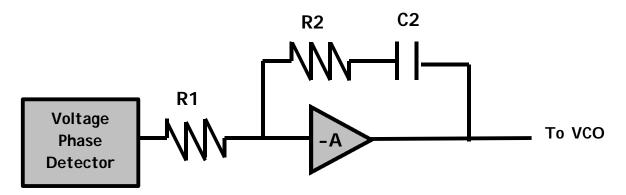

#### The Classical Voltage Phase Detector

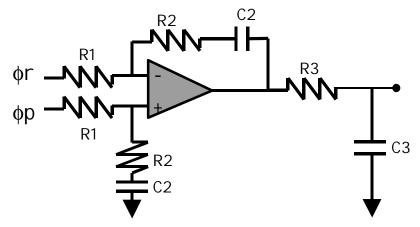

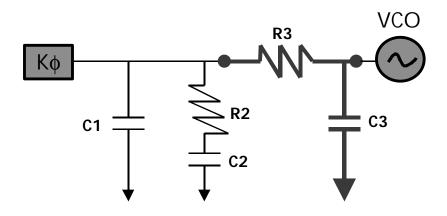

In the past, active filters have been emphasized for several reasons that are explained in depth in Floyd Gardner's classical book, <u>Phaselock Techniques</u>. Many of these concepts still apply to the charge pump PLL, while many others, such as the steady state phase error are quite outdated. The XOR gate and the mixer are both discussed as practical ways to implement a phase detector. In Gardner's book, the following classical active loop filter topology is presented.

Figure 1 Classical Active Loop Filter Topology for a Voltage Phase Detector

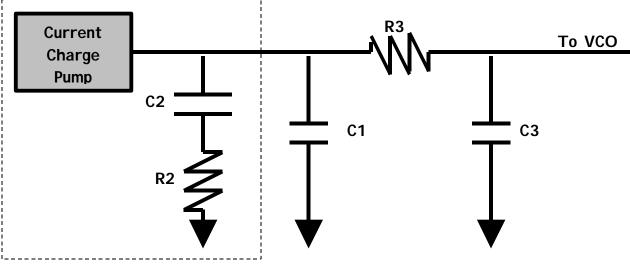

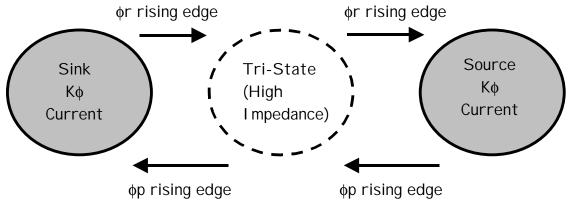

#### The Modern Phase Frequency Detector with Charge Pump and its Advantages

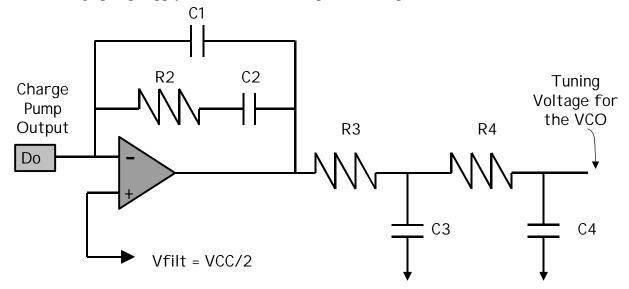

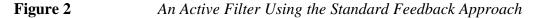

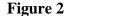

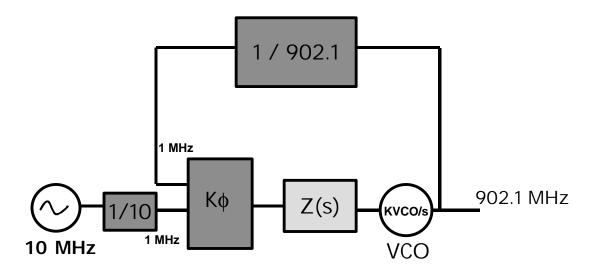

The phase frequency detector with charge pump combination offers several advantages over the voltage charge pump and has all but replaced it. The phase-frequency detector and charge pump are usually integrated on the PLL chip. Using this approach completely eliminates the issues of steady state phase error and hold in range. The PLL with this combination can be compared to its predecessor as is done in Figure 2. Note that the circuit shown below with the box drawn around it integrates the functionality of the op-amp. It is necessary to divide the phase detector voltage gain (in Figure 1) by R1 in order convert the voltage gain to a current gain.

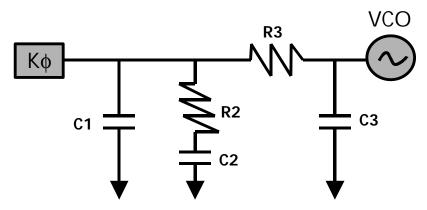

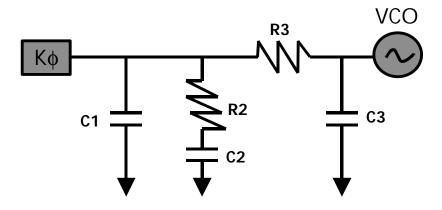

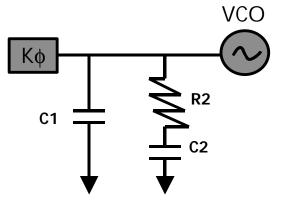

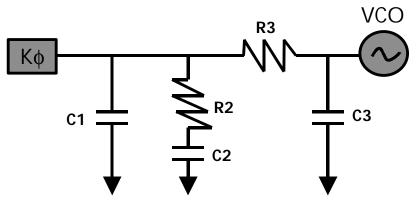

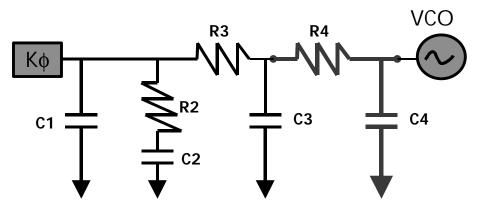

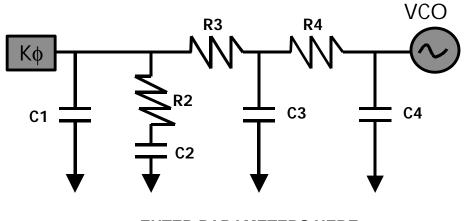

Figure 2Passive Loop Filter with Charge Pump

The capacitor C1 is added, because it reduces the spur levels significantly. Also, the components R3 and C3 can be added in order to further reduce the reference spur levels. Note that this passive filter has the op-amp functionality included. Instead of the phase detector delivering a voltage proportional to the phase error, the charge pump delivers a current with average value proportional to the phase error. This current is actually a constant amplitude with variable duty cycle. It is usually sufficient to model this current as an analog current with the average value proportional to the phase error. This is called the continuous time approximation and is used in most of the chapters in this book.

## iii. The PLL as Viewed from a System Level

## Introduction

This chapter discusses, on a very rudimentary level, how a PLL could be used in a typical wireless application. It also briefly discusses the impact of phase noise, reference spurs, and lock time on system level performance.

## **Typical Wireless Receiver Application**

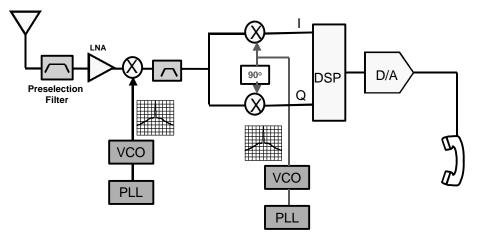

Figure 1Typical PLL Receiver Application

## **General Receiver Description**

In the above diagram, there are several different channels being received at the antenna, each one with a unique frequency. The first PLL in the receiver chain is tuned so that the output from the mixer is a constant frequency. The signal is then easier to filter and deal with since it is a fixed frequency from this point onwards, and because it is also lower in frequency. The second PLL is used to strip the information from the signal. Other than the obvious parameters of a PLL such as cost, size, and current consumption, there are three other parameters that are application specific. These parameters are phase noise, reference spurs, and lock time and are greatly influenced by the loop filter components. For this reason, these performance parameters are not typically specified in a datasheet, unless the exact application, components, and design parameters are known.

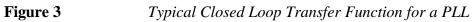

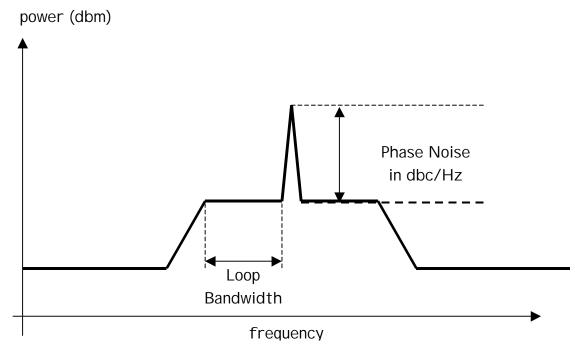

## Phase Noise, Reference Spurs, and Lock Time as They Relate to This System

Phase noise refers to noise generated by the PLL. It can increase the bit error rates and the signal to noise ratio of the system. Reference spurs are unwanted noise sidebands that can occur at multiples of the comparison frequency, and can be translated by a mixer to the desired signal frequency. They can mask or degrade the desired signal. Lock time is the time that it takes for the PLL to change frequencies. It is dependent on the size of the frequency change and what frequency error is considered acceptable. When the PLL is switching frequencies, no data can be transmitted, so lock time of the PLL must lock fast enough as to not slow the data rate. Phase noise, reference spurs, and lock time are discussed in great depth in the rest of this book.

For the receiver shown in Figure 1, the first PLL that is closest to the antenna is typically the most challenging from a design perspective, due to the fact that it is higher frequency and is tunable. Since this PLL is tunable, there is typically a more difficult lock time requirement, which in turn makes it more challenging to meet spur requirements as well. In addition to this, the requirements on this PLL are also typically more strict because the undesired channels are not yet filtered out from the antenna.

The second PLL has less stringent requirements, because it is lower frequency and also it is often not tunable. This makes lock time requirements easier to meet. There is also a trade off between lower spur levels and faster lock times for any PLL. So if the lock time requirements are relaxed, then the reference spur requirements are also easier to meet. Note also that since the signal path coming to the second PLL has already been filtered, the lock time and spur requirements are often less difficult to meet.

#### Conclusion

The PLL is a basic building block that can be used in just about any application where a frequency needs to be synthesized. It is the application that puts restrictions on phase noise, reference spurs, and lock time. These three performance parameters are greatly influenced by many factors including the VCO, loop filter, and N divider value.

## **PLL Performance and Simulation**

## 1. Reference Spurs and their Causes

## Introduction

In PLL frequency synthesis, reference sidebands and spurious outputs are an issue in design. There are several types of these spurious outputs with many different causes. However, by far, the most common type of spur is the reference spur. These spurs appear at multiples of the comparison frequency.

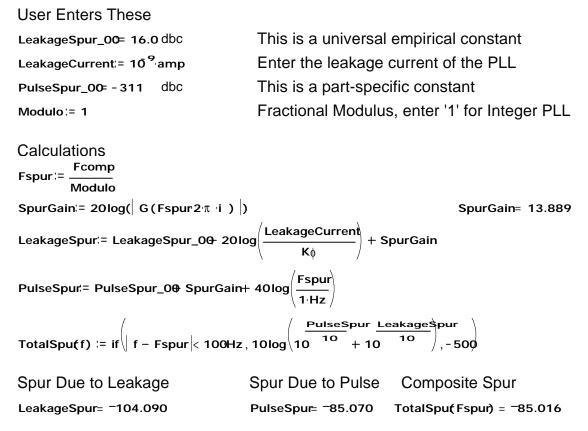

This chapter investigates the causes and behaviors of these reference spurs. In general, spurs are caused by either leakage or mismatch of the charge pump. Depending on the cause of the reference spurs, the spurs may behave differently when the comparison frequency or loop filter is changed. This chapter will discuss how to determine which is the dominant cause for a given application. In order to discuss spur levels, the fundamental concept of spur gain will be introduced. A clear understanding of spur gain is the starting point to understanding how reference spurs will vary from one filter to another. After this concept is developed, leakage and mismatch dominated spurs will be discussed, and then these results will be combined.

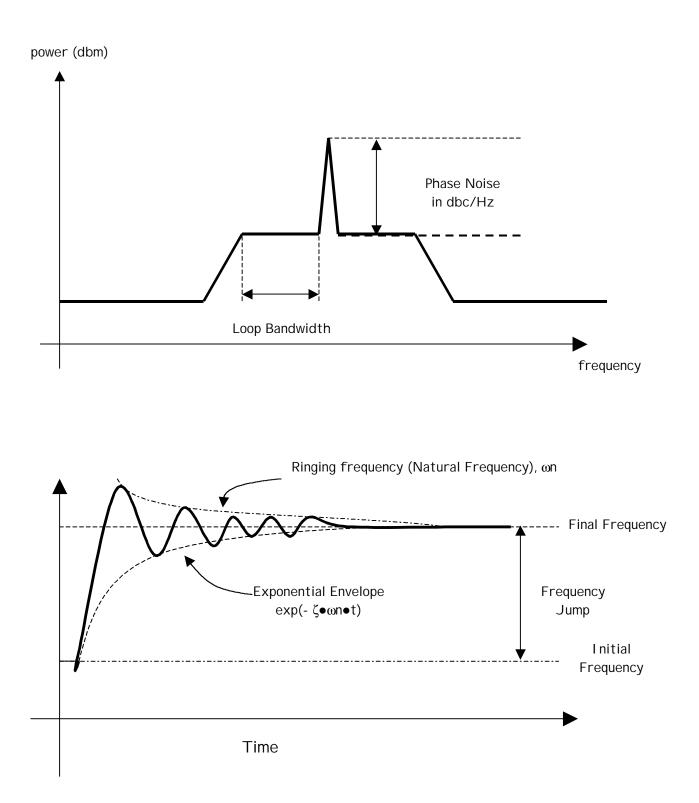

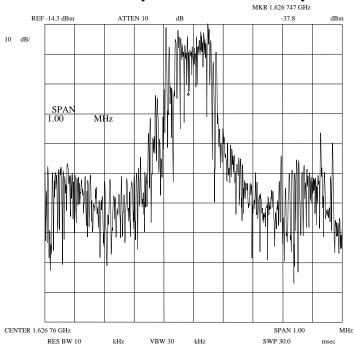

Figure 1Typical Reference Spur Plot

## The Definition of Spur Gain

Conceptually, if a given current noise of a fixed frequency is injected into the loop filter, then the power of the frequency noise that this induces at the VCO would be a start to defining the spur gain. However, an additional factor of 1/s is included in the transfer function to simplify the arithmetic later. Note that since this is a frequency change, it is necessary to multiply the transfer function by a factor of s to convert from phase to frequency. This factor of 1/s is left in, because it turns out that it is reintroduced because of other factors. Furthermore it makes the concept of spur gain a dimensionless quantity. Now since the power of the reference spur is sought, it is necessary to square this gain, and it is finally expressed in decibels for convenience.

Spur Gain (Fspur) =

$$20 \bullet log \left( \left| \frac{K\mathbf{f} \bullet Z(s) \bullet Kvco}{s} \right|_{s=j \bullet Fspur \bullet 2 \bullet \mathbf{p}} \right)$$

So spur gain is the product of the VCO gain, charge pump gain, and loop filter impedance evaluated at a frequency equal to the offset frequency of the spur of interest, *Fspur*. In most cases, *Fspur* will be assumed to be the comparison frequency, *Fcomp*, but it could also be other frequencies, such as multiples of the comparison frequency, or fractions of the comparison frequency (in the case of a fractional N PLL).

Aside from spur gain, there are other factors that contribute to spur levels, depending on whether the spurs are leakage dominated or mismatch dominated. The avid reader might wonder why the open loop transfer function is used, as opposed to the closed loop transfer function. In the case of leakage-dominated spurs, this would make sense, since it is the behavior the charge pump in the off state that causes the spurs. If the charge pump is off, it therefore makes sense to use the open loop transfer function. In the case of a mismatch-dominated spur, it may not be so obvious which transfer function to use. Since the open loop transfer function approximates the closed loop transfer function very well at the reference spurs frequencies, it makes most sense to use the open loop transfer function for the sake of consistency and simplicity.

#### Leakage Dominated Spurs

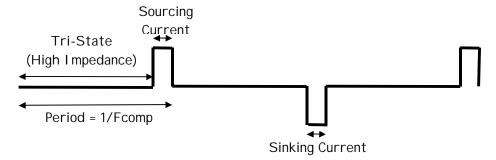

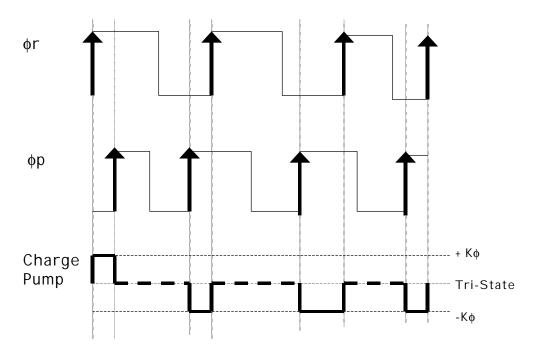

At lower comparison frequencies, leakage effects are the dominant cause of reference spurs. When the PLL is in the locked condition, the charge pump will generate short alternating pulses of current with long periods in between in which the charge pump is tri-stated.

Figure 3 Output of the Charge Pump When the PLL is in the Locked Condition

When the charge pump is in the tri-state state, it is ideally high impedance. However, there will be some parasitic leakage through the charge pump, VCO, and loop filter capacitors. Of these leakage sources, the charge pump tends to be the dominant one. This causes FM modulation on the VCO tuning line, which in turn results in spurs. This is described in greater detail in the appendix.

To predict the reference spur levels based on leakage, use the following general rule:

Leakage Spur = BaseLeakageSpur + 20 •

$$log\left(\frac{Leakage}{K\mathbf{f}}\right)$$

+ Spur Gain

The leakage due to the PLL charge pump is temperature dependent and is often given guaranteed ratings as well as typical ratings and graphs in performance. The leakage of the charge pump increases with temperature, so spurs caused by leakage of the charge pump tend to increase when the PLL is heated.

Various leakage currents were induced at various comparison frequencies, and the results were measured on the bench. The loop filter was not changed during any of these measurements. These results imply the fundamental constant for leakage-dominated spurs:

## BaseLeakageSpur = 16.0 dBc

Note that this constant is universal and not part specific and should apply to any integer PLL. It can also not be stressed enough that it is impossible to directly measure the *BaseLeakageSpur* – this number is extrapolated from other numbers.

| I <sub>leak</sub><br>(nA) | 20●<br>Log<br>(I <sub>leak</sub><br>/Kφ) | Fcomp<br>(KHz) | Filter  | Spur Levels<br>(dBc) |                 | Spur Gain<br>(dB) |                 |                  | Implied<br>BaseLeakage<br>Spur<br>(dbc) |                 |                 |                 |

|---------------------------|------------------------------------------|----------------|---------|----------------------|-----------------|-------------------|-----------------|------------------|-----------------------------------------|-----------------|-----------------|-----------------|

|                           | (dB)                                     |                |         | 1 <sup>st</sup>      | 2 <sup>nd</sup> | 3 <sup>rd</sup>   | 1 <sup>st</sup> | 2 <sup>nd</sup>  | 3 <sup>rd</sup>                         | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> |

| 200                       | -86.0                                    | 50             | А       | -28.3                | -40.5           | -47.3             | 41.7            | 29.7             | 22.7                                    | 16.0            | 15.8            | 16.0            |

| 100                       | -92.0                                    | 50             | А       | -33.8                | -45.7           | -52.7             | 41.7            | 29.7             | 22.7                                    | 16.5            | 16.6            | 16.6            |

| 100                       | -80.0                                    | 100            | В       | -24.3                | -40.5           | -51.5             | 38.8            | 21.9             | 11.6                                    | 16.9            | 17.6            | 16.9            |

| 100                       | -80.0                                    | 200            | В       | -43.5                | -61.5           | -72.0             | 21.9            | 4.2              | -6.3                                    | 14.6            | 14.3            | 14.3            |

| 500                       | -46.0                                    | 400            | С       | -32.7                | Х               | Х                 | -2.4            | Х                | Х                                       | 15.7            | Х               | Х               |

| 200                       | -54.0                                    | 400            | С       | -40.5                | Х               | Х                 | -2.4            | Х                | Х                                       | 15.9            | Х               | Х               |

|                           |                                          |                | Average | e Base L             | eakage          | spur              |                 |                  |                                         | 15.9            | 16.1            | 16.0            |

| Filter                    | Κφ                                       | Kvco           | C1      | C2                   | C3              | R2                | R3              | Output Frequency |                                         |                 |                 |                 |

|                           | (mA)                                     | (MHz/V)        | ) (nF)  | (nF)                 | (pF)            | <b>(Κ</b> Ω)      | <b>(Κ</b> Ω)    | (MHz)            |                                         |                 |                 |                 |

| Α                         | 4.0                                      | 17             | 5.6     | 33                   | 0               | 4.7               | 0               | 900              |                                         |                 |                 |                 |

| В                         | 1.0                                      | 43             | 0.47    | 3.3                  | 90              | 12                | 39              | 1960             |                                         |                 |                 |                 |

| С                         | 0.1                                      | 48             | 1       | 4.7                  | 0               | 18                | 0               |                  |                                         | 870             |                 |                 |

**Table 1** Spur Level vs. Leakage Currents and Comparison Frequency

Note that the *BaseLeakageSpur* index applies to the primary reference spurs as well as higher harmonics of this spur. Appendix B shows a theoretical calculation that is within 4 db of the measured results above. It is recommended that the measured value be used, since the theoretical derivation contains simplifying assumptions and may not account for all factors.

#### **Pulse Related Spurs**

In classical PLL literature, it is customary to model the reference spurs based entirely on leakage currents. For older PLLs, where the leakage currents were in the  $\mu$ A range, this made reasonable estimates for reference spurs and their behavior. However, modern PLLs typically have leakage currents of 1 nA or less, and therefore other factors tend to dominate the spurs, except at low comparison frequencies.

Recall that the charge pump comes on for very short periods of time and then is off during most of the time. It is the length of time that these short charge pump corrections are made that determines the pulse related spur. In other words, if leakage is not the dominant factor, then it is this time that the charge pump is on that determines the spur levels. There are several factors that influence this correction pulse width which include: charge pump mismatches, unequal transistor turn on times, dead-zone elimination circuitry, and inaccuracies in the fractional calibration circuitry. Below is an explanation of how these factors can influence the pulse width.

Mismatch of the charge pump refers to when the sink and source currents of the charge pump are not properly matched. The higher degree of the mismatch, the wider the correction pulse of the phase detector becomes. The unequal transistor turn on times refer to when the PMOS device that sources the current is not matched to the NMOS device that sinks the current. Since the PMOS process is slower, this typically makes it so that the lowest spur levels actually do not occur at 0% mismatch, but closer to about 4% mismatch. The dead zone elimination circuitry is added to keep the PLL out of the dead zone of the phase detector. Around zero phase error, real world issues of gate delays become a factor. To avoid this problem, circuitry can be added to ensure that the charge pump comes on for a minimum amount of time, which in turn impacts spur levels. Inaccuracies in the fractional calibration circuitry can also cause the fractional spurs to appear. All of these above sources increase the width of the charge pump correction pulse, so all of these effects contribute to the pulse spur.

For pulse related spur issues, it is important to be aware of the mismatch properties and to base the design around several different parts to get an idea of the full variations. Mismatch properties of parts can vary from date code to date code, so it is important to consider that in the design process. Also, in designs where an op-amp is used in the loop filter, it is best to use all of the tuning range of the PLL or to center the op-amp around half of the charge pump supply voltage or slightly higher. Due to this variation of spur level over tuning voltage to the VCO, the way that spurs are characterized in this chapter are by the worst case spur when the VCO tuning voltage is varied from 0.5 volts to 0.5 volts below the charge pump supply. The variation can also be mentioned, since this shows how much the spur varies, but ultimately, the worst case spur should be the figure of merit. To predict reference spurs caused by the pulsing action of the charge pump, the following rule applies.

# Pulse Spur = BasePulseSpur + Spur Gain + 40 • $log\left(\frac{Fspur}{1 Hz}\right)$

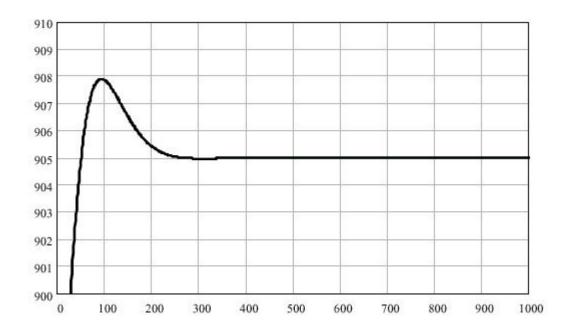

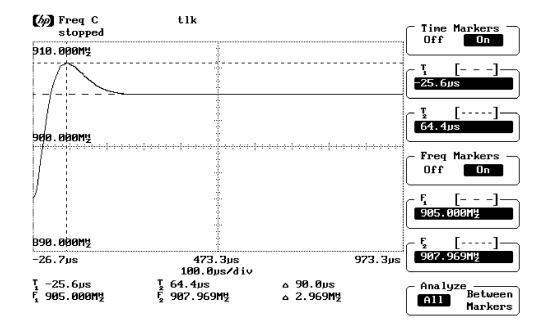

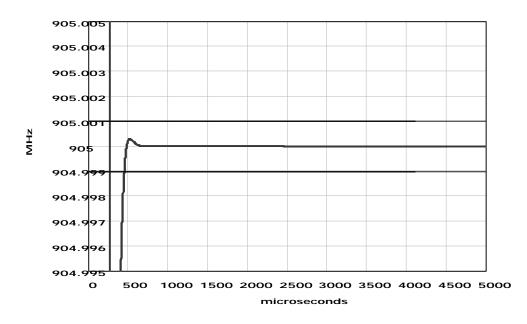

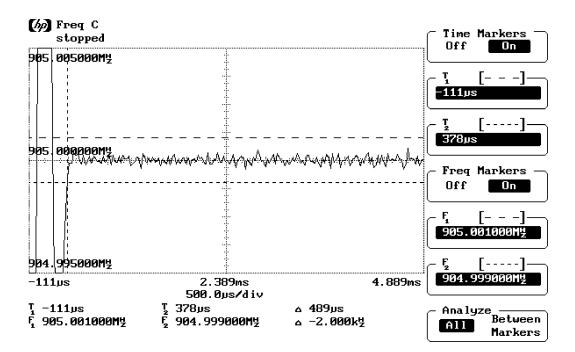

The reader may be surprised to see that the above formula has the additional *Fspur* term added. This was first discovered by making observations with a modulation domain analyzer, which displays frequency versus time. In the case of the leakage-dominated spur, the VCO frequency was assumed to be modulated in a sinusoidal manner, which was confirmed with observations on the bench. However, this was not the case for the pulse-dominated spur. For these, frequency spikes occur a regular intervals of time corresponding to when the charge pump turns on. The pulse-dominated spurs were measured and their magnitude could be directly

correlated to the magnitude of these frequency spikes. This correlation was independent of the comparison frequency. Therefore, using the modulation index concept does not work for pulse dominated spurs and introduces an error equal to  $20 \cdot log(Fspur)$ . However, the pulse spur differs from the leakage spur not by this factor but by  $40 \cdot log(Fspur)$ . The additional factor of  $20 \cdot log(Fspur)$  comes because it is more proper to model the charge pump noise as a train of pulse functions, not a sinusoidal function. Recall to recover the time domain response of a pulse function applied to a system, this is simply the inverse Laplace transform. In a similar way that the inverse Laplace transform of 1/s is just 1, and not involving any factors of 1/w, likewise in this situation, a factor of 1/w is lost for this reason, thus accounting for the additional factor of  $40 \cdot log(Fspur)$ . In the case of the LMX2350/52/54, these are the  $1/16^{\text{th}}$  fractional spurs and have an additional dependence on the output frequency. This is due to the nature of the fractional spur compensation.

| Fout  | Ν         | Fspur      | Kφ      | Кусо      | C1     | C2     | C3     | R2    | R3     | Spur     | Spur      | BasePulse |

|-------|-----------|------------|---------|-----------|--------|--------|--------|-------|--------|----------|-----------|-----------|

|       |           |            |         | MHz       |        |        |        |       |        |          | Gain      | Spur      |

| MHz   |           | KHz        | mA      | /V        | nF     | nF     | рF     | KΩ    | KΩ     | dBc      | dB        | dBc       |

| 1     | This data | was all ta | ken fro | om an LM  | 1X2330 | PLL.   | The V  | CO wa | s near | the high | end of th | he rail.  |

| 1895  | 18950     | 100        | 4       | 43.2      | 2.2    | 10     | 0      | 6.8   | 0      | -51.7    | 46        | -297.7    |

| 1895  | 18950     | 100        | 4       | 43.2      | 13.9   | 66     | 0      | 2.7   | 0      | -69.7    | 30        | -299.7    |

| 1895  | 18950     | 100        | 4       | 43.2      | 0.56   | 2.7    | 0      | 15    | 0      | -41.0    | 58        | -299.0    |

| 1895  | 18950     | 100        | 4       | 43.2      | 1.5    | 6.8    | 0      | 5.6   | 0      | -50.0    | 49.2      | -299.2    |

| 1895  | 18950     | 100        | 4       | 43.2      | 1.5    | 6.8    | 100    | 5.6   | 39     | -59.8    | 40.5      | -300.3    |

| 1895  | 6064      | 312.5      | 4       | 43.2      | 4.7    | 20     | 0      | 1.8   | 0      | -60.2    | 19.6      | -299.6    |

| 1895  | 6064      | 3125.      | 4       | 43.2      | 1.8    | 5.6    | 0      | 1.5   | 0      | -51.1    | 27.7      | -298.6    |

|       | This      | s data was | s taker | n from an | LMX23  | 326 PL | L with | Vtune | = 0.29 | V and V  | cc = 3 V  | /         |

| 231   | 1155      | 200        | 1       | 12        | 0.47   | 3.3    | 0      | 12    | 0      | -74.1    | 23.0      | -309.1    |

| 881.6 | 4408      | 200        | 1       | 18        | 0.47   | 3.3    | 0      | 12    | 0      | -70.1    | 27.6      | -309.7    |

| 881.6 | 1146      | 770        | 1       | 18        | 0.47   | 3.3    | 0      | 12    | 0      | -70.1    | 4.9       | -308.8    |

| 1885  | 9425      | 200        | 1       | 50        | 0.47   | 3.3    | 0      | 12    | 0      | -59.7    | 35.6      | -308.6    |

| 1885  | 4343      | 434        | 1       | 12        | 0.47   | 3.3    | 0      | 12    | 0      | -58.7    | 22.2      | -307.7    |

**Table 2**Demonstration of the Consistency of the BasePulseSpur

The first several rows in Table 2 demonstrate many different filters at the same output frequency. The last several rows use the same filter, but emphasize the difference in changing the N value and comparison frequency. For the last several rows, the charge pump voltage was kept at 0.29 volts to maintain consistent mismatch properties of the charge pump and to also make spurs that were easy to measure. For this reason, this table is a valuable tool to show how spur levels vary. However, it is not a good source of information for worst case *BasePulseSpur*, since the tuning voltage was within 0.5 V of the supply rail and therefore out of specification.

| PLL                       | Variation<br>(dBc) | BasePulseSpur<br>(dBc)    |

|---------------------------|--------------------|---------------------------|

| LMX2301/05, LMX2315/20/25 | 11                 | -299                      |

| LMX2330/31/32/35/36/37    | 23                 | -311                      |

| LMX2306/16/26             | 7                  | -309                      |

| LMX1600/01/02             | 5.0                | -292                      |

| LMX2350/52/54             | 18                 | -257 – 40●log(Fout/1 GHz) |

Table 3

BasePulseSpur for Various National Semiconductor PLLs

Despite the tables and measurements given above, the avid reader is sure to try to relate the pulse related spur to the mismatch of the charge pump. To do this, the LMX2315 PLL was used, and the spur level was measured along with the charge pump mismatch. The spur gain of this system was 19.6 dB, and in this system the comparison frequency was 200 KHz, so the spurs are clearly pulse-dominated.

| Vtune (Volts)      | 1      | 1.5    | 2.2    | 3      | 4      | 4.5    |

|--------------------|--------|--------|--------|--------|--------|--------|

| Source (mA)        | 5.099  | 5.169  | 5.241  | 5.308  | 5.397  | 5.455  |

| Sink (mA)          | 5.308  | 5.253  | 5.166  | 5.047  | 4.828  | 4.517  |

| mismatch (%)       | - 4.0  | - 1.6  | 1.4    | 5.0    | 11.1   | 18.8   |

| 200 KHz Spur (dBc) | - 73.1 | - 76.6 | - 83.3 | - 83.2 | - 72.8 | - 65.7 |

**Table 4**Sample Variation of Spur Levels and Mismatch with Do voltage

Using statistical models, this suggests that the best spur performance is actually when the charge pump is 3.2 % mismatched and also gives the relationship:

BasePulseSpur =  $-315.6 + 1.28 \bullet / \%$ mismatch - 3.2% /

## **Combining the Concepts of Leakage Related Spurs and Pulse Related Spurs**

Critical Values for Comparison Frequency

In most cases, it makes sense to model the spurs as pulse related spurs, but this may not work for low comparison frequencies. One way to determine if a spur is leakage or pulse related is to calculate spurs based on both methods, and use whichever method yields the largest spur levels. In most cases, the pulse related spur will dominate. If the leakage is known, and the *BasePulseSpur* is known, it is possible to predict the comparison frequency for which the spur is equally pulse and leakage dominated. If the comparison frequency is higher than this, then the spur becomes more pulse dominated. Note that this calculation is independent of the spur gain and is found by setting the leakage spur equal to the pulse spur and solving for the comparison frequency. The governing equation and table for this are given below:

$$40 \bullet \log\left(\frac{Fcomp}{1 Hz}\right) = (BaseLeakageSpur - BasePulseSpur) + 20 \bullet \log\left(\frac{leakage}{Kf}\right)$$

Comparison frequencies that satisfy this equation will be called critical frequencies. At the critical frequency, the reference spur is equally dominated by leakage and pulse effects. Above the critical frequency, the spur becomes more pulse dominated, below the critical frequency, the spur becomes more leakage dominated. This table was generated assuming the following:

| BaseLeakageSpur | = | 16.0 dBc |

|-----------------|---|----------|

| K <b>f</b>      | = | 1 mA     |

Note that the critical frequency is proportional to the square root of the leakage current, and inversely proportional to the square root of the charge pump gain.

|                  | BasePulseSpur |                     |        |        |  |  |  |  |

|------------------|---------------|---------------------|--------|--------|--|--|--|--|

|                  | -290          | -290 -300 -310 -320 |        |        |  |  |  |  |

| leakage = 0.1 nA | 14.1          | 25.1                | 44.7   | 79.4   |  |  |  |  |

| leakage = 0.5 nA | 31.6          | 56.2                | 99.9   | 177.6  |  |  |  |  |

| leakage = 1.0 nA | 44.7          | 79.4                | 141.2  | 251.2  |  |  |  |  |

| leakage = 0.1 uA | 446.7         | 794.3               | 1412.5 | 2511.9 |  |  |  |  |

| leakage = 1.0 uA | 1412.5        | 2511.9              | 4466.8 | 7943.3 |  |  |  |  |

#### **Table 5** Critical Values for Comparison Frequency in Kilohertz

#### Composite Spur Calculation

This chapter has independently derived the spur levels based on leakage and pulse effects. However, regardless of the dominant cause, the spur level is given by:

$$Spur = 10 \bullet log \left( 10^{\frac{Leakage Spur}{10}} + 10^{\frac{Pulse Spur}{10}} \right)$$

## Spur Levels vs. Unoptimized Loop Filter Parameters

Using the expression for spur gain, the way that spur levels vary vs. various parameters can easily be calculated and is shown below:

| Relationship to Parameter              | Leakage Dominated<br>Spurs | Pulse Dominated Spurs      |

|----------------------------------------|----------------------------|----------------------------|

| Charge Pump Leakage, i <sub>leak</sub> | 20●log(i <sub>leak</sub> ) | N/A                        |

| Mismatch, M                            | N/A                        | Correlated to   M - δ      |

| N Value, N                             | independent                | independent                |

| VCO Gain, Kvco                         | 20●log(Kvco)               | 20●log(Kvco)               |

| Comparison Frequency                   | -40●log(Fcomp)             | -20●log(Fcomp)             |

| i = Fcomp/Fc                           | -40●log(i)                 | -40•log(i) + 20•log(Fcomp) |

| Charge Pump Gain, K <b>f</b>           | independent                | 20●log(Kø)                 |

| Spur Gain, SG                          | SG                         | SG                         |

**Table 6**Approximate Relationship of Spur Levels to Various Parameters Assuming that<br/>the Loop Filter is NOT Redesigned to Adjust for the Changed Parameter.

## Harmonics of Pulse Dominated Reference Spurs

In the case of a leakage-dominated spur, *BaseLeakageSpur* also applies to the spur harmonics, so this topic has already been covered. However, this case has not been treated in the case of pulse spurs. In order to address this issue, a LMX2326 PLL was tuned in 1 MHz increments from 1900 MHz to 1994 MHz using an automated test program. For these tests, K $\phi$  = 1 mA, Fcomp = 200 KHz, and Kvco = 45 MHz/V. Filter A had components of C1 = 145 pF, C2 = 680 pF, R2 = 33 K $\Omega$ , while Filter B had components of C1 = 315 pF, C2 = 1.8 nF, and R2 = 18 K $\Omega$ . The statistics for the spur levels are presented in Table 7a.

|                         | Fundamental<br>(200 KHz) | 2nd Harmonic<br>(400 KHz) | 3rd Harmonic<br>(600 KHz) |

|-------------------------|--------------------------|---------------------------|---------------------------|

| Minimum (dBc)           | -56.2                    | -65.1                     | -64.5                     |

| Average (dBc)           | -52.8                    | -58.5                     | -61.9                     |

| Maximum (dBc)           | -49.3                    | -54.4                     | -59.0                     |

| Spur Gain for Spur (dB) | 45.7                     | 33.8                      | 26.8                      |

| BasePulseSpur (dBc)     | -307.0                   | -312.4                    | -316.9                    |

|                         | Fundamental<br>(200 KHz) | 2nd Harmonic<br>(400 KHz) | 3rd Harmonic<br>(600 KHz) |

|-------------------------|--------------------------|---------------------------|---------------------------|

| Minimum (dBc)           | -64.8                    | -70.4                     | -69.1                     |

| Average (dBc)           | -60.8                    | -65.1                     | -66.8                     |

| Maximum (dBc)           | -56.2                    | -61.1                     | -64.7                     |

| Spur Gain for Spur (dB) | 39.0                     | 27.1                      | 20.0                      |

| BasePulseSpur (dBc)     | -307.2                   | -312.2                    | -315.8                    |

## **Table 7b**Reference Spurs and their Harmonics for Filter B

Table 7a to Table 7b show that the pulse spur is relatively consistent for different filters, however the second harmonic has a different BasePulseSpur than the first. These empirical measurements would suggest to expect that the BasePulseSpur for the second harmonic to be about 5 dB better than the BasePulseSpur for the first harmonic, and for the BasePulseSpur of the third harmonic to be about 4 dB better than the BasePulseSpur for the second harmonic.

Now Tables 7a and 7b show harmonics of pulse dominated reference spurs. Similar measurements can also be made for harmonics of leakage-dominated spurs. Theoretically, one would expect that the higher harmonics to behave differently than the fundamental leakage dominated spur, since they are based on the higher powers of the modulation index (See Appendix A), however measured results show that they can be treated just as the fundamental leakage spur, except for the value of BaseLeakageSpur for them is a little different.

|                         | Fundamental<br>(200 KHz) | 2nd Harmonic<br>(400 KHz) | 3rd Harmonic<br>(600 KHz) |

|-------------------------|--------------------------|---------------------------|---------------------------|

| Minimum (dBc)           | -56.2                    | -65.1                     | -64.5                     |

| Average (dBc)           | -52.8                    | -58.5                     | -61.9                     |

| Maximum (dBc)           | -49.3                    | -54.4                     | -59.0                     |

| Spur Gain for Spur (dB) | 45.7                     | 33.8                      | 26.8                      |

| BasePulseSpur (dBc)     | -307.0                   | -312.4                    | -316.9                    |

| Table 7a | <b>Reference</b> Spurs | and their Harm | onics for Filter A |

|----------|------------------------|----------------|--------------------|

|----------|------------------------|----------------|--------------------|

#### Conclusion

This chapter has discussed the causes of reference spurs and given some techniques to simulate their general behavior. The concept of spur gain applies to reference spurs and gives a relative indication of how they vary from one loop filter to another when the other parameters, such as comparison frequency are held constant. Reference spurs can be caused by leakage or pulse effects. Pulse effects is a generic term to refer to inconsistencies in the pulse width of the charge pump caused by mismatch, unequal transistor turn on times, or imperfections in the fractional N compensation circuitry. Although reference spurs are intended to refer to spurs that

appear at a spacing equal to the comparison frequency from the carrier, the models in this chapter are also useful in predicting harmonics of reference spurs and fractional spurs. One caution dealing with fractional spurs is they may be sensitive to voltage and prescaler. They also often have a dependence on the output frequency as well. In general, the spur that is closest to the carrier is the most troublesome, since it is most difficult to filter.

As for the accuracy of the formulas presented in this chapter, there will always be some variation between the actual measured result and the theoretical results. Relative comparisons using spur gain tend to be the most accurate. In the case of leakage-dominated spurs, there is a discrepancy between the theoretical and empirical values for **BaseLeakageSpur** of about 4 db. It is recommended to use the empirical value, but to accept that there could be several dB variation between the predicted and measured results. In the case of pulse-dominated spurs, the value for **BasePulseSpur** is purely empirical and is based solely on measured data. These spurs can also change a good 15 dB as the VCO is tuned across its tuning range. However, the worst case spur is the one that is being modeled.

## **Appendix A: Spectra of Spurious Signals**

## Introduction

This section investigates the causes of spurs and their spectral density for an arbitrary time-varying signal that is fed to a VCO. It assumes a sinusoidal signal and is therefore meaningful in analyzing leakage-dominated spurs.

#### **Derivation of Spurious Spectrum**

Spurs are caused by the PLL when a signal with an AC component is presented to the tuning line of the VCO. Assume that the tuning voltage to the VCO has the form:

$$V_{tune} = V_{DC} + V_{AC}(t)$$

Where

| $V_{tune}$     | = | Tuning voltage to the VCO                   |

|----------------|---|---------------------------------------------|

| $V_{DC}$       | = | DC component of tuning voltage to the VCO   |

| $V_{AC}$       | = | AC component of tuning voltage to the VCO   |

|                |   | $= V_m \bullet sin(\mathbf{w}_m \bullet t)$ |

| ω <sub>m</sub> | = | Modulating Frequency = <i>Fcomp</i>         |

The VCO has an output voltage of the form [1]:

$$V(t) = A \bullet cos[\mathbf{w}_0 \bullet t + \mathbf{b} \bullet sin(\mathbf{w}_m \bullet t)]$$

Where

| W0 | = | Carrier Frequency |

|----|---|-------------------|

| b  | = | Modulation Index  |

Since **b**•*sin*( $\mathbf{w}_n \bullet t$ ), represents the phase deviation of the signal, this expression can be differentiated to determine the maximum frequency deviation, **D***F*, and the following identity can be derived [1]:

$$\boldsymbol{b} = \frac{\boldsymbol{D}F}{\boldsymbol{w}_n}$$

By writing down the Fourier Series for  $e^{j \cdot b \cdot sin(w_n \cdot t)}$  the following identity can be derived [1].

$$e^{j \bullet \boldsymbol{b} \bullet sin(\boldsymbol{w}_n \bullet t)} = \sum_{n=-\infty}^{\infty} J_n(\boldsymbol{b}) \bullet e^{j \bullet n \bullet \boldsymbol{w}_m \bullet t}$$

In the above expression,  $J_n(\mathbf{b})$  is the Bessel function of the first kind of order n.

Applying the identity allows the power spectral density to be simplified as follows [1].

$$Vout(t) = A \cdot cos[\mathbf{w}_0 \cdot t + \mathbf{b} \cdot sin(\mathbf{w}_m \cdot t)]$$

=  $A \cdot Re al \left\{ e^{j \cdot \mathbf{w}_0 \cdot t} \sum_{n=-\infty}^{\infty} J_n(\mathbf{b}) \cdot e^{j \cdot n \cdot \mathbf{w}_m \cdot t} \right\}$

=  $A \cdot \sum_{n=-\infty}^{\infty} J_n(\mathbf{b}) \cdot cos(\mathbf{w}_0 \cdot t + n \cdot \mathbf{w}_m \cdot t)$

From this expression, the sideband levels can be found by visual inspection.

Carrier :

$$J_0(\mathbf{b}) \approx 1$$

First :  $J_1(\mathbf{b}) \approx \frac{\mathbf{b}}{2}$

Second :  $J_2(\mathbf{b}) \approx \frac{\mathbf{b}^2}{8}$

$n^{th}$  :  $J_n(\mathbf{b})$

Below is a table of first sideband level versus frequency deviation from zero for various comparison frequencies:

| Spur<br>Level | Modulation<br>Index | Frequency Deviation for Various Comparison Frequencies (H |                 |                 |                  |                  |                   |

|---------------|---------------------|-----------------------------------------------------------|-----------------|-----------------|------------------|------------------|-------------------|

| (dBm) (β)     |                     | Fcomp<br>10 KHz                                           | Fcomp<br>30 KHz | Fcomp<br>50 KHz | Fcomp<br>100 KHz | Fcomp<br>200 KHz | Fcomp<br>1000 KHz |

| -30           | 6.32e-2             | 632                                                       | 1900            | 3160            | 6320             | 12600            | 63200             |

| -40           | 2.00e-2             | 200                                                       | 600             | 1000            | 2000             | 4000             | 20000             |

| -50           | 6.32e-3             | 63                                                        | 190             | 316             | 632              | 1260             | 6320              |

| -55           | 3.56e-3             | 36                                                        | 107             | 178             | 356              | 712              | 3560              |

| -60           | 2.00e-3             | 20                                                        | 60              | 100             | 200              | 400              | 2000              |

| -65           | 1.12e-3             | 11                                                        | 34              | 56              | 112              | 224              | 1120              |

| -70           | 6.32e-4             | 6                                                         | 19              | 32              | 63               | 126              | 632               |

| -75           | 3.56e-4             | 4                                                         | 11              | 18              | 36               | 71               | 356               |

| -80           | 2.00e-4             | 2                                                         | 6               | 10              | 20               | 40               | 200               |

| -85           | 1.12e-4             | 1                                                         | 3               | 6               | 11               | 22               | 112               |

| -90           | 6.32e-5             | 0.6                                                       | 2               | 3               | 6                | 13               | 63                |

**Table 7** Relationship Between Spur Level, Modulation Index, and Frequency Variation

The spur levels relate the modulation index by:

Spur Level =

$$20 \bullet log(b/2)$$

## References

[1] Tranter, W.H. and R.E. Ziemer *Principles of Communications Systems, Modulation, and Noise*, 2<sup>nd</sup> ed, Houghton Mifflin Company, 1985

## **Appendix B: Theoretical Calculation of Leakage Based Spurs**

Since the *BaseLeakageSpur* is theoretically independent of PLL and loop filter, it makes sense to choose the loop filter that is the most basic. A simple capacitor is the most basic loop filter. Note that this filter topology is not a stable one, but for the purposes of this calculation, it will do just fine. Using this simplified loop filter, the voltage deviation to the VCO can easily be calculated.

$$\frac{DV}{Dt} = \frac{i}{C1}$$

Substituting in known values gives the voltage deviation.

$$\mathbf{D}V = \int_{0}^{1/F_{comp}} \frac{i}{C1} \bullet dt = \frac{i}{C1 \bullet Fcomp}$$

Now recall that this is the amount the voltage changes during one charge pump cycle. So to get the modulation index, it is necessary to divide by two. Therefore, the modulation index is:

$$\boldsymbol{b} = \frac{Kvco \bullet \boldsymbol{D}V}{2 \bullet Fcomp}$$

Leakage Spur =  $20 \bullet \log\left(\frac{\boldsymbol{b}}{2}\right)$

Table 8 shows the fundamental result and how it can be derived. This number is within a few dB of what has been measured in practice.

| Specified | Quantities | Derived Quantities                                       |                                  |  |

|-----------|------------|----------------------------------------------------------|----------------------------------|--|

| C1        | 10 nF      | Spur Gain 8.073 dB                                       |                                  |  |

| C2        | 0 nF       | DV                                                       | 1.000 μV                         |  |

| R2        | 0 KΩ       | <b>b</b> = modulation index 0.00005                      |                                  |  |

| Kf        | 1 mA       | <i>Leakage Spur</i> = $20 \cdot \log(\beta/2) = -92.041$ |                                  |  |

| Кисо      | 10 MHz/V   | 20●(Leakage/K <b>f</b> )                                 | -120.000                         |  |

| Leakage   | 1 nA       |                                                          | = -92.0 dBc - (-120 dB) - 8.1 dB |  |

| Fcomp     | 100 KHz    | BaseLeakageSpur                                          |                                  |  |

|           |            |                                                          | = 19.886 dBc                     |  |

**Table 8**Theoretical calculation for BaseLeakageSpur = 19.9 dBc/Hz

## 2. On Non-Reference Spurs and their Causes

## Introduction

Much has been said about reference spurs, which occur at the reference frequency away from the carrier. This chapter investigates other types of spurs and their causes. The value of doing this is so that when a spur is seen, its causes and fixes can be investigated. Although many types of spurs are listed, most of these spurs are not usually present. Since a lot of these spurs occur in dual PLLs, the main PLL will always refer to the side of a dual PLL on which the spur is being observed, and the auxiliary PLL will refer to the side of a dual PLL that is not being observed. This chapter discusses general good tips for dealing with spurs, and then goes into categorizing the most common types, their causes, and their cures.

## **Tips for Good Decoupling and Good Layout**

To deal with board-related cross talk, there are several steps that can be taken. Be sure to visit wireless.national.com and download the evaluation board instructions to see typical board layouts. In addition to this, there are the following additional suggestions:

**Good Decoupling:** By this it is meant to have several capacitors on both the VCC and charge pump supply lines. The charge pump supply lines are the most vulnerable to noisy signals. Place a 100 pF, 0.01  $\mu$ F, and a 0.1  $\mu$ F capacitor on each of these lines to deal with noise at a wide range of frequencies. It may seem that these capacitances simply add in parallel to form a 0.111  $\mu$ F capacitor, but in fact, they are all necessary since the larger capacitors have more problems responding to high frequency signals and may have a higher ESR. It is also good to place these components as close to the PLL chip as possible. Also it is often good to isolate the power supply pins with a small resistor of about 18  $\Omega$ .

*Good Layout:* Be sure to protect the charge pump supply lines and the VCO tuning voltage lines from noisy signals. This can be done by making these traces short and as close as possible to the PLL chip. When two high frequency traces must be placed together, try to make them so that they are not parallel (i.e. try to make them perpendicular) in order to minimize the cross talk effects. Also try to minimize ground looping, which occurs when there is a small impedance (such as the inductance caused by a via) that connects two traces to ground. In the instance of ground looping noise can travel from one trace to another. Placing a ground plane in the board to separate the top and bottom layer also can help reduce cross talk effects.

*Good Loop Filter Design:* Higher order loop filters and filters with narrower loop bandwidth are more effective in reducing spurs of all sorts – not just reference spurs.

## Cross Talk vs. Non-Cross Talk Related Spurs

For the purposes of this discussion, the spurs will be divided into two categories. Cross talk related spurs refer to any spur that is caused by some source other than the PLL that finds its way to VCO output. Non-cross talk related spurs refer to spurs that are caused by some inherent behavior in the PLL. The first step in diagnosing a spur is to determine whether or not it is a cross talk related spur. The way that this is done is by eliminating all potential causes of the cross talk spur and checking if the spur goes away.

## **Cross Talk Related Spurs**

In general, signals that are either low frequency, or close to the PLL output frequency are the most likely to cause this type of spurs. Whenever two sinusoidal signals enter a non-linear device an output signal at the sum and the difference of these frequencies will be produced. This result can be derived by writing the first three general terms for the Taylor series and observing that the square term gives rise to these sum and difference frequencies. It therefore follows that frequencies that are low in frequency, or frequencies that are close to the PLL output frequency are the ones that cause the most problems with cross talk related spurs. Several different types of the cross talk related spur are given below:

## **External Cross Talk Spur**

*Description:* This spur appears and is unrelated to the auxiliary PLL output. Often times, when the main PLL is tuned to different frequencies, this spur moves around.

*Cause:* This type of spur is caused by some frequency source external to the PLL. Common external sources that can cause these spurs are: computer monitors (commonly causes spurs at the screen refresh rate of 30 - 50 KHz), phones of all sorts, other components on the board, florescent lights, power supply (commonly causes spurs in multiples of 60 Hz), and computers. Long signal traces can act as an antenna and agitate this type of spur.

*Diagnosis:* To diagnose this spur, start isolating the PLL from all potential external noise sources. Switch power supplies. Turn off computer monitors. Go to a screen room. Disconnect the auxiliary VCO and power down the auxiliary PLL. By trial and error, external noise sources can be ruled out, one by one.

*Cure:* To eliminate this spur, remove or isolate the PLL from the noise source. As usual, these spurs are layout dependent, so be sure to read the section on good layout. Also consider using RF fences to isolate the PLL from potential noise sources.

## Auxiliary PLL Cross Talk Spur

**Description:** This spur only occurs in dual PLLs and is seen at a frequency spacing from the carrier equal to the difference of the frequencies of the main and auxiliary PLL (or sometimes a higher harmonic of the auxiliary PLL). This spur is most likely to occur if the main and auxiliary sides of a dual PLL are close in frequency. If the auxiliary PLL is powered down, but the auxiliary VCO is running, then this spur can dance around the spectrum as the auxiliary frequency VCO drifts around.

*Cause:* Parasitic capacitances on the board can allow high frequency signals to travel from one trace on the board to another. This happens most for higher frequencies and longer traces. There could also be cross talk within the chip. The charge pump supply pins are vulnerable to high frequency noise.

**Diagnosis:** One of the best ways to diagnose this spur is to tune the auxiliary side of the PLL while observing the main side. If the spur moves around, that is a good indication that the spur being observed is of this type. Once this type of spur is diagnosed, then it needs to be determined if the spur is related to cross talk on the board, or cross talk in the PLL. Most PLLs

have a power down function that allow one to power down the auxiliary side of a PLL, while keeping the main side running. If the auxiliary side of the PLL is powered down, and the spur reduces in size substantially, this indicates cross talk in the PLL chip. If the spur stays about the same magnitude, then this indicates that there is cross talk in the board.

*Cure:* Read the section on how to deal with board related cross talk.

## **Crystal Reference Cross Talk Spur**

**Description:** This spur is visible at an offset from the carrier equal to some multiple of the crystal reference frequency. Often times, there is a whole family of spurs that often occur at harmonics of the crystal reference frequency. In this case, the odd harmonics are usually stronger than the even harmonics.

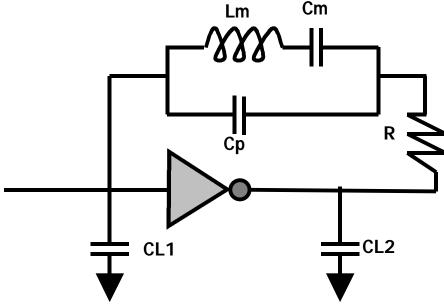

**Cause:** This spur can be caused by excessive gain of the inverter in the crystal oscillator. Sometimes, this inverter is integrated unto the PLL chip. When any oscillator has excessive gain, it can give rise to harmonics. The reason that the odd harmonics are often stronger is that the oscillator often produces a square wave or a clipped sine wave, which has stronger odd harmonics. Figure 1 shows a the structure of a typical crystal oscillator. Note that Lm (motional inductance), Cm (motional capacitance), and Cp (parallel capacitance) represent the circuit equivalent of a quartz crystal.

Figure 1A Typical Crystal Oscillator Circuit

**Diagnosis:** The best way to diagnose this spur is to use a signal generator in place of the crystal. If spur level is impacted, then this is an indication that the oscillator inverter has excessive gain. Note that on some of National Semiconductor's PLLs, the inverting buffer is included on the PLL chip, while on others, it is not. If the power level to the chip is reduced, then this decreases the gain of the buffer, which theoretically should decrease the level of this type of spur.

*Cure:* In addition to the suggestions about good decoupling and layout, there are several things that may reduce these spur levels

*1. Decrease the gain of the inverting buffer*

This may sound sort of ridiculous at first, but if the part is run at a lower VCC power supply voltage, then the gain of the inverter is decreased. Also, some of National Semiconductor's PLLs, such as the LMX160x family have only a single inverter stage as opposed to a triple inverter stage.

2. Supply an external inverter

Using a separate inverter for the crystal, or using the inverter from some other component, such as the microprocessor could also be a fix.

*3. Increase the value of the Resistor, R*

In the above diagram, increasing the value of R can account a little bit for the excessive inverter gain. If R is increased too much, the circuit simply will not oscillate. Note that in many inverter circuits  $R = 0 \Omega$ .

4. Try unequal load capacitors

Usually, the load capacitors, CL1, and CL2 are chosen to be equal, but in this case it might improve the spur level to make CL2 > CL1. This is because the output of the inverter is a square wave, so anything to round out the edges can help.

5. Layout and filtering

Be sure to read the layout tips and also consider filtering the noisy signal on the board.

## **Non-Cross talk Related Spurs**

These spurs are caused by something other than cross talk on the board. Some common examples are discussed below:

## **Fractional N Spurs**

**Description:** These spurs only occur with a fractional N PLL. They occur at multiples of the fractional modulus M. For instance, if there was a fractional N PLL with N = 915.2, and a comparison frequency of 1 MHz, there could potentially be spurs at 200 KHz ( $1/5^{th}$  fractional spur), 400 KHz ( $2/5^{th}$  fractional spur), 600 KHz ( $3/5^{th}$  fractional spur), 800 KHz ( $4/5^{th}$  fractional spur), and 1 MHz (main spur) from the carrier. If the fraction is N/M, then the k<sup>th</sup> fractional spur will be present if the greatest common multiple of M and N divide k. For instance, if a PLL is run in the 2/16 mode, spurs will appear at  $1/8^{th}$ ,  $1/4^{th}$ ,  $3/8^{th}$ , ..., and  $7/8^{th}$  of the comparison frequency. Furthermore, the k<sup>th</sup> fractional spur is most severe when N=k. If N and M are relatively prime, all fractional spurs will be present.

Consider a PLL used in modulo 8 mode. When the fraction is 1/8, all fractional spurs will be present. When the fraction is 2/8, only the even fractional spurs will be present, and the 2/8 fractional spur in this mode will be the worst case for the second fractional spur. When the fraction is 3/8 mode, all fractional spurs will be there and this is the worst case for the third fractional spur. In the 4/8 mode, only the 4/8 and main spur will be present, and this will be the worst case for the fourth fractional spur.

*Cause:* In any fractional N PLL, fractional N averaging is employed. Fractional N averaging involves switching the N counter value between two different values. This gives rise to fractional spurs due to an instantaneous phase error introduced by the fractional N averaging.

For this reason, compensation circuitry is included on the chip to account for this instantaneous phase error. Since this circuitry is not perfect, there will usually be fractional N spurs on any sort of fractional PLL.

*Diagnosis:* These spurs are easy to identify because they occur at the fractional modulus times the comparison frequency from the carrier and are very dependent on the fractional modulus.

*Cure:* Fractional N parts have a lot of part-specific spur causes, but the spurs are all a result of imperfections in the fractional compensation circuitry. They can be dependent on supply voltage, output frequency, and a lot of other attributes that one would normally not suspect. If there is flexibility in adjusting the power supply voltage, then this provides one degree of freedom. For instance, the LMX2350 PLL has lowest fractional spurs around 3.3 V of operation. The other way to deal with these fractional spurs is to use a different fractional N part, since they are specific to each family of fractional N parts. If the second or higher fractional spur is a trouble causer, then using fractional modulus is odd or prime can help, since this will improve the worst case scenario for the second spur.

## **Greatest Common Multiple Spur**

**Description:** This spur occurs in a dual PLL at the greatest common multiple of the two comparison frequencies. For example, if one side was running with a 25 KHz comparison frequency, and the other side was running with a 30 KHz comparison frequency, then this spur would appear at 5 KHz. In some cases, this spur can be larger on certain output frequencies.

*Cause:* The reason that this spur occurs is that the greatest common multiple of the two comparison frequencies corresponds to the event that both charge pumps come on at the same time. This result can be derived by considering the periods of the two comparison frequencies. When both charge pumps come on, they produce noise, especially at the charge pump supply pins, which gives birth to this spur.

**Diagnosis:** A couple telltale signs of this type of spur is it is always spaced the same distance from the carrier, regardless of output frequency. However, keeping the output frequency the same, but changing the comparison frequency causes this spur to move around. Just be sure that when changing the comparison frequencies for diagnostic purposes, you are also changing the greatest common multiple of the two comparison frequencies.

*Cure:* This spur can be treated effectively by putting more capacitors on the Vcc and charge pump supply lines. Be sure that there is good layout and decoupling around these pins. Also consider changing the comparison frequency of the auxiliary PLL.

## **Phantom Reference Spur**

**Description:** The phantom reference spur is characterized by a ghastly increase in the reference spurs right after switching frequencies. After the frequency is changed, it takes an excessively long time for the reference spurs to settle down. This spur is more common at lower comparison frequencies.

*Cause:* Some of this can be possibly explained by deceptive measurements from the equipment, such as using the video averaging function on a spectrum analyzer. It can also be caused by leaky capacitors in the loop filter. Other theories suggest that it is related to undesired effects from the loop filter capacitors, such as dielectric absorption.

**Diagnosis:** This can be observed on a spectrum analyzer. Just be very careful that it is not some sort of averaging effect of the spectrum analyzer. The output of the spectrum analyzer is power vs. frequency, which is really intended to be a still time sort of measurement. It may be helpful to test the equipment measuring some other spur to make sure that this is really the PLL and not the equipment.

*Cure:* Designing with higher quality capacitors helps a lot. In particular, the capacitor C2 tends to be the culprit for causing this spur. Common capacitor types listed in order of improving dielectric properties are: tantalum, X7R, NPO, and polypropeline. Also, using a fractional N PLL can possibly help, since the fractional spurs tend to be less leakage dominated.

## **Prescaler Miscounting Spur**

**Description:** This spur typically occurs at half the comparison frequency. However, it can also occur at one-third, two-thirds, or some fractional multiple of the comparison frequency. It can have mysterious attributes, such only occurring on odd channels.

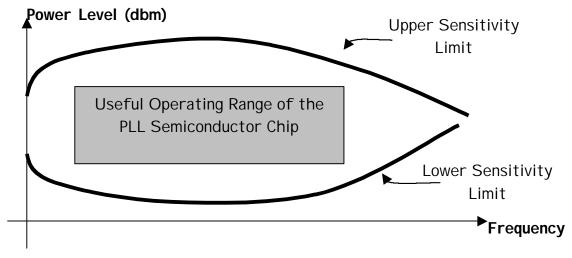

*Cause:* This spur is caused by the prescaler miscounting. Things that cause the prescaler to miscount include poor matching to the high frequency input pin, violation of sensitivity specifications for the PLL, and VCO harmonics. Be very aware that although it may seem that the sensitivity requirement for the PLL is being met, poor matching can still agitate sensitivity problems and VCO harmonic problems. Note also that there is an upper sensitivity limitation on the part.

To understand why the prescaler miscounting causes spurs, consider fractional N averaging. Since the prescaler is skipping counts on some occasions and not skipping counts on another, it produces spurs similar to fractional spurs.

*Diagnosis:* Since miscounting ties in one way or another to sensitivity, try varying the voltage and/or temperature conditions for the PLL. Since sensitivity is dependent on these parameters, any dependency to supply voltage or temperature point to prescaler miscounting as the cause of the spur. Changing the N counter between even and odd values can also sometimes have an impact on this type of spur caused by the N counter miscounting, and can be used as a diagnostic tool.

Also be aware that R counter sensitivity problems can cause this spur as well. One way to diagnose R counter miscounting is to change the R counter value just slightly. If the spur seems sensitive to this, then this may be the cause. If a signal generator is connected to the reference input, and the spur mysteriously disappears, then this suggests that the R counter miscounting is the cause of the spur.

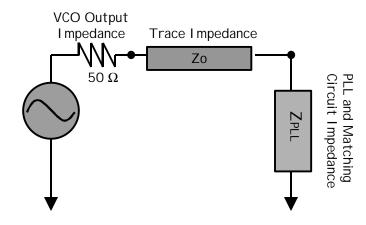

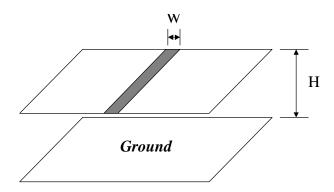

*Cure:* To cure this problem, it is necessary to fix whatever problem is causing the prescaler to miscount. The first thing to check is that the power level is within the specifications of the part. After that, consider the input impedance of the PLL. For many PLLs, this tends to be capacitive. Putting an inductor to match the imaginary part of the PLL input impedance at the operating frequency can usually fix impedance matching issues. Be also aware of the sensitivity and matching to the VCO harmonics, since they can also cause a miscount. Try to keep the VCO harmonics -20 dBm or lower in order to reduce the chance of the PLL miscounting the VCO harmonic.

## VCO Harmonic Spurs