## **Fundamental Characteristics of Thyristors**

#### Introduction

Expertise Applied Answers Delivered

The Thyristor family of semiconductors consists of several very useful devices. The most widely used of this family are silicon controlled rectifiers (SCRs), Triacs, SIDACs, and DIACs. In many applications these devices perform key functions and are real assets in meeting environmental, speed, and reliability specifications which their electromechanical counterparts cannot fulfill.

This application note presents the basic fundamentals of SCR, Triac, SIDAC, and DIAC Thyristors so the user understands how they differ in characteristics and parameters from their electro-mechanical counterparts. Also, Thyristor terminology is defined.

#### SCR

#### **Basic Operation**

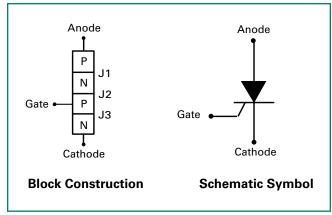

Figure AN1001.1 shows the simple block construction of an SCR.

Figure AN1001.1 SCR Block Construction

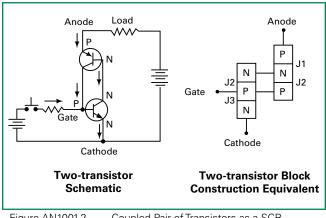

The operation of a PNPN device can best be visualized as a specially coupled pair of transistors as shown in Figure AN1001.2.

Figure AN1001.2 Coupled Pair of Transistors as a SCR

The connections between the two transistors trigger the occurrence of regenerative action when a proper gate signal is applied to the base of the NPN transistor. Normal leakage current is so low that the combined h<sub>EE</sub> of the specially coupled two-transistor feedback amplifier is less than unity, thus keeping the circuit in an off-state condition. A momentary positive pulse applied to the gate biases the NPN transistor into conduction which, in turn, biases the PNP transistor into conduction. The effective  $h_{\text{ee}}$  momentarily becomes greater than unity so that the specially coupled transistors saturate. Once saturated, current through the transistors is enough to keep the combined h<sub>FF</sub> greater than unity. The circuit remains "on" until it is "turned off" by reducing the anode-to-cathode current (I\_{\_{T}}) so that the combined  $h_{_{\text{FF}}}$  is less than unity and regeneration ceases. This threshold anode current is the holding current of the SCR.

#### **Geometric Construction**

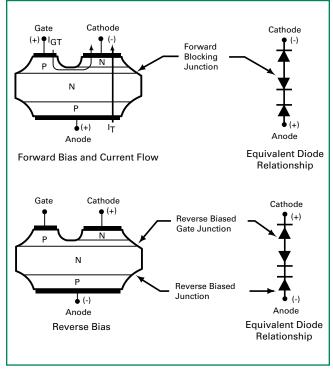

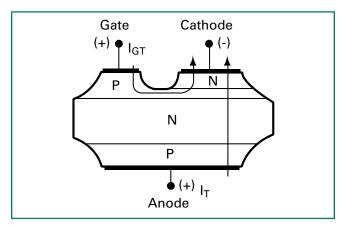

Figure AN1001.3 shows cross-sectional views of an SCR chip and illustrations of current flow and junction biasing in both the blocking and triggering modes.

Figure AN1001.3 Cross-sectional View of SCR Chip

Specifications are subject to change without notice. Please refer to http://www.littelfuse.com for current information

#### Triac

#### **Basic Operation**

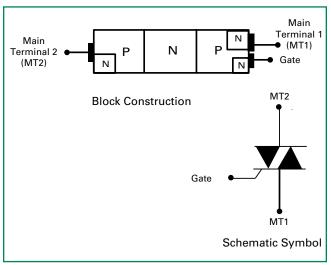

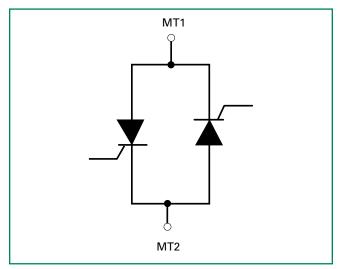

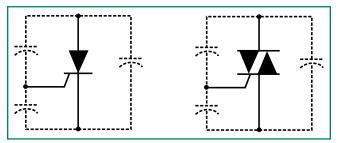

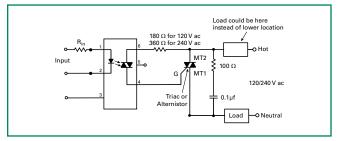

Figure AN1001.4 shows the simple block construction of a Triac. Its primary function is to control power bilaterally in an AC circuit.

Figure AN1001.4 Triac Block Construction

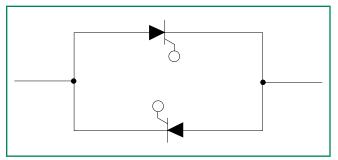

Operation of a Triac can be related to two SCRs connected in parallel in opposite directions as shown in Figure AN1001.5.

Although the gates are shown separately for each SCR, a Triac has a single gate and can be triggered by either polarity.

Figure AN1001.5 SCRs Connected as a Triac

Since a Triac operates in both directions, it behaves essentially the same in either direction as an SCR would behave in the forward direction (blocking or operating).

#### **Geometric Construction**

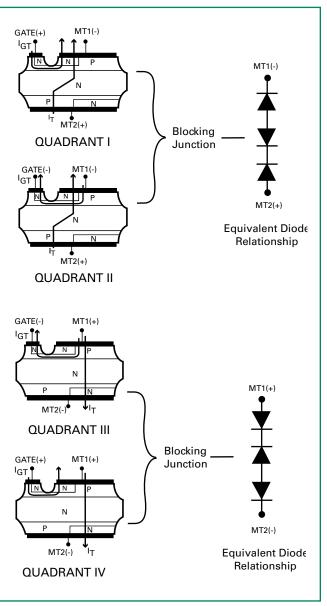

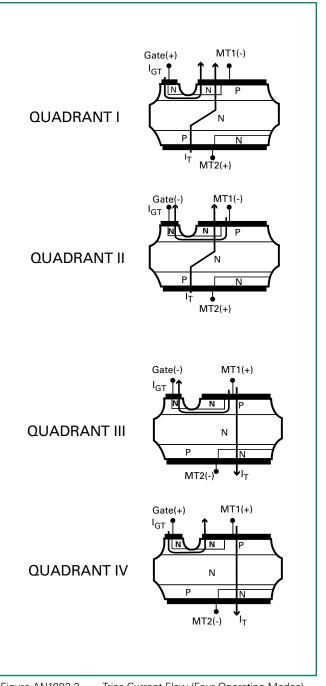

Figure AN1001.6 show simplified cross-sectional views of a Triac chip in various gating quadrants and blocking modes.

Figure AN1001.6 Simplified Cross-sectional of Triac Chip

#### SIDAC

#### **Basic Operation**

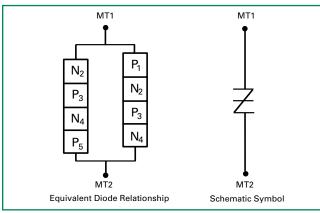

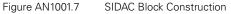

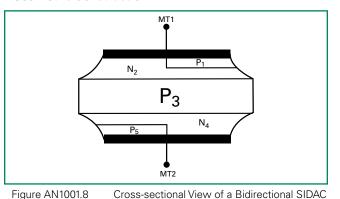

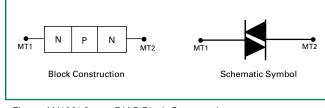

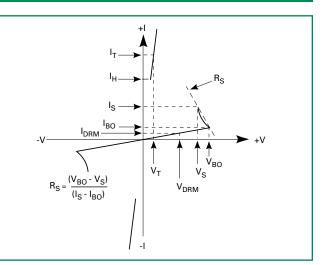

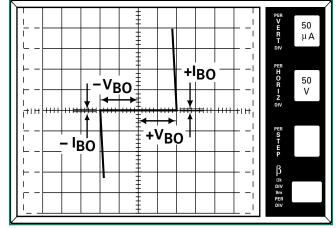

The SIDAC is a multi-layer silicon semiconductor switch. Figure AN1001.7 illustrates its equivalent block construction using two Shockley diodes connected inverse parallel. Figure AN1001.7 also shows the schematic symbol for the SIDAC.

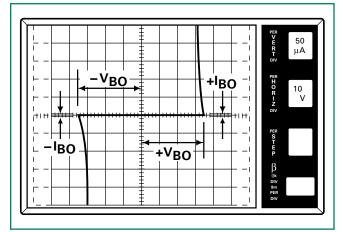

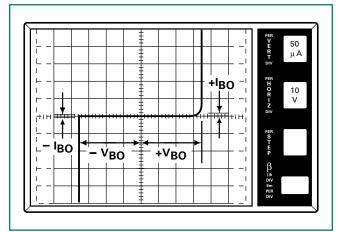

The SIDAC operates as a bidirectional switch activated by voltage. In the off state, the SIDAC exhibits leakage currents (I\_{\_{DBM}}) less than 5  $\mu A.$  As applied voltage exceeds the SIDAC  $V_{\rm BO}$ , the device begins to enter a negative resistance switching mode with characteristics similar to an avalanche diode. When supplied with enough current (I<sub>a</sub>), the SIDAC switches to an on state, allowing high current to flow. When it switches to on state, the voltage across the device drops to less than 5 V, depending on magnitude of the current flow. When the SIDAC switches on and drops into regeneration, it remains on as long as holding current is less than maximum value (150 mA, typical value of 30 mA to 65 mA). The switching current (I<sub>c</sub>) is very near the holding current (I<sub>1</sub>) value. When the SIDAC switches, currents of 10 A to 100 A are easily developed by discharging small capacitor into primary or small, very highvoltage transformers for 10 µs to 20 µs.

The main application for SIDACs is ignition circuits or inexpensive high voltage power supplies.

#### **Geometric Construction**

Figure AN1001.8

Chip with Multi-layer Construction

#### DIAC

#### **Basic Operation**

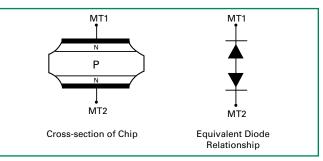

The construction of a DIAC is similar to an open base NPN transistor. Figure AN1001.9 shows a simple block construction of a DIAC and its schematic symbol.

Figure AN1001.9 **DIAC Block Construction**

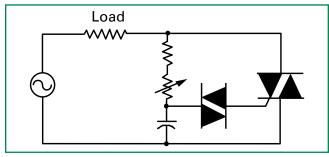

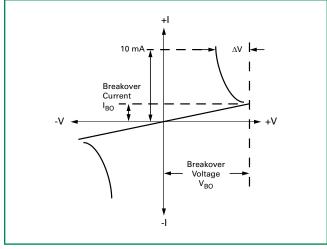

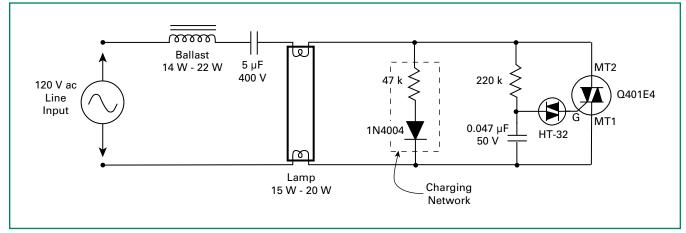

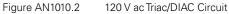

The bidirectional transistor-like structure exhibits a highimpedance blocking state up to a voltage breakover point  $(V_{_{\rm RO}})$  above which the device enters a negative-resistance region. These basic DIAC characteristics produce a bidirectional pulsing oscillator in a resistor-capacitor AC circuit. Since the DIAC is a bidirectional device, it makes a good economical trigger for firing Triacs in phase control circuits such as light dimmers and motor speed controls. Figure AN1001.10 shows a simplified AC circuit using a DIAC and a Triac in a phase control application.

Figure AN1001.10 AC Phase Control Circuit

#### **Geometric Construction**

Figure AN1001.11 Cross-sectional View of DIAC Chip

Specifications are subject to change without notice Please refer to http://www.littelfuse.com for current information.

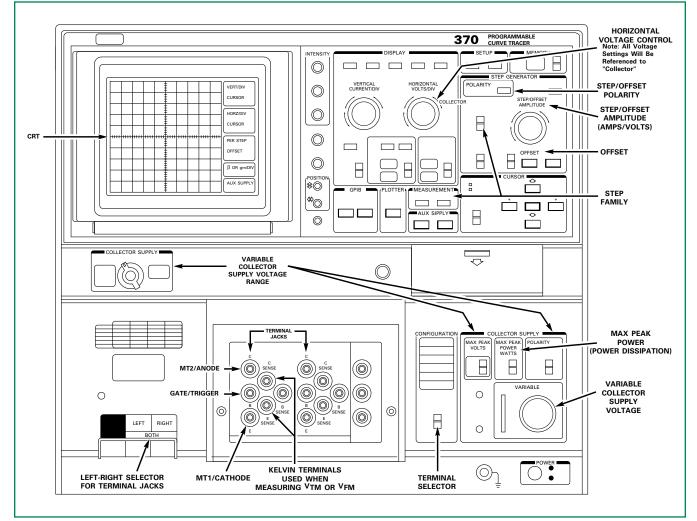

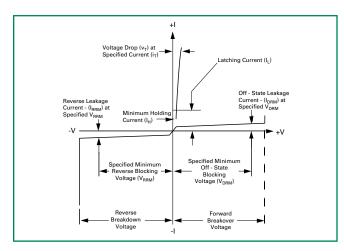

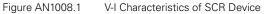

#### **Electrical Characteristic Curves of Thyristors**

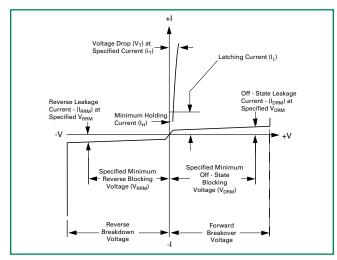

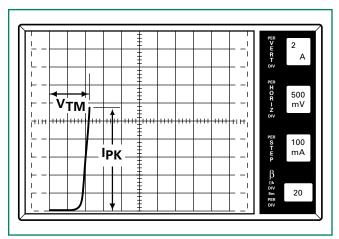

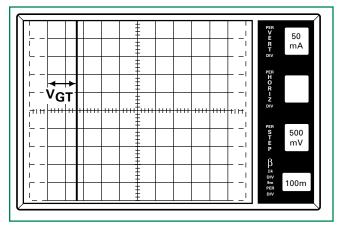

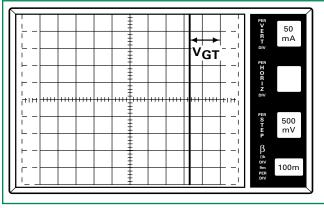

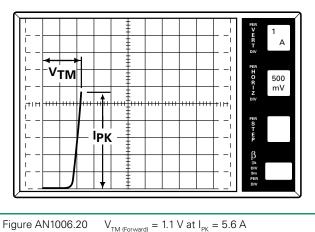

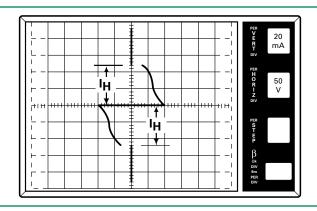

Figure AN1001.12 V-I Characteristics of SCR Device

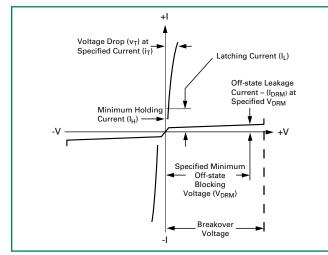

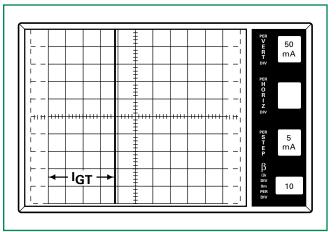

Figure AN1001.13 V-I Characteristics of Triac Device

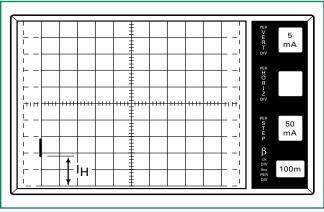

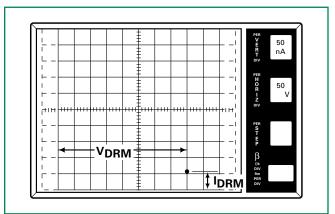

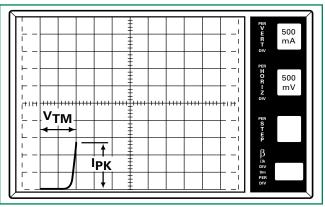

Figure AN1001.14 V-I Characteristics of Bilateral Trigger DIAC

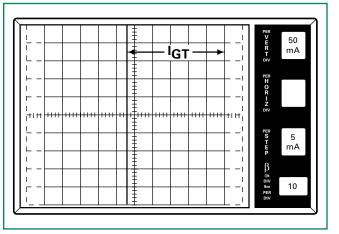

Figure AN1001.15 V-I Characteristics of a SIDAC Chip

#### Methods of Switching on Thyristors

Three general methods are available for switching Thyristors to on-state condition:

- Application of gate signal

- Static dv/dt turn-on

- Voltage breakover turn-on

#### **Application Of Gate Signal**

Gate signal must exceed I<sub>GT</sub> and V<sub>GT</sub> requirements of the Thyristor used. For an SCR (unilateral device), this signal must be positive with respect to the cathode polarity. A Triac (bilateral device) can be turned on with gate signal of either polarity; however, different polarities have different requirements of I<sub>GT</sub> and V<sub>GT</sub> which must be satisfied. Since DIACs and SIDACs do not have a gate, this method of turnon is not applicable. In fact, the single major application of DIACs is to switch on Triacs.

#### Static dv/dt Turn-on

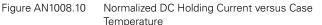

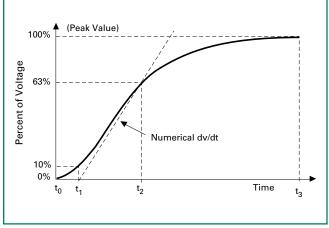

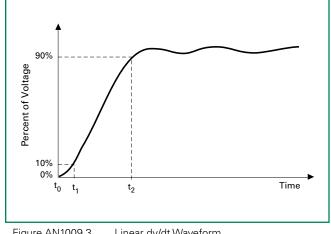

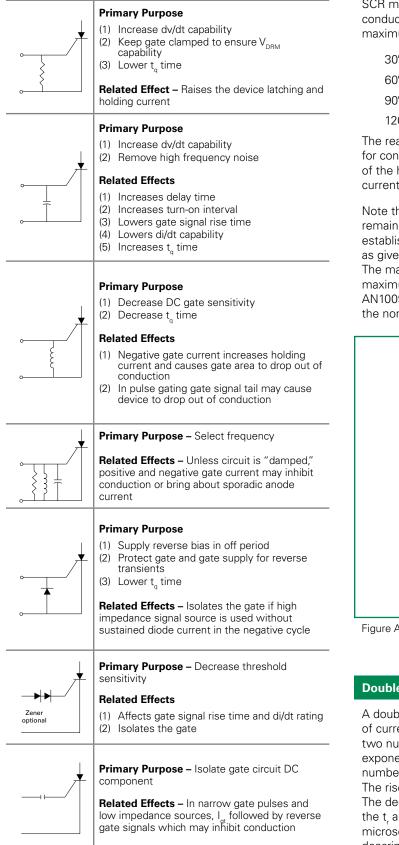

Static dv/dt turn-on comes from a fast-rising voltage applied across the anode and cathode terminals of an SCR or the main terminals of a Triac. Due to the nature of Thyristor construction, a small junction capacitor is formed across each PN junction. Figure AN1001.16 shows how typical internal capacitors are linked in gated Thyristors.

Figure AN1001.16 Internal Capacitors Linked in Gated Thyristors

When voltage is impressed suddenly across a PN junction, a charging current flows, equal to:

$$i = C \left(\frac{dv}{dt}\right)$$

When C  $\left(\frac{dv}{dt}\right)$  becomes greater or equal to Thyristor I<sub>GT</sub>

the Thyristor switches on. Normally, this type of turn-on does not damage the device, providing the surge current is limited.

Generally, Thyristor application circuits are designed with static dv/dt snubber networks if fast-rising voltages are anticipated.

#### Voltage Breakover Turn-on

tise Applied | Answers Delivered

This method is used to switch on SIDACs and DIACs. However, exceeding voltage breakover of SCRs and Triacs is definitely not recommended as a turn-on method.

In the case of SCRs and Triacs, leakage current increases until it exceeds the gate current required to turn on these gated Thyristors in a small localized point. When turn-on occurs by this method, localized heating in a small area may melt the silicon or damage the device if di/dt of the increasing current is not sufficiently limited.

DIACs used in typical phase control circuits are basically protected against excessive current at breakover as long as the firing capacitor is not excessively large. When DIACs are used in a zener function, current limiting is necessary.

SIDACs are typically pulse-firing, high-voltage transformers and are current limited by the transformer primary. The SIDAC should be operated so peak current amplitude, current duration, and di/dt limits are not exceeded.

#### Triac Gating Modes Of Operation

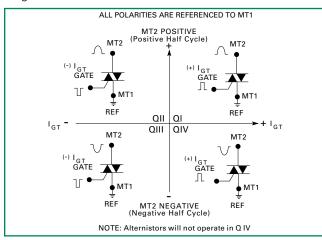

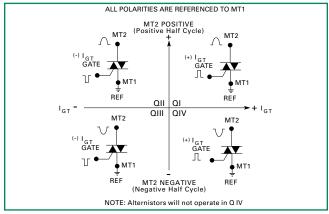

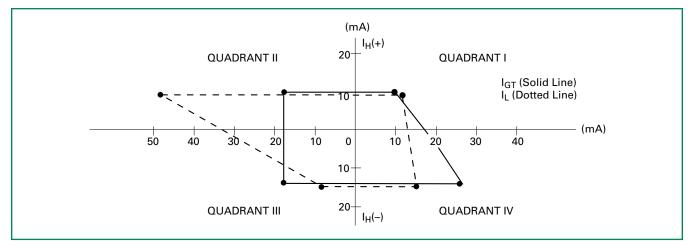

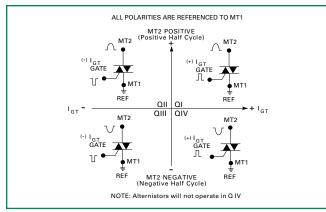

Triacs can be gated in four basic gating modes as shown in Figure AN1001.17.

Figure AN1001.17 Gating Modes

The most common quadrants for Triac gating-on are Quadrants I and III, where the gate supply is synchronized with the main terminal supply (gate positive – MT2 positive, gate negative – MT2 negative). Gate sensitivity of Triacs is most optimum in Quadrants I and III due to the inherent Thyristor chip construction. If Quadrants I and III cannot be used, the next best operating modes are Quadrants II and III where the gate has a negative polarity supply with an AC main terminal supply. Typically, Quadrant II is approximately equal in gate sensitivity to Quadrant I; however, latching current sensitivity in Quadrant II is lowest. Therefore, it is difficult for Triacs to latch on in Quadrant II when the main terminal current supply is very low in value.

Special consideration should be given to gating circuit design when Quadrants I and IV are used in actual application, because Quadrant IV has the lowest gate sensitivity of all four operating quadrants.

#### **General Terminology**

The following definitions of the most widely-used Thyristor terms, symbols, and definitions conform to existing EIA-JEDEC standards:

**Breakover Point** – Any point on the principal voltage-current characteristic for which the differential resistance is zero and where the principal voltage reaches a maximum value

**Principal Current** – Generic term for the current through the collector junction (the current through main terminal 1 and main terminal 2 of a Triac or anode and cathode of an SCR)

Principal Voltage – Voltage between the main terminals:

- (1) In the case of reverse blocking Thyristors, the principal voltage is called positive when the anode potential is higher than the cathode potential and negative when the anode potential is lower than the cathode potential.

- (2) For bidirectional Thyristors, the principal voltage is called positive when the potential of main terminal 2 is higher than the potential of main terminal 1.

**Off State** – Condition of the Thyristor corresponding to the high-resistance, low-current portion of the principal voltagecurrent characteristic between the origin and the breakover point(s) in the switching quadrant(s)

**On State** – Condition of the Thyristor corresponding to the low-resistance, low-voltage portion of the principal voltage-current characteristic in the switching quadrant(s).

#### Specific Terminology

**Average Gate Power Dissipation** [P<sub>G(AV)</sub>] – Value of gate power which may be dissipated between the gate and main terminal 1 (or cathode) averaged over a full cycle

**Breakover Current (I** $_{\rm BO}$ ) – Principal current at the breakover point

**Breakover Voltage (V** $_{\rm BO}$ ) – Principal voltage at the breakover point

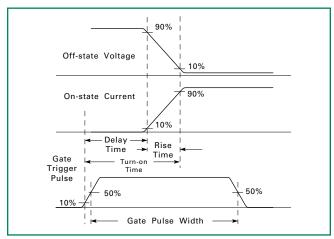

**Circuit-commutated Turn-off Time**  $(t_a)$  – Time interval between the instant when the principal current has decreased to zero after external switching of the principal voltage circuit and the instant when the Thyristor is capable of supporting a specified principal voltage without turning on

**Critical Rate-of-rise of Commutation Voltage of a Triac** (**Commutating dv/dt**) – Minimum value of the rate-of-rise of principal voltage which will cause switching from the off state to the on state immediately following on-state current conduction in the opposite quadrant

#### Critical Rate-of-rise of Off-state Voltage or Static dv/

**dt (dv/dt)** – Minimum value of the rate-of-rise of principal voltage which will cause switching from the off state to the on state

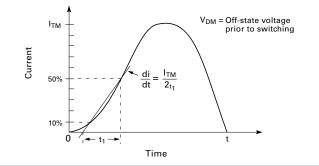

#### Critical Rate-of-rise of On-state Current (di/dt) -

Maximum value of the rate-of-rise of on-state current that a Thyristor can withstand without harmful effect

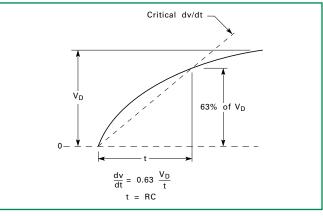

**Gate-controlled Turn-on Time (t**<sub>gt</sub>) – Time interval between a specified point at the beginning of the gate pulse and the instant when the principal voltage (current) has dropped to a specified low value (or risen to a specified high value) during switching of a Thyristor from off state to the on state by a gate pulse.

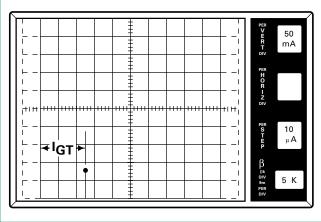

**Gate Trigger Current (I** $_{\rm GT}$ ) – Minimum gate current required to maintain the Thyristor in the on state

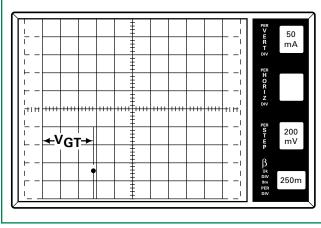

**Gate Trigger Voltage (V**<sub>GT</sub>) – Gate voltage required to produce the gate trigger current

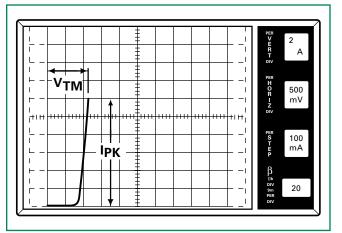

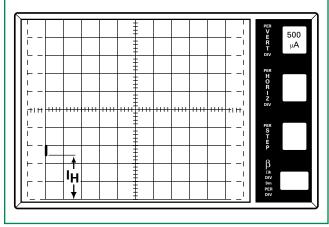

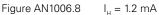

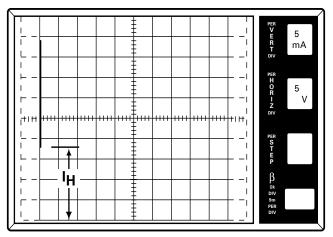

**Holding Current (I**<sub> $\mu$ </sub>) – Minimum principal current required to maintain the Thyristor in the on state

**Latching Current (I**<sub>L</sub>) – Minimum principal current required to maintain the Thyristor in the on state immediately after the switching from off state to on state has occurred and the triggering signal has been removed

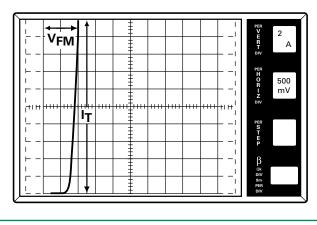

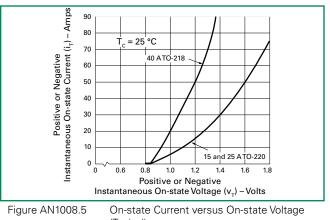

$\textbf{On-state Current} (\textbf{I}_{\scriptscriptstyle T})$  – Principal current when the Thyristor is in the on state

**Peak Gate Power Dissipation (P**<sub>GM</sub>) – Maximum power which may be dissipated between the gate and main terminal 1 (or cathode) for a specified time duration

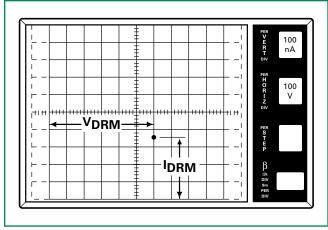

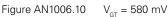

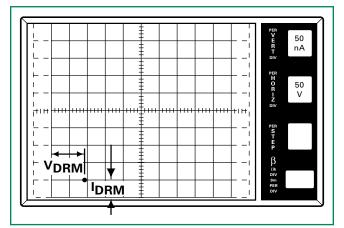

**Repetitive Peak Off-state Current (I**<sub>DRM</sub>) – Maximum instantaneous value of the off-state current that results from the application of repetitive peak off-state voltage

**Repetitive Peak Off-state Voltage (V**<sub>DRM</sub>) – Maximum instantaneous value of the off-state voltage which occurs across a Thyristor, including all repetitive transient voltages and excluding all non-repetitive transient voltages

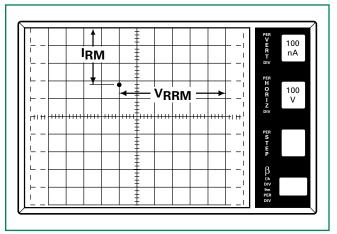

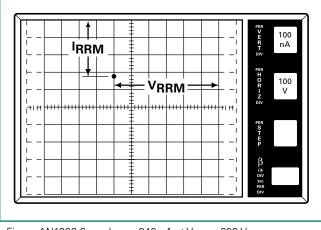

#### Repetitive Peak Reverse Current of an SCR (I<sub>RBM</sub>)

Maximum instantaneous value of the reverse current resulting from the application of repetitive peak reverse voltage

#### Repetitive Peak Reverse Voltage of an SCR (V<sub>RRM</sub>)-

Maximum instantaneous value of the reverse voltage which occurs across the Thyristor, including all repetitive transient voltages and excluding all non-repetitive transient voltages

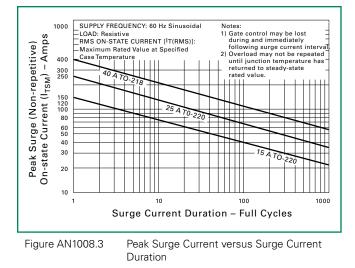

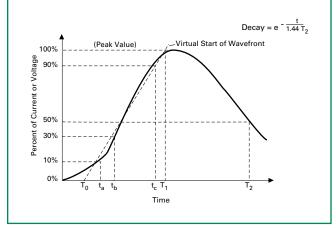

Surge (Non-repetitive) On-state Current ( $I_{\text{TSM}}$ ) – On-state

current of short-time duration and specified waveshape

#### Thermal Resistance, Junction to Ambient ( $R_{_{\Theta,IA}}$ )–

Temperature difference between the Thyristor junction and ambient divided by the power dissipation causing the temperature difference under conditions of thermal equilibrium

Note: Ambient is the point at which temperature does not change as the result of dissipation.

#### Thermal Resistance, Junction to Case $(R_{_{\Theta JC}})$ –

Temperature difference between the Thyristor junction and the Thyristor case divided by the power dissipation causing the temperature difference under conditions of thermal equilibrium

## Gating, Latching, and Holding of SCRs and Triacs

#### Introduction

Gating, latching, and holding currents of Thyristors are some of the most important parameters. These parameters and their interrelationship determine whether the SCRs and Triacs will function properly in various circuit applications.

This application note describes how the SCR and Triac parameters are related. This knowledge helps users select best operating modes for various circuit applications.

#### Gating of SCRs and Triacs

Three general methods are available to switch Thyristors to on-state condition:

- Applying proper gate signal

- Exceeding Thyristor static dv/dt characteristics

- Exceeding voltage breakover point

ittelfuse

Expertise Applied | Answers Delivered

This application note examines only the application of proper gate signal. Gate signal must exceed the  $I_{\rm GT}$  and  $V_{\rm GT}$  requirements of the Thyristor being used.  $I_{\rm GT}$  (gate trigger current) is the minimum gate current required to switch a Thyristor from the off state to the on state.  $V_{\rm GT}$  (gate trigger voltage) is the voltage required to produce the gate trigger current.

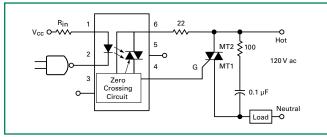

SCRs (unilateral devices) require a positive gate signal with respect to the cathode polarity. Figure AN1002.1 shows the current flow in a cross-sectional view of the SCR chip.

Figure AN1002.1 SCR Current Flow

In order for the SCR to latch on, the anode-to-cathode current (I<sub>T</sub>) must exceed the latching current (I<sub>L</sub>) requirement. Once latched on, the SCR remains on until it is turned off when anode-to-cathode current drops below holding current (I<sub>H</sub>) requirement.

Triacs (bilateral devices) can be gated on with a gate signal of either polarity with respect to the MT1 terminal; however, different polarities have different requirements of  $I_{\rm GT}$  and  $V_{\rm GT}$  Figure AN1002.2 illustrates current flow through the Triac chip in various gating modes.

Figure AN1002.2 Triac Current Flow (Four Operating Modes)

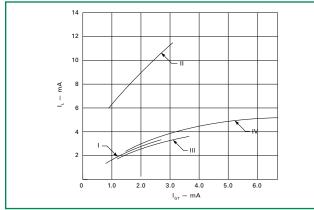

Triacs can be gated on in one of four basic gating modes as shown in Figure AN1002.3. The most common quadrants for gating on Triacs are Quadrants I and III, where the gate supply is synchronized with the main terminal supply (gate positive – MT2 positive, gate negative – MT2 negative). Optimum Triac gate sensitivity is achieved when operating in Quadrants I and III due to the inherent Thyristor chip construction. If Quadrants I and III cannot be used, the next best operating modes are Quadrants II and III where the gate supply has a negative polarity with an AC main terminal supply. Typically, Quadrant II is approximately equal in gate sensitivity to Quadrant I; however, latching current sensitivity in Quadrant II is lowest. Therefore, it is difficult for Triacs to latch on in Quadrant II when the main terminal current supply is very low in value.

Special consideration should be given to gating circuit design when Quadrants I and IV are used in actual application, because Quadrant IV has the lowest gate sensitivity of all four operating quadrants.

Figure AN1002.3 Definition of Operating Quadrants in Triacs

The following table shows the relationships between different gating modes in current required to gate on Triacs.

| Typical Ratio of <mark>I<sub>c⊺</sub> (in given Quadrant)</mark> at 25ºC<br>I <sub>c⊤</sub> (Quadrant 1) |                |             |              |             |  |

|----------------------------------------------------------------------------------------------------------|----------------|-------------|--------------|-------------|--|

| Tupo                                                                                                     | Operating Mode |             |              |             |  |

| Туре                                                                                                     | Quadrant I     | Quadrant II | Quadrant III | Quadrant IV |  |

| 4 A Triac                                                                                                | 1              | 1.6         | 2.5          | 2.7         |  |

| 10 A Triac                                                                                               | 1              | 1.5         | 1.4          | 3.1         |  |

Example of 4 A Triac:

If  $I_{GT}(I) = 10 \text{ mA}$ , then

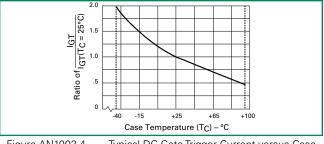

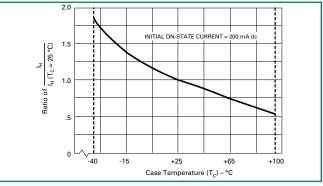

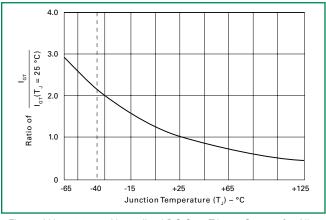

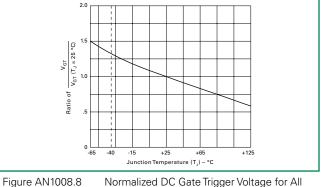

Gate trigger current is temperature-dependent as shown in Figure AN1002.4. Thyristors become less sensitive with decreasing temperature and more sensitive with increasing temperature.

For applications where low temperatures are expected, gate current supply should be increased to at least two to eight times the gate trigger current requirements at 25 °C. The actual factor varies by Thyristor type and the environmental temperature.

Example of a 10 A Triac:

If  $I_{GT}(I) = 10 \text{ mA at } 25 \text{ °C}$ , then

$$I_{GT}(I) = 20 \text{ mA at } -40 \text{ °C}$$

In applications where high di/dt, high surge, and fast turn-on are expected, gate drive current should be steep rising (1  $\mu$ s rise time) and at least twice rated I<sub>GT</sub> or higher with minimum 3  $\mu$ s pulse duration. However, if gate drive current magnitude is very high, then duration may have to be limited to keep from overstressing (exceeding the power dissipation limit of) gate junction.

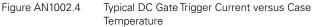

#### Latching Current of SCRs and Triacs

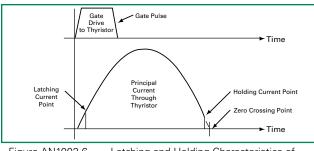

Latching current ( $I_L$ ) is the minimum principal current required to maintain the Thyristor in the on state immediately after the switching from off state to on state has occurred and the triggering signal has been removed. Latching current can best be understood by relating to the "pick-up" or "pull-in" level of a mechanical relay. Figure AN1002.5 and Figure AN1002.6 illustrate typical Thyristor latching phenomenon.

In the illustrations in Figure AN1002.5, the Thyristor does not stay on after gate drive is removed due to insufficient available principal current (which is lower than the latching current requirement).

Not Latched) In the illustration in Figure AN1002.6 the device stays on for the remainder of the half cycle until the principal current falls below the holding current level. Figure AN1002.5 shows the characteristics of the same device if gate drive is removed or shortened before latching current requirement has been met.

Figure AN1002.6 Latching and Holding Characteristics of Thyristor

Similar to gating, latching current requirements for Triacs are different for each operating mode (quadrant). Definitions of latching modes (quadrants) are the same as gating modes. Therefore, definitions shown in Figure AN1002.2 and Figure AN1002.3 can be used to describe latching modes (quadrants) as well. The following table shows how different latching modes (quadrants) relate to each other. As previously stated, Quadrant II has the lowest latching current sensitivity of all four operating quadrants.

| Typical Ratio of |                |             |              |             |  |

|------------------|----------------|-------------|--------------|-------------|--|

| Turne            | Operating Mode |             |              |             |  |

| Туре             | Quadrant I     | Quadrant II | Quadrant III | Quadrant IV |  |

| 4 A Triac        | 1              | 4           | 1.2          | 1.1         |  |

| 10 A Triac       | 1              | 4           | 1.1          | 1           |  |

Example of a 4 Amp Triac:

If

$$I_{L}(I) = 10 \text{ mA}$$

, then

$$I_{L}(II) = 40 \text{ mA}$$

$$I_{L}(III) = 12 \text{ mA}$$

$$I_{1}(IV) = 11 \text{ mA}$$

Latching current has even somewhat greater temperature dependence compared to the DC gate trigger current. Applications with low temperature requirements should have sufficient principal current (anode current) available to ensure Thyristor latch-on.

Two key test conditions on latching current specifications are gate drive and available principal (anode) current durations. Shortening the gate drive duration can result in higher latching current values.

#### Holding Current of SCRs and Triacs

Holding current  $(I_{\mu})$  is the minimum principal current required to maintain the Thyristor in the on state. Holding current can best be understood by relating it to the "dropout" or "must release" level of a mechanical relay. Figure AN1002.6 shows the sequences of gate, latching, and holding currents. Holding current will always be less than latching. However, the more sensitive the device, the closer the holding current value approaches its latching current value.

Holding current is independent of gating and latching, but the device must be fully latched on before a holding current limit can be determined. Holding current modes of the Thyristor are strictly related to the voltage polarity across the main terminals. The following table illustrates how the positive and negative holding current modes of Triacs relate to each other.

| Typical Triac Holding Current Ratio |                    |                    |  |  |

|-------------------------------------|--------------------|--------------------|--|--|

| Turce                               | Operating Mode     |                    |  |  |

| Туре                                | ا <sub>н</sub> (+) | I <sub>н</sub> (—) |  |  |

| 4 A Triac                           | 1                  | 1.1                |  |  |

| 10 A Triac                          | 1                  | 1.3                |  |  |

Example of a 10 A Triac:

If

$$I_{H}(+) = 10 \text{ mA}$$

, then

$I_{H}(-) = 13 \text{ mA}$

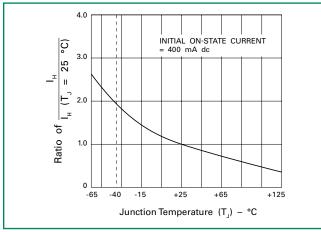

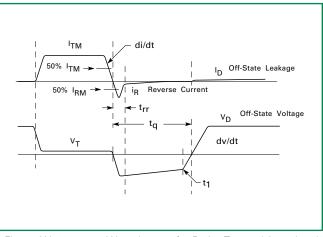

Holding current is also temperature-dependent like gating and latching shown in Figure AN1002.7. The initial onstate current is 200 mA to ensure that the Thyristor is fully latched on prior to holding current measurement. Again, applications with low temperature requirements should have sufficient principal (anode) current available to maintain the Thyristor in the on-state condition.

Both minimum and maximum holding current specifications may be important, depending on application. Maximum holding current must be considered if the Thyristor is to stay in conduction at low principal (anode) current; the minimum holding current must be considered if the device is expected to turn off at a low principal (anode) current.

Figure AN1002.7 Typical DC Holding Current vs Case Temperatures

Example of a 10 A Triac:

lf

I<sub>H</sub>(+) = 10 mA at 25 °C, then

$I_{H}(+) \approx 7.5 \text{ mA at } 65 \text{ }^{\circ}\text{C}$

#### Relationship of Gating, Latching, and Holding Currents

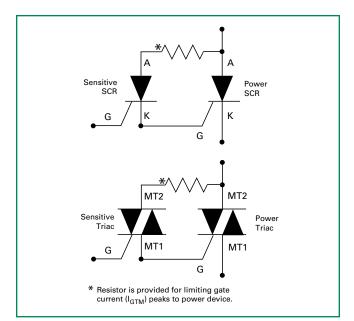

Although gating, latching, and holding currents are independent of each other in some ways, the parameter values are related. If gating is very sensitive, latching and holding will also be very sensitive and vice versa. One way to obtain a sensitive gate and not-so-sensitive latchingholding characteristic is to have an "amplified gate" as shown in Figure AN1002.8.

The following table and Figure AN1002.9 show the relationship of gating, latching, and holding of a 4 A device.

| Typical 4 A Triac Gating, Latching,<br>and Holding Relationship |                             |             |              |             |

|-----------------------------------------------------------------|-----------------------------|-------------|--------------|-------------|

| Parameter                                                       | Quadrants or Operating Mode |             |              |             |

| Falameter                                                       | Quadrant I                  | Quadrant II | Quadrant III | Quadrant IV |

| I <sub>gt</sub> (mA)                                            | 10 17                       |             | 18           | 27          |

| I <sub>L</sub> (mA)                                             | 12                          | 48          | 12           | 13          |

| I <sub>H</sub> (mA)                                             | 10                          | 10          | 12           | 12          |

Figure AN1002.8 "Amplified Gate" Thyristor Circuit

Figure AN1002.9 Typical Gating, Latching, and Holding Relationships of 4 A Triac at 25 °C

The relationships of gating, latching, and holding for several device types are shown in the following table. For convenience all ratios are referenced to Quadrant I gating.

| Typical Ratio of Gating, Latching, and Holding Current at 25 °C |             |                                                    |                                                   |         |          |           |                               |     |      |

|-----------------------------------------------------------------|-------------|----------------------------------------------------|---------------------------------------------------|---------|----------|-----------|-------------------------------|-----|------|

|                                                                 |             | Ratio                                              |                                                   |         |          |           |                               |     |      |

| Devices                                                         | (II)<br>(I) | <u>I<sub>GT</sub> (III)</u><br>I <sub>GT</sub> (I) | <u>Ι<sub>GT</sub> (IV)</u><br>Ι <sub>GT</sub> (I) | (I)<br> | (II)<br> | (III)<br> | L (IV)<br>I <sub>GT</sub> (I) |     | <br> |

| 4A Triac                                                        | 1.6         | 2.5                                                | 2.7                                               | 1.2     | 4.8      | 1.2       | 1.3                           | 1.0 | 1.2  |

| 10A Triac                                                       | 1.5         | 1.4                                                | 3.1                                               | 1.6     | 4.0      | 1.8       | 2.0                           | 1.1 | 1.6  |

| 15A Alternistor                                                 | 1.5         | 1.8                                                | -                                                 | 2.4     | 7.0      | 2.1       | _                             | 2.2 | 1.9  |

| 1A Sensitive SCR                                                | -           | -                                                  | -                                                 | 25      | _        | -         | -                             | 25  | _    |

| 6A SCR                                                          | _           | _                                                  | _                                                 | 3.2     | _        | _         | _                             | 2.6 | _    |

Examples of a 10 A Triac:

| lf | $I_{gT}(I) = 10 \text{ mA, then}$        |

|----|------------------------------------------|

|    | $I_{gT}(II) = 15 \text{ mA}$             |

|    | $I_{gT}(III) = 14 \text{ mA}$            |

|    | $I_{GT}(IV) = 31 \text{ mA}$             |

| lf | $I_{L}(I) = 16 \text{ mA}, \text{ then}$ |

|    | $I_{L}(II) = 40 \text{ mA}$              |

|    | $I_{L}(III) = 18 \text{ mA}$             |

|    | $I_{L}(IV) = 20 \text{ mA}$              |

If  $I_{H}(+) = 11 \text{ mA at } 25 \text{ °C}$ , then  $I_{H}(+) = 16 \text{ mA}$

#### Summary

Gating, latching, and holding current characteristics of Thyristors are quite important yet predictable (once a single parameter value is known). Their interrelationships (ratios) can also be used to help designers in both initial circuit application design as well as device selection.

## **Phase Control Using Thyristors**

#### Introduction

Due to high-volume production techniques, Thyristors are now priced so that almost any electrical product can benefit from electronic control. A look at the fundamentals of SCR and Triac phase controls shows how this is possible.

#### **Output Power Characteristics**

Phase control is the most common form of Thyristor power control. The Thyristor is held in the off condition – that is, all current flow in the circuit is blocked by the Thyristor except a minute leakage current. Then the Thyristor is triggered into an "on" condition by the control circuitry.

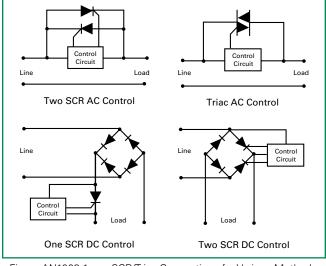

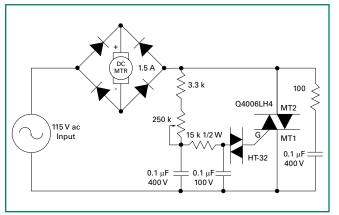

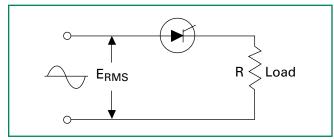

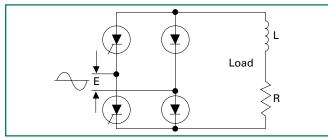

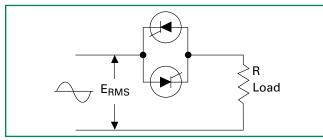

For full-wave AC control, a single Triac or two SCRs connected in inverse parallel may be used. One of two methods may be used for full-wave DC control -- a bridge rectifier formed by two SCRs or an SCR placed in series with a diode bridge as shown in Figure AN1003.1.

Figure AN1003.1 SCR/Triac Connections for Various Methods of Phase Control

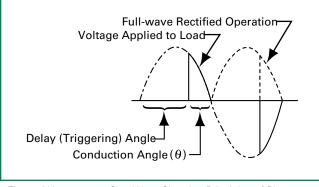

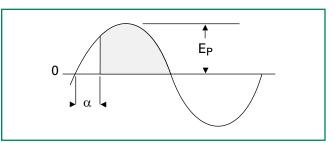

Figure AN1003.2 illustrates voltage waveform and shows common terms used to describe Thyristor operation. Delay angle is the time during which the Thyristor blocks the line voltage. The conduction angle is the time during which the Thyristor is on. It is important to note that the circuit current is determined by the load and power source. For simplification, assume the load is resistive; that is, both the voltage and current waveforms are identical.

Figure AN1003.2 Sine Wave Showing Principles of Phase Control

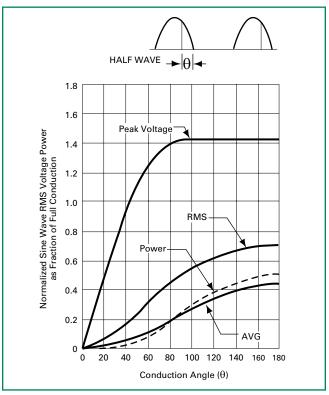

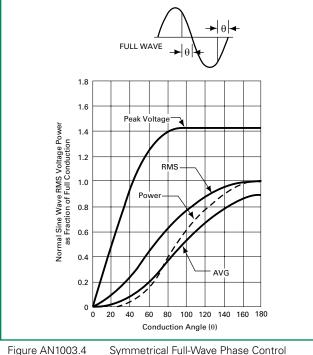

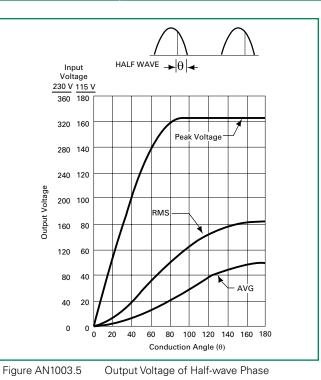

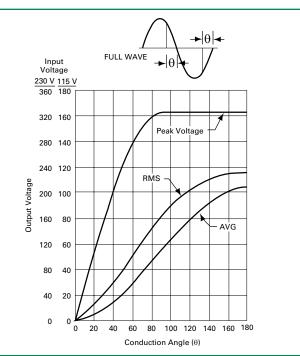

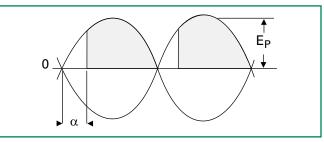

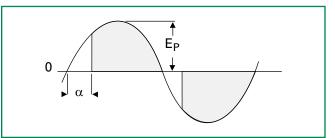

Different loads respond to different characteristics of the AC waveform. For example, some are sensitive to average voltage, some to RMS voltage, and others to peak voltage. Various voltage characteristics are plotted against conduction angle for half- and full-wave phase control circuits in Figure AN1003.3 and Figure AN1003.4.

Figure AN1003.3 Half-Wave Phase Control (Sinusoidal)

Figure AN1003.4 Symmetrical Full-Wave Phase Contro (Sinusoidal)

Figure AN1003.3 and Figure AN1003.4 also show the relative power curve for constant impedance loads such as heaters. Because the relative impedance of incandescent lamps and motors change with applied voltage, they do not follow this curve precisely. To use the curves, find the full-wave rated power of the load, and then multiply by the ratio associated with the specific phase angle. Thus, a 180° conduction angle in a half-wave circuit provides 0.5 x full-wave conduction power.

In a full-wave circuit, a conduction angle of  $150^{\circ}$  provides 97% full power while a conduction angle of  $30^{\circ}$  provides only 3% of full power control. Therefore, it is usually pointless to obtain conduction angles less than  $30^{\circ}$  or greater than  $150^{\circ}$ .

Figure AN1003.5 and Figure AN1003.6 give convenient direct output voltage readings for 115 V/230 V input voltage. These curves also apply to current in a resistive circuit.

ttelfuse

Expertise Applied | Answers Delivered

Output Voltage of Full-wave Phase Control

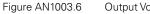

#### **Control Characteristics**

A relaxation oscillator is the simplest and most common control circuit for phase control. Figure AN1003.7 illustrates this circuit as it would be used with a Thyristor. Turn-on of the Thyristor occurs when the capacitor is charged through the resistor from a voltage or current source until the breakover voltage of the switching device is reached. Then, the switching device changes to its on state, and the capacitor is discharged through the Thyristor gate. Trigger devices used are neon bulbs, unijunction transistors, and three-, four-, or five-layer semiconductor trigger devices. Phase control of the output waveform is obtained by varying the RC time constant of the charging circuit so the trigger device breakdown occurs at different phase angles within the controlled half or full cycle.

Figure AN1003.7 Relaxation Oscillator Thyristor Trigger Circuit

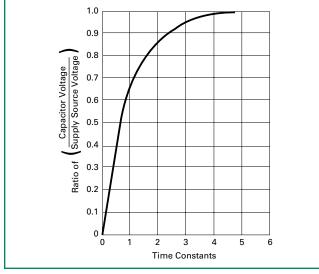

Figure AN1003.8 shows the capacitor voltage-time characteristic if the relaxation oscillator is to be operated from a pure DC source.

Figure AN1003.8 C

Capacitor Charging from DC Source

Usually, the design starting point is the selection of a capacitance value which will reliably trigger the Thyristor when the capacitance is discharged. Trigger devices and Thyristor gate triggering characteristics play a part in the selection. All the device characteristics are not always completely specified in applications, so experimental determination is sometimes needed.

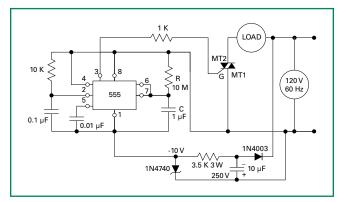

Upon final selection of the capacitor, the curve shown in Figure AN1003.8 can be used in determining the

charging resistance needed to obtain the desired control characteristics.

Many circuits begin each half-cycle with the capacitor voltage at or near zero. However, most circuits leave a relatively large residual voltage on the capacitor after discharge. Therefore, the charging resistor must be determined on the basis of additional charge necessary to raise the capacitor to trigger potential.

For example, assume that we want to trigger an S2010L SCR with a 32 V trigger DIAC. A 0.1  $\mu$ F capacitor will supply the necessary SCR gate current with the trigger DIAC. Assume a 50 V dc power supply, 30° minimum conduction angle, and 150° maximum conduction angle with a 60 Hz input power source. At approximately 32 V, the DIAC triggers leaving 0.66 V<sub>BO</sub> of DIAC voltage on the capacitor. In order for DIAC to trigger, 22 V must be added to the capacitor potential, and 40 V additional (50-10) are available. The capacitor must be charged to 22/40 or 0.55 of the available charging voltage in the desired time. Looking at Figure AN1003.8, 0.55 of charging voltage represents 0.8 time constant. The 30° conduction angle required that the firing pulse be delayed 150° or 6.92 ms. (The period of 1/2 cycle at 60 Hz is 8.33 ms.) To obtain this time delay:

6.92 ms = 0.8 RC

RC = 8.68 ms

if C = 0.10 μF

then, R =

$$\frac{8.68 \times 10^{-3}}{0.1 \times 10^{-6}}$$

= 86,000 Ω

To obtain the minimum R (150° conduction angle), the delay is 30° or

$$(30/180) \times 8.33 = 1.39 \text{ ms}$$

$$1.39 \text{ ms} = 0.8 \text{ RC}$$

$$\text{RC} = 1.74 \text{ ms}$$

$$\text{R} = \frac{1.74 \times 10^{-3}}{0.1 \times 10^{-6}} = 17,400 \text{ G}$$

Using practical values, a 100 k potentiometer with up to 17 k minimum (residual) resistance should be used. Similar calculations using conduction angles between the maximum and minimum values will give control resistance versus power characteristic of this circuit.

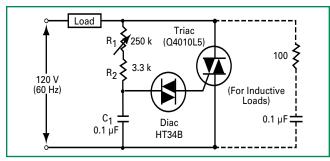

#### Triac Phase Control

The basic full-wave Triac phase control circuit shown in Figure AN1003.9 requires only four components. Adjustable resistor R<sub>1</sub> and C<sub>1</sub> are a single-element phase-shift network. When the voltage across C<sub>1</sub> reaches breakover voltage (V<sub>80</sub>) of the DIAC, C<sub>1</sub> is partially discharged by the DIAC into the Triac gate. The Triac is then triggered into the conduction mode for the remainder of that half-cycle. In this circuit, triggering is in Quadrants I and III. The unique simplicity of this circuit makes it suitable for applications with small control range.

Figure AN1003.9 Basic DIAC-Triac Phase Control

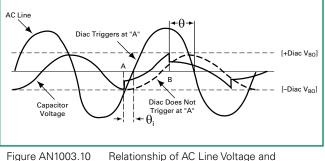

The hysteresis (snap back) effect is somewhat similar to the action of a kerosene lantern. That is, when the control knob is first rotated from the off condition, the lamp can be lit only at some intermediate level of brightness, similar to turning up the wick to light the lantern. Brightness can then be turned down until it finally reaches the extinguishing point. If this occurs, the lamp can only be relit by turning up the control knob again to the intermediate level. Figure AN1003.10 illustrates the hysteresis effect in capacitor-DIAC triggering. As R<sub>1</sub> is brought down from its maximum resistance, the voltage across the capacitor increases until the DIAC first fires at point A, at the end of a halfcycle (conduction angle  $\theta$ i). After the gate pulse, however, the capacitor voltage drops suddenly to about half the triggering voltage, giving the capacitor a different initial condition. The capacitor charges to the DIAC, triggering voltage at point B in the next half-cycle and giving a steadystate conduction angle shown as  $\theta$  for the Triac.

Figure AN1003.10 Relationship of AC Line Voltage and Triggering Voltage

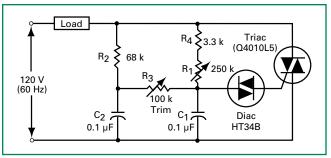

In the Figure AN1003.11 illustration, the addition of a second RC phase-shift network extends the range on control and reduces the hysteresis effect to a negligible region. This circuit will control from 5% to 95% of full load power, but is subject to supply voltage variations. When R<sub>1</sub> is large, C<sub>1</sub> is charged primarily through R<sub>3</sub> from the phase-shifted voltage appearing across C<sub>2</sub>. This action provides additional range of phase-shift across C<sub>1</sub> and enables C<sub>2</sub> to partially recharge C<sub>1</sub> after the DIAC has triggered, thus reducing hysteresis. R<sub>3</sub> should be adjusted so that the circuit just drops out of conduction when R<sub>1</sub> is brought to maximum resistance.

ttelfuse

Expertise Applied Answers Delivered

Figure AN1003.11 Extended Range Full-wave Phase Control

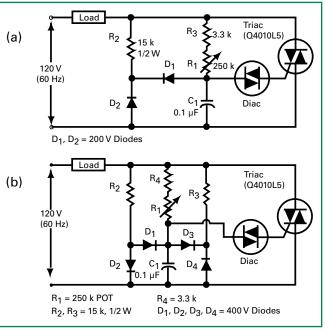

By using one of the circuits shown in Figure AN1003.12, the hysteresis effect can be eliminated entirely. The circuit (a) resets the timing capacitor to the same level after each positive half-cycle, providing a uniform initial condition for the timing capacitor. This circuit is useful only for resistive loads since the firing angle is not symmetrical throughout the range. If symmetrical firing is required, use the circuit (b) shown in Figure AN1003.12.

Figure AN1003.12 Wide-range Hysteresis Free Phase Control

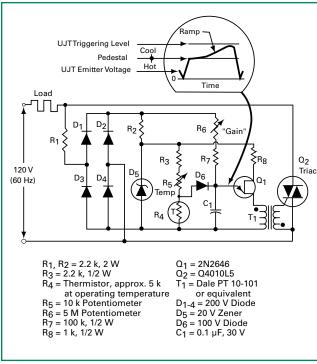

For more complex control functions, particularly closed loop controls, the unijunction transistor may be used for the triggering device in a ramp and pedestal type of firing circuit as shown in Figure AN1003.13.

Figure AN1003.13 Precision Proportional Temperature Control

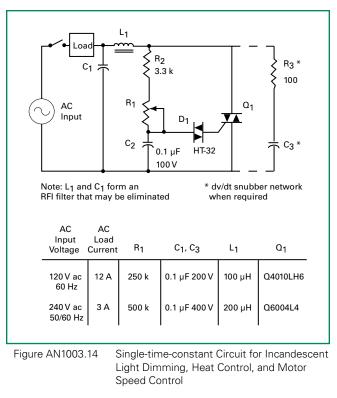

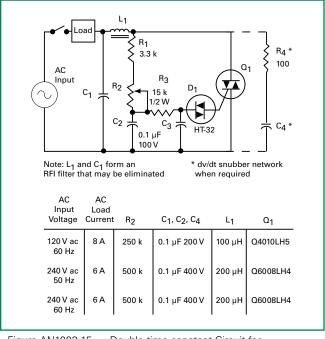

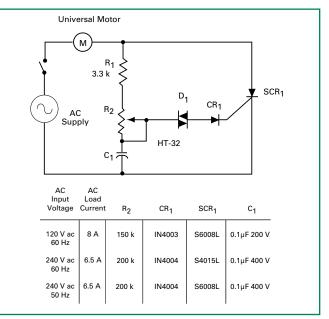

Several speed control and light dimming (phase) control circuits have been presented that give details for a complete 120 V application circuit but none for 240 V. Figure AN1003.14 and Figure AN1003.15 show some standard phase control circuits for 240 V, 60 Hz/50 Hz operation along with 120 V values for comparison. Even though there is very little difference, there are a few key things that must be remembered. First, capacitors and Triacs connected across the 240 V line must be rated at 400 V. Secondly, the potentiometer (variable resistor) value must change considerably to obtain the proper timing or triggering for 180° in each half-cycle.

Figure AN1003.14 shows a simple single-time-constant light dimmer (phase control) circuit, giving values for both 120 V and 240 V operation.

The circuit shown in Figure AN1003.15 is a doubletime-constant circuit which has improved performance compared to the circuit shown in Figure AN1003.14. This circuit uses an additional RC network to extend the phase angle so that the Triac can be triggered at small conduction angles. The additional RC network also minimizes any hysteresis effect explained and illustrated in Figure AN1003.10 and Figure AN1003.11.

Figure AN1003.15

Double-time-constant Circuit for Incandescent Light Dimming, Heat Control, and Motor Speed Control

Expertise Applied Answers Delivered

#### **Permanent Magnet Motor Control**

Figure AN1003.16 illustrates a circuit for phase controlling a permanent magnet (PM) motor. Since PM motors are also generators, they have characteristics that make them difficult for a standard Triac to commutate properly. Control of a PM motor is easily accomplished by using an alternistor Triac with enhanced commutating characteristics.

Figure AN1003.16 Circuit for Phase Controlling a Permanent Magnet Motor

PM motors normally require full-wave DC rectification. Therefore, the alternistor Triac controller should be connected in series with the AC input side of the rectifier bridge. The possible alternative of putting an SCR controller in series with the motor on the DC side of the rectifier bridge can be a challenge when it comes to timing and delayed turn-on near the end of the half cycle. The alternistor Triac controller shown in Figure AN1003.16 offers a wide range control so that the alternistror Triac can be triggered at a small conduction angle or low motor speed; the rectifiers and alternistors should have similar voltage ratings, with all based on line voltage and actual motor load requirements.

#### **SCR Phase Control**

Figure AN1003.17 shows a very simple variable resistance half-wave circuit. It provides phase retard from essentially zero (SCR full on) to 90 electrical degrees of the anode voltage wave (SCR half on). Diode CR, blocks reverse gate voltage on the negative half-cycle of anode supply voltage. This protects the reverse gate junction of sensitive SCRs and keeps power dissipation low for gate resistors on the negative half cycle. The diode is rated to block at least the peak value of the AC supply voltage. The retard angle cannot be extended beyond the 90-degree point because the trigger circuit supply voltage and the trigger voltage producing the gate current to fire are in phase. At the peak of the AC supply voltage, the SCR can still be triggered with the maximum value of resistance between anode and gate. Since the SCR will trigger and latch into conduction the first time  ${\rm I}_{\rm \scriptscriptstyle GT}$  is reached, its conduction cannot be delayed beyond 90 electrical degrees with this circuit.

Figure AN1003.17 Half-wave Control, 0° to 90° Conduction

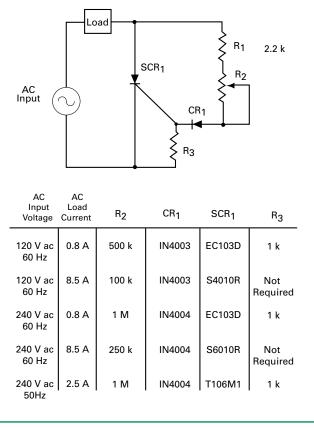

Figure AN1003.18 shows a half-wave phase control circuit using an SCR to control a universal motor. This circuit is better than simple resistance firing circuits because the phase-shifting characteristics of the RC network permit the firing of the SCR beyond the peak of the impressed voltage, resulting in small conduction angles and very slow speed.

Figure AN1003.18 Half-wave Motor Control

#### Phase Control from Logic (DC) Inputs

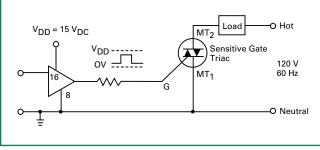

Triacs can also be phase-controlled from pulsed DC unidirectional inputs such as those produced by a digital logic control system. Therefore, a microprocessor can be interfaced to AC load by using a sensitive gate Triac to control a lamp's intensity or a motor's speed.

There are two ways to interface the unidirectional logic pulse to control a Triac. Figure AN1003.19 illustrates one easy way if load current is approximately 5 A or less. The sensitive gate Triac serves as a direct power switch controlled by HTL, TTL, CMOS, or integrated circuit operational amplifier. A timed pulse from the system's logic can activate the Triac anywhere in the AC sinewave producing a phase-controlled load.

Figure AN1003.19 Sensitive Gate Triac Operating in Quadrants I and IV

The key to DC pulse control is correct grounding for DC and AC supply. As shown in Figure AN1003.19, **DC ground and AC ground/neutral must be common plus MT1 must be connected to common ground.** MT1 of the Triac is the return for both main terminal junctions as well as the gate junction.

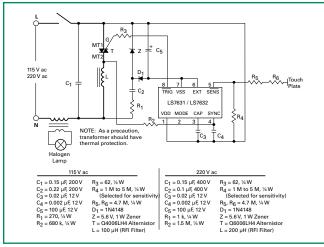

Figure AN1003.20 shows an example of a unidirectional (all negative) pulse furnished from a special I.C. that is available from LSI Computer Systems in Melville, New York. Even though the circuit and load is shown to control a Halogen lamp, it could be applied to a common incandescent lamp for touch-controlled dimming.

Figure AN1003.20 Typical Touch Plate Halogen Lamp Dimmer

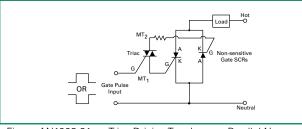

For a circuit to control a heavy-duty inductive load where an alternistor is not compatible or available, two SCRs can be driven by an inexpensive TO-92 Triac to make a very high current Triac or alternistor equivalent, as shown in Figure AN1003.21. See "Relationship of IAV, IRMS, and IPK' in AN1009 for design calculations.

Figure AN1003.21 Triac Driving Two Inverse Parallel Non-Sensitive Gate SCRs

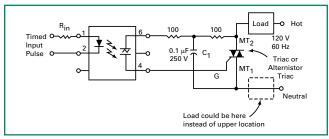

Figure AN1003.22 shows another way to interface a unidirectional pulse signal and activate AC loads at various points in the AC sine wave. This circuit has an electrically-isolated input which allows load placement to be flexible with respect to AC line. In other words, connection between DC ground and AC neutral is not required.

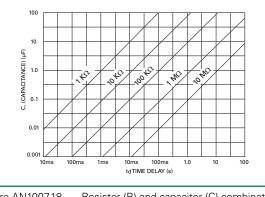

#### **Microcontroller Phase Control**

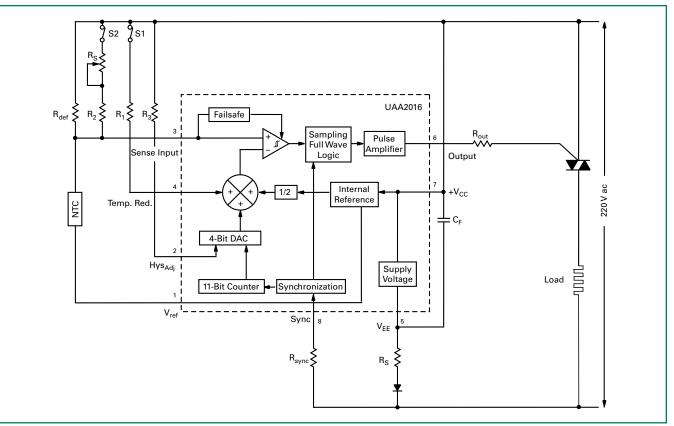

Traditionally, microcontrollers were too large and expensive to be used in small consumer applications such as a light dimmer. Microchip Technology Inc. of Chandler, Arizona has developed a line of 8-pin microcontrollers without sacrificing the functionality of their larger counterparts. These devices do not provide high drive outputs, but when combined with a sensitive Triac can be used in a costeffective light dimmer.

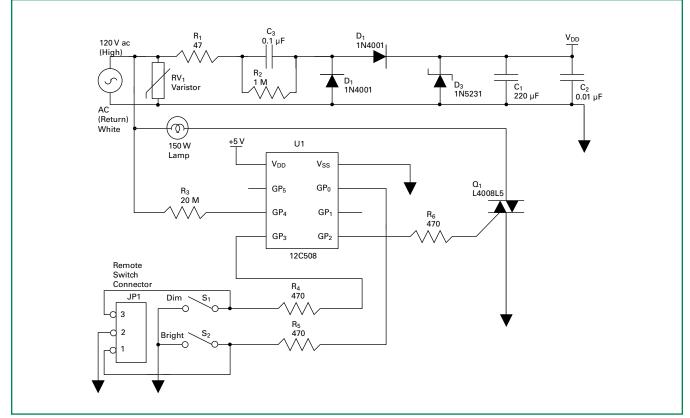

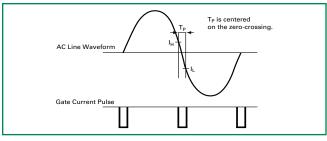

Figure AN1003.23 illustrates a simple circuit using a transformerless power supply, PIC 12C508 microcontroller, and a sensitive Triac configured to provide a light dimmer control. R<sub>3</sub> is connected to the hot lead of the AC power line and to pin GP<sub>4</sub>. The ESD protection diodes of the input structure allow this connection without damage. When the voltage on the AC power line is positive, the protection diode form the input to V<sub>DD</sub> is forward biased, and the input buffer will see approximately V<sub>DD</sub> + 0.7 V. The software will read this pin as high. When the voltage on the line is negative, the protection diode from V<sub>SS</sub> to the input pin is forward biased, and the input buffer sees approximately V<sub>SS</sub> - 0.7 V. The software will read the pin as low. By polling GP<sub>4</sub> for a change in state, the software can detect zero crossing.

Specifications are subject to change without notice. Please refer to http://www.littelfuse.com for current information

#### Figure AN1003.23 Microcontroller Light Dimmer Control

With a zero crossing state detected, software can be written to turn on the Triac by going from tri-state to a logic high on the gate and be synchronized with the AC phase cycles (Quadrants I and IV). Using pull-down switches connected to the microcontoller inputs, the user can signal the software to adjust the duty cycle of the Triac.

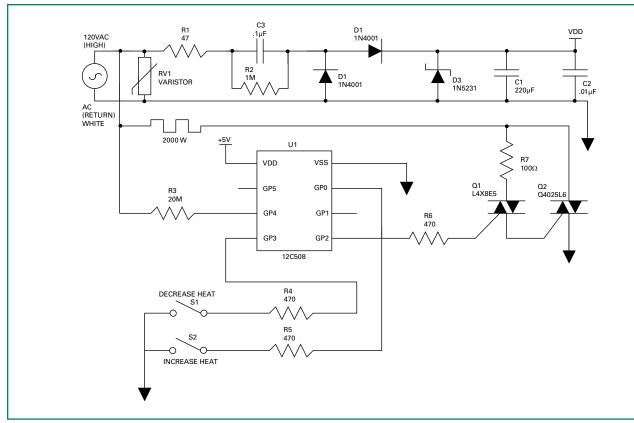

For higher amperage loads, a small 0.8 A, TO-92 Triac (operating in Quadrants I and IV) can be used to drive a 25 A alternistor Triac (operating in Quadrants I and III) as shown in the heater control illustration in Figure AN1003.24.

For a complete listing of the software used to control this circuit, see the Microchip application note PICREF-4. This application note can be downloaded from Microchip's Web site at www.microchip.com.

Figure AN1003.24 Microcontroller Heater Control

ittelfuse

Expertise Applied Answers Delivered

#### Summary

The load currents chosen for the examples in this application note were strictly arbitrary, and the component values will be the same regardless of load current except for the power Triac or SCR. The voltage rating of the power Thyristor devices must be a minimum of 200 V for 120 V input voltage and 400 V for 240 V input voltage.

The use of alternistors instead of Triacs may be much more acceptable in higher current applications and may eliminate the need for any dv/dt snubber network.

For many electrical products in the consumer market, competitive Thyristor prices and simplified circuits make automatic control a possibility. These simple circuits give the designer a good feel for the nature of Thyristor circuits and their design. More sophistication, such as speed and temperature feedback, can be developed as the control techniques become more familiar. A remarkable phenomenon is the degree of control obtainable with very simple circuits using Thyristors. As a result, industrial and consumer products will greatly benefit both in usability and marketability.

## Mounting and Handling of Semiconductor Devices

#### Introduction

ttelfuse

Expertise Applied | Answers Delivered

Proper mounting and handling of semiconductor devices, particularly those used in power applications, is an important, yet sometimes overlooked, consideration in the assembly of electronic systems. Power devices need adequate heat dissipation to increase operating life and reliability and allow the device to operate within manufacturers' specifications. Also, in order to avoid damage to the semiconductor chip or internal assembly, the devices should not be abused during assembly. Very often, device failures can be attributed directly to a heat sinking or assembly damage problem.

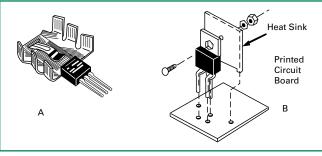

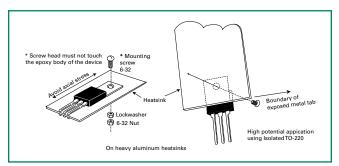

The information in this application note guides the semiconductor user in the proper use of Littelfuse devices, particularly the popular and versatile TO-220 and TO-218 epoxy packages.

Contact the Littelfuse Applications Engineering Group for further details or suggestions on use of Littelfuse devices.

#### Lead Forming — Typical Configurations

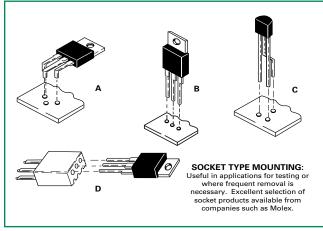

A variety of mounting configurations are possible with Littelfuse power semiconductor TO-92, DO-15, and TO- 220 packages, depending upon such factors as power requirements, heat sinking, available space, and cost considerations. Figure AN1004.1 shows typical examples and basic design rules.

Figure AN1004.1 Component Mounting

These are suitable only for vibration-free environments and low-power, free-air applications. For best results, the device should be in a vertical position for maximum heat dissipation from convection currents.

#### **Standard Lead Forms**

Littelfuse encourages users to allow factory production of all lead and tab form options. Littelfuse has the automated machinery and expertise to produce pre-formed parts at minimum risk to the device and with greater convenience for the consumer. See the "Lead Form Dimensions" section of this catalog for a complete list of readily available lead form options. Contact Littelfuse for information regarding custom lead form designs.

#### Lead Bending Method

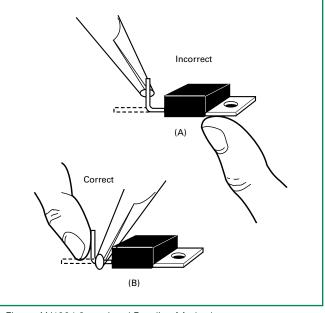

Leads may be bent easily and to any desired angle, provided that the bend is made at a minimum 0.063" (0.1" for TO-218 package) away from the package body with a minimum radius of 0.032" (0.040" for TO-218 package) or 1.5 times lead thickness rule. DO-15 device leads may be bent with a minimum radius of 0.050", and DO-35 device leads may be bent with a minimum radius of 0.028". Leads should be held firmly between the package body and the bend so that strain on the leads is not transmitted to the package body, as shown in Figure AN1004.2. Also, leads should be held firmly when trimming length.

Figure AN1004.2 Lead Bending Method

When bending leads in the plane of the leads (spreading), bend only the narrow part. Sharp angle bends should be done only once as repetitive bending will fatigue and break the leads.

#### **Heat Sinking**

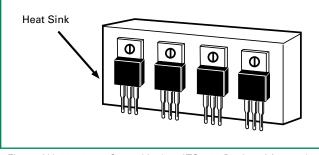

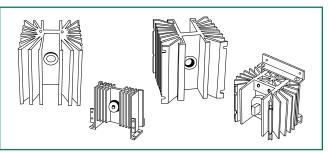

Use of the largest, most efficient heat sink as is practical and cost effective extends device life and increases reliability. In the illustration shown in Figure AN1004.3, each device is electrically isolated.

Figure AN1004.3 Several Isolated TO-220 Devices Mounted to a Common Heat Sink

#### Many power device failures are a direct result of

**improper heat dissipation.** Heat sinks with a mating area smaller than the metal tab of the device are unacceptable. Heat sinking material should be at least 0.062" thick to be effective and efficient.

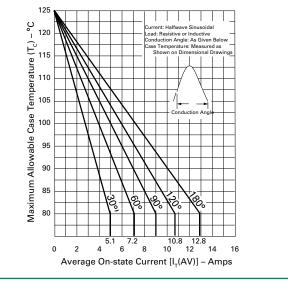

Note that in all applications the maximum case temperature (T<sub>c</sub>) rating of the device must not be exceeded. Refer to the individual device data sheet rating curves (T<sub>c</sub> versus I<sub>T</sub>) as well as the individual device outline drawings for correct T<sub>c</sub> measurement point.

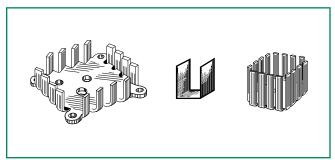

Figure AN1004.4 through Figure AN1004.6 show additional examples of acceptable heat sinks.

Figure AN1004.4 Examples of PC Board Mounts

Vertical Mount Heat Sink

Several types of vertical mount heat sinks are available. Keep heat sink vertical for maximum convection.

Figure AN1004.6

Examples of Extruded Aluminum

When coupled with fans, extruded aluminum mounts have the highest efficiency.

#### **Heat Sinking Notes**

Care should be taken not to mount heat sinks near other heat-producing elements such as power resistors, because black anodized heat sinks may absorb more heat than they dissipate.

Some heat sinks can hold several power devices. Make sure that if they are in electrical contact to the heat sink, the devices do not short-circuit the desired functions. Isolate the devices electrically or move to another location. Recall that the mounting tab of Littelfuse isolated TO-220 devices is electrically isolated so that several devices may be mounted on the same heat sink without extra insulating components. If using an external insulator such as mica, with a thickness of 0.004", an additional thermal resistance of 0.8° C/W for TO-220 or 0.5° C/W for TO-218 devices is added to the  $R_{\rm AlC}$  device rating.

Allow for adequate ventilation. If possible, route heat sinks to outside of assembly for maximum airflow.

#### Mounting Surface Selection

Proper mounting surface selection is essential to efficient transfer of heat from the semiconductor device to the heat sink and from the heat sink to the ambient. The most popular heat sinks are flat aluminum plates or finned extruded aluminum heat sinks.

The mounting surface should be clean and free from burrs or scratches. It should be flat within 0.002 inch per inch, and a surface finish of 30 to 60 microinches is acceptable. Surfaces with a higher degree of polish do not produce better thermal conductivity.

Many aluminum heat sinks are black anodized to improve thermal emissivity and prevent corrosion. Anodizing results in high electrical but negligible thermal insulation. This is an excellent choice for isolated TO-220 devices. For applications of non-isolated TO-220 devices where electrical connection to the common anode tab is required, the anodization should be removed. Iridite or chromate acid dip finish offers low electrical and thermal resistance. Either TO-218, Fastpak or TO-220 devices may be mounted directly to this surface, regardless of application. Both finishes should be cleaned prior to use to remove manufacturing oils and films. Some of the more economical heat sinks are painted black. Due to the high thermal resistance of paint, the paint should be removed in the area where the semiconductor is attached.

ttelfuse

Applied Answers Delivered

Bare aluminum should be buffed with #000 steel wool and followed with an acetone or alcohol rinse. Immediately, thermal grease should be applied to the surface and the device mounted down to prevent dust or metal particles from lodging in the critical interface area.

For good thermal contact, the use of thermal grease is essential to fill the air pockets between the semiconductor and the mounting surface. This decreases the thermal resistance by 20%. For example, a typical TO-220 with R<sub>eJC</sub> of 1.2 °C/W may be lowered to 1 °C/W by using thermal grease.

Littelfuse recommends Dow-Corning 340 as a proven effective thermal grease. Fibrous applicators are not recommended as they may tend to leave lint or dust in the interface area. Ensure that the grease is spread adequately across the device mounting surface, and torque down the device to specification.

Contact Littelfuse Applications Engineering for assistance in choosing and using the proper heat sink for specific application.

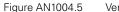

#### **Hardware And Methods**

#### **TO-220**

The mounting hole for the Teccor TO-220 devices should not exceed 0.140" (6/32) clearance. (Figure AN1004.7) No insulating bushings are needed for the L Package (isolated) devices as the tab is electrically isolated from the semiconductor chip. 6/32 mounting hardware, especially round head or Fillister machine screws, is recommended and should be torqued to a value of 6 inch-lbs.

Figure AN1004.7 TO-220 Mounting

Punched holes are not acceptable due to cratering around the hole which can cause the device to be pulled into the crater by the fastener or can leave a significant portion of the device out of contact with the heat sink. The first effect may cause immediate damage to the package and early failure, while the second can create higher operating temperatures which will shorten operating life. Punched holes are quite acceptable in thin metal plates where fineedge blanking or sheared-through holes are employed.

Drilled holes must have a properly prepared surface. Excessive chamfering is not acceptable as it may create a crater effect. Edges must be deburred to promote good contact and avoid puncturing isolation materials.

For high-voltage applications, it is recommended that only the metal portion of the TO-220 package (as viewed from the bottom of the package) be in contact with the heat sink. This will provide maximum oversurface distance and prevent a high voltage path over the plastic case to a grounded heat sink.

#### TO-218

The mounting hole for the TO-218 device should not exceed 0.164" (8/32) clearance. Isolated versions of TO-218 do not require any insulating material since mounting tab is electrically isolated from the semiconductor chip. Round lead or Fillister machine screws are recommended. Maximum torque to be applied to mounting tab should not exceed 8 inch-lbs.

The same precautions given for the TO-220 package concerning punched holes, drilled holes, and proper prepared heat sink mounting surface apply to the TO-218 package. Also for high-voltage applications, it is recommended that only the metal portion of the mounting surface of the TO-218 package be in contact with heat sink. This achieves maximum oversurface distance to prevent a high-voltage path over the device body to grounded heat sink.

#### **General Mounting Notes**

Care must be taken on TO-220 & TO-218 packages at all times to avoid strain to the mounting tab or leads. For easy insertion of the part onto the board or heat sink, avoid axial strain on the leads. Carefully measure holes for the mounting tab and the leads, and do any forming of the tab or leads before mounting. Refer to the "Lead Form Dimensions" section of this catalog before attempting lead form operations.

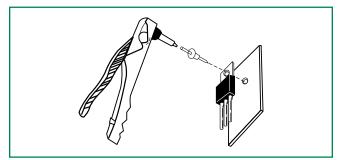

Rivets may be used for less demanding and more economical applications. 1/8" all-aluminum pop rivets can be used on both TO-220 and TO-218 packages. Use a 0.129"-0.133" (#30) drill for the hole and insert the rivet from the top side, as shown in Figure AN1004.9. An insertion tool, similar to a "USM" PRG 430 hand riveter, is recommended. A wide selection of grip ranges is available, depending upon the thickness of the heat sink material. Use an appropriate grip range to securely anchor the device, yet not deform the mounting tab. The recommended rivet tool has a protruding nipple that will

Littelfuse<sup>®</sup>

allow easy insertion of the rivet and keep the tool clear of the plastic case of the device.

Figure AN1004.9 Pop Riveting Technique

A Milford #511 (Milford Group, Milford, CT) semi-tubular steel rivet set into a 0.129" receiving hole with a riveting machine similar to a Milford S256 is also acceptable. Contact the rivet machine manufacturer for exact details on application and set-up for optimum results.

Pneumatic or other impact riveting devices are not recommended due to the shock they may apply to the device.

Under no circumstance should any tool or hardware come into contact with the case. The case should not be used as a brace for any rotation or shearing force during mounting or in use. Non-standard size screws, nuts, and rivets are easily obtainable to avoid clearance problems.

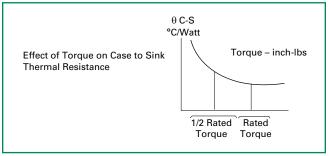

Always use an accurate torque wrench to mount devices. No gain is achieved by overtorquing devices. In fact, overtorquing may cause the tab and case to deform or rupture, seriously damaging the device. The curve shown in Figure AN1004.10 illustrates the effect of proper torque.

Figure AN1004.10 Effect of Torque to Sink Thermal Resistance

With proper care, the mounting tab of a device can be soldered to a surface. However, the heat required to accomplish this operation can damage or destroy the semiconductor chip or internal assembly. See "Surface Mount Soldering Recommendations" (AN1005) in this catalog.

Spring-steel clips can be used to replace torqued hardware in assembling Thyristors to heat sinks. Clips snap into heat sink slots to hold the device in place for PC board insertion. Clips are available in several sizes for various heat sink thicknesses and Thyristor case styles from *Aavid*  *Thermalloy* in Concord, New Hampshire. A typical heatsink is shown in Figure AN1004.11

Figure AN1004.11

Typical Heat Sink Using Clips

#### Soldering Of Leads

A prime consideration in soldering leads is the soldering of device leads into PC boards, heat sinks, and so on. Significant damage can be done to the device through improper soldering. In any soldering process, do not exceed the data sheet lead solder temperature of +280 °C for 10 seconds, maximum,  $\geq 1/16''$  from the case.

This application note presents details about the following three types of soldering:

- Hand soldering

- Wave soldering

- Dip soldering

#### Hand Soldering

This method is mostly used in prototype breadboarding applications and production of small modules. It has the greatest potential for misuse. The following recommendations apply to Littlefuse TO-92, TO-220, and TO-218 packages.

Select a small- to medium-duty electric soldering iron of 25 W to 45 W designed for electrical assembly application. Tip temperature should be rated from 600 °F to 800 °F (300 °C to 425 °C). The iron should have sufficient heat capacity to heat the joint quickly and efficiently in order to minimize contact time to the part. Pencil tip probes work very well. Neither heavy-duty electrical irons of greater than 45 W nor flame-heated irons and large heavy tips are recommended, as the tip temperatures are far too high and uncontrollable and can easily exceed the time-temperature limit of the part.

Littelfuse Fastpak devices require a different soldering technique. Circuit connection can be done by either quick-connect terminals or solder.

Since most quick-connect 0.250" female terminals have a maximum rating of 30 A, connection to terminals should be made by soldering wires instead of quick-connects.

Recommended wire is 10 AWG stranded wire for use with MT1 and MT2 for load currents above 30 A. Soldering

should be performed with a 100-watt soldering iron. The iron should not remain in contact with the wire and terminal longer than 40 seconds so the Fastpak Triac is not damaged.

For the Littelfuse TO-218X package, the basic rules for hand soldering apply; however, a larger iron may be required to apply sufficient heat to the larger leads to efficiently solder the joint.

Remember not to exceed the lead solder temperatures of +280 °C for 10 seconds, maximum,  $\geq$ 1/16" (1.59mm) from the case.

A 60/40 or 63/37 Sn/Pb solder is acceptable. This low melting-point solder, used in conjunction with a mildly activated rosin flux, is recommended.

Insert the device into the PC board and, if required, attach the device to the heat sink before soldering. Each lead should be individually heat sinked as it is soldered. Commercially available heat sink clips are excellent for this use. Hemostats may also be used if available. Needle-nose pliers are a good heat sink choice; however, they are not as handy as stand-alone type clips.

In any case, the lead should be clipped or grasped between the solder joint and the case, as near to the joint as possible. Avoid straining or twisting the lead in any way.

Use a clean pre-tinned iron, and solder the joint as quickly as possible. Avoid overheating the joint or bringing the iron or solder into contact with other leads that are not heat sinked.

#### Wave Solder

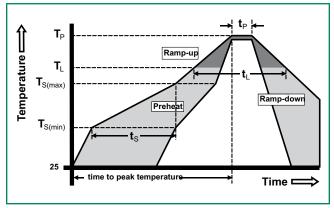

Wave soldering is one of the most efficient methods of soldering large numbers of PC boards quickly and effectively. Guidelines for soldering by this method are supplied by equipment manufacturers. The boards should be pre-heated to avoid thermal shock to semiconductor components, and the time-temperature cycle in the solder wave should be regulated to avoid heating the device beyond the recommended temperature rating. A mildly activated resin flux is recommended. Figures AN1004.12 and .13 show typical heat and time conditions.

Figure AN1004.12 Reflow Soldering with Pre-heating

| Reflow Co                                                       | ndition                                    | Pb – Free assembly |  |  |  |

|-----------------------------------------------------------------|--------------------------------------------|--------------------|--|--|--|

|                                                                 | -Temperature Min (T <sub>s(min)</sub> )    | 150°C              |  |  |  |

| Pre Heat                                                        | -Temperature Max (T <sub>s(max)</sub> )    | 200°C              |  |  |  |

|                                                                 | -Time (min to max) (t <sub>s</sub> )       | 60 – 190 secs      |  |  |  |

| Average ra<br>(T <sub>L</sub> ) to pea                          | amp up rate (LiquidusTemp<br>k             | 5°C/second max     |  |  |  |

| T <sub>S(max)</sub> to T <sub>L</sub>                           | - Ramp-up Rate                             | 5°C/second max     |  |  |  |

| Reflow                                                          | - Temperature (T <sub>L</sub> ) (Liquidus) | 217°C              |  |  |  |

| Rellow                                                          | -Time (min to max) (t <sub>s</sub> )       | 60 – 150 seconds   |  |  |  |

| PeakTemp                                                        | erature (T <sub>P</sub> )                  | 260 °C             |  |  |  |

| Time within 5°C of actual peak<br>Temperature (t <sub>p</sub> ) |                                            | 20 – 40 seconds    |  |  |  |

| Ramp-down Rate                                                  |                                            | 5°C/second max     |  |  |  |

| Time 25°C to peak Temperature (T <sub>P</sub> )                 |                                            | 8 minutes Max.     |  |  |  |

| Do not exceed                                                   |                                            | 280°C              |  |  |  |

| Figure AN1004.13 Heat and Time Table                            |                                            |                    |  |  |  |

Figure AN1004.13 Heat and Time Table

#### **Dip Soldering**

Dip soldering is very similar to wave soldering, but it is a hand operation. Follow the same considerations as for wave soldering, particularly the time-temperature cycle which may become operator dependent because of the wide process variations that may occur. This method is not recommended.

Board or device clean-up is left to the discretion of the customer. Littelfuse devices are tolerant of a wide variety of solvents, and they conform to MIL-STD 202E method 215 "Resistance to Solvents."

## **Surface Mount Soldering Recommendations**

#### Introduction

Expertise Applied | Answers Delivered

The most important consideration in reliability is achieving a good solder bond between surface mount device (SMD) and substrate since the solder provides the thermal path from the chip. A good bond is less subject to thermal fatiguing and will result in improved device reliability.

The most economic method of soldering is a process in which all different components are soldered simultaneously, such as DO-214, Compak, TO-252 devices, capacitors, and resistors.

#### **Reflow Of Soldering**

The preferred technique for mounting microminiature components on hybrid thick- and thin-film is reflow soldering.

The DO-214 is designed to be mounted directly to or on thick-film metallization which has been screened and fired on a substrate. The recommended substrates are Alumina or P.C. Board material.

Recommended metallization is silver palladium or molymanganese (plated with nickel or other elements to enhance solderability). For more information, consult Du Pont's Thick-Film handbook or the factory.

It is best to prepare the substrate by either dipping it in a solder bath or by screen printing a solder paste.

After the substrate is prepared, devices are put in place with vacuum pencils. The device may be laid in place without special alignment procedures since it is selfaligning during the solder reflow process and will be held in place by surface tension.

For reliable connections, keep the following in mind:

- Maximum temperature of the leads or tab during the soldering cycle does not exceed 280 °C.

- (2) Flux must affect neither components nor connectors.

- (3) Residue of the flux must be easy to remove.

Good flux or solder paste with these properties is available on the market. A recommended flux is Alpha 5003 diluted with benzyl alcohol. Dilution used will vary with application and must be determined empirically.

Having first been fluxed, all components are positioned on the substrate. The slight adhesive force of the flux is sufficient to keep the components in place.

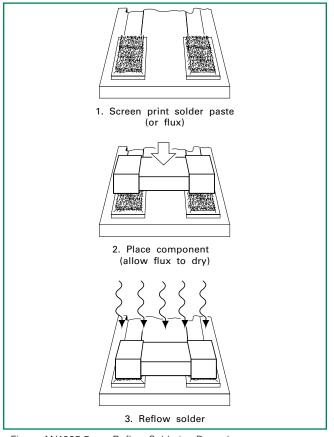

Because solder paste contains a flux, it has good inherent adhesive properties which eases positioning of the components. Allow flux to dry at room temperature or in a 70 °C oven. Flux should be dry to the touch. Time required will depend on flux used. With the components in position, the substrate is heated to a point where the solder begins to flow. This can be done on a heating plate, on a conveyor belt running through an infrared tunnel, or by using vapor phase soldering.

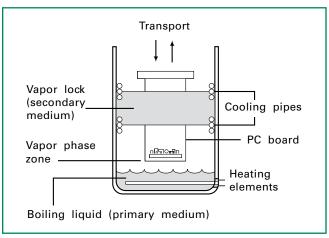

In the vapor phase soldering process, the entire PC board is uniformly heated within a vapor phase zone at a temperature of approximately 215 °C. The saturated vapor phase zone is obtained by heating an inert (inactive) fluid to the boiling point. The vapor phase is locked in place by a secondary vapor. (Figure AN1005.1) Vapor phase soldering provides uniform heating and prevents overheating.

Figure AN1005.1 Principle of Vapor Phase Soldering

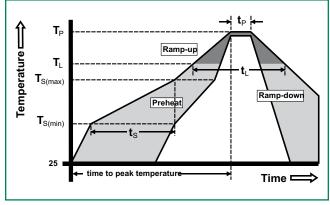

No matter which method of heating is used, the maximum allowed temperature of the plastic body must not exceed 250 °C during the soldering process. For additional information on temperature behavior during the soldering process, see Figure AN1005.2 and Figure AN1005.3.

| Reflow Co                                                       | ndition                                   | Pb – Free assembly |  |

|-----------------------------------------------------------------|-------------------------------------------|--------------------|--|

|                                                                 | -Temperature Min (T <sub>s(min)</sub> )   | 150°C              |  |

| Pre Heat                                                        | -Temperature Max (T <sub>s(max)</sub> )   | 200°C              |  |

|                                                                 | -Time (min to max) (t <sub>s</sub> )      | 60 – 190 secs      |  |

| Average ramp up rate (Liquidus Temp<br>(T,) to peak             |                                           | 5°C/second max     |  |

| T <sub>S(max)</sub> to T <sub>L</sub> - Ramp-up Rate            |                                           | 5°C/second max     |  |

| Reflow                                                          | -Temperature (T <sub>L</sub> ) (Liquidus) | 217°C              |  |

|                                                                 | -Time (min to max) (t <sub>s</sub> )      | 60 – 150 seconds   |  |

| Peak Temperature (T <sub>P</sub> )                              |                                           | 260 °C             |  |

| Time within 5°C of actual peak<br>Temperature (t <sub>n</sub> ) |                                           | 20 – 40 seconds    |  |

| Ramp-down Rate                                                  |                                           | 5°C/second max     |  |

| Time 25°C to peak Temperature (T <sub>P</sub> )                 |                                           | 8 minutes Max.     |  |

| Do not exceed                                                   |                                           | 280°C              |  |

#### **Reflow Soldering Zones**

#### Zone 1: Initial Pre-heating Stage (25 °C to 150 °C)

- Excess solvent is driven off.

- PCB and Components are gradually heated up.

- Temperature gradient shall be <2.5 °C/Sec.

#### Zone 2: Soak Stage (150 °C to 180 °C)

- Flux components start activation and begin to reduce the oxides on component leads and PCB pads.

- PCB components are brought nearer to the temperature at which solder bonding can occur.

- Soak allows different mass components to reach the same temperature.

- Activated flux keeps metal surfaces from re-oxidizing.

#### Zone 3: Reflow Stage (180 °C to 235 °C)

- Paste is brought to the alloy's melting point.

- Activated flux reduces surface tension at the metal interface so metallurgical bonding occurs.

#### Zone 4: Cool-down Stage (180 °C to 25 °C)

Assembly is cooled evenly so thermal shock to the components or PCB is reduced.

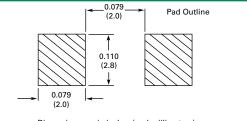

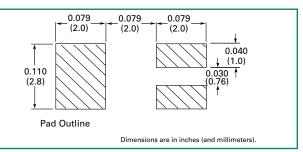

The surface tension of the liquid solder tends to draw the leads of the device towards the center of the soldering area and so has a correcting effect on slight mispositionings. However, if the layout is not optimized, the same effect can result in undesirable shifts, particularly if the soldering areas on the substrate and the components are not concentrically arranged. This problem can be solved by using a standard contact pattern which leaves sufficient scope for the self-positioning effect (Figure AN1005.3 and Figure AN1005.4) Figure AN1005.5 shows the reflow soldering procedure.

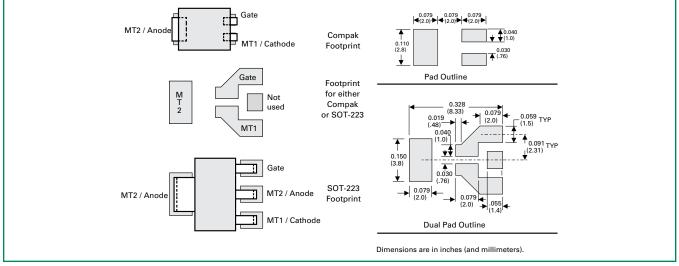

Dimensions are in inches (and millimeters).

Minimum Required Dimensions of Metal Connection of Typical DO-214 Pads on Hybrid Thick- and Thin-film Substrates

Figure AN1005.4 Modified DO-214 Compak — Three-leaded Surface Mount Package

Figure AN1005.5

Reflow Soldering Procedure

After the solder is set and cooled, visually inspect the connections and, where necessary, correct with a soldering iron. Finally, the remnants of the flux must be removed carefully.

Use vapor degrease with an azeotrope solvent or equivalent to remove flux. Allow to dry.

ittelfuse

Expertise Applied | Answers Delivered

After the drying procedure is complete, the assembly is ready for testing and/or further processing.

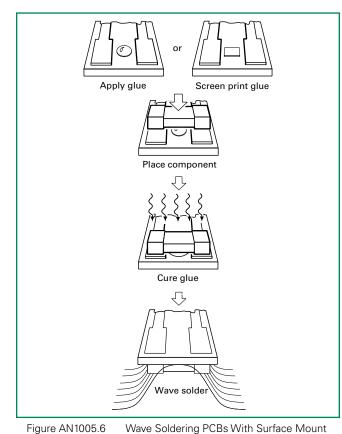

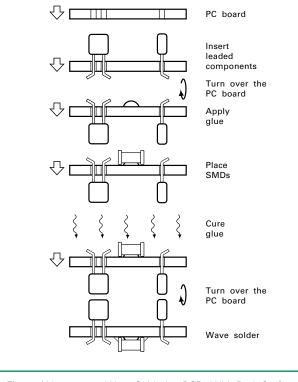

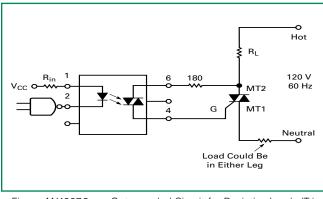

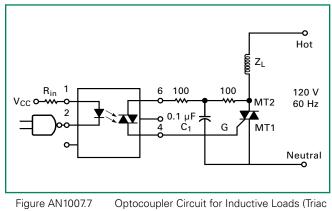

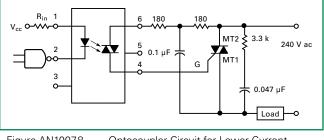

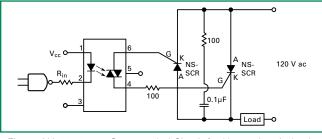

#### Wave Soldering