# Serial ATA II: Extensions to Serial ATA 1.0a

Revision 1.2 27-August-2004

Dell Computer Corporation

Intel Corporation

Maxtor Corporation

Seagate Technology

Vitesse Semiconductor Corporation

This 1.2 revision of the Serial ATA II: Extensions to Serial ATA 1.0a specification ("Final Specification") is available for download at www.serialata.org.

#### SPECIFICATION DISCLAIMER

THIS SPECIFICATION IS PROVIDED TO YOU "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMNETATION OF INFORMATION IN THIS SPECIFICATION. THE AUTHORS DO NOT WARRANT OR REPRESENT THAT SUCH USE WILL NOT INFRINGE SUCH RIGHTS. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS.

Copyright 2002-2004, Dell Computer Corporation, Intel Corporation, Maxtor Corporation, Seagate Technology LLC, Vitesse Semiconductor Corporation. All rights reserved.

For more information about Serial ATA, refer to the Serial ATA Working Group website at <a href="https://www.serialata.org">www.serialata.org</a>.

All product names are trademarks, registered trademarks, or servicemarks of their respective owners.

Serial ATA II Workgroup Extensions to Serial ATA 1.0a Technical Editor:

Amber Huffman Intel Corporation 2111 NE 25th Ave M/S JF2-53 Hillsboro, OR 97124 USA Tel: (503) 264-7929

Email: amber.huffman@intel.com

# **Table of Contents**

| 1. | Introd    | uction                                                    | 1    |

|----|-----------|-----------------------------------------------------------|------|

|    | 1.1. Goa  | als, Objectives, & Constraints                            | 1    |

|    | 1.2. Ref  | erences                                                   | 1    |

|    | 1.3. Defi | nitions, abbreviations, and conventions                   | 2    |

|    | 1.3.1.    | Definitions and Abbreviations                             | 2    |

|    | 1.3.2.    | Conventions                                               |      |

| 2. | Physic    | cal Layer                                                 | 4    |

|    | 2.1. Bac  | kplane Interconnect Reference                             | 4    |

|    | 2.1.1.    | Goals, Objectives, & Constraints                          |      |

|    | 2.1.2.    | Introduction                                              |      |

|    | 2.1.3.    | Storage Arrays                                            |      |

|    | 2.1.4.    | Conclusion & Recommendation                               |      |

|    | 2.2. Asy  | nchronous Signal Recovery (Optional)                      | 6    |

|    | 2.2.1.    | Host Phy Initialization State Machine                     |      |

|    | 2.2.2.    | Device Phy Initialization State Machine                   |      |

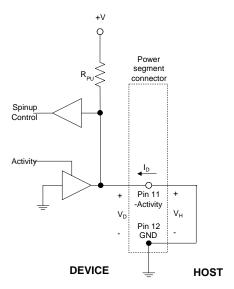

|    | 2.3. Dev  | ice Power Connector Pin 11 Definition (optional)          | . 15 |

|    | 2.3.1.    | Device Activity Signal (optional)                         | . 16 |

|    | 2.3.2.    | Staggered Spin-up Disable Control (optional)              | . 18 |

| 3. | Trans     | oort Layer                                                | . 20 |

|    | 3.1. Auto | o-Activate in DMA Setup FIS                               | . 20 |

|    | 3.2. Asy  | nchronous Notification                                    | . 21 |

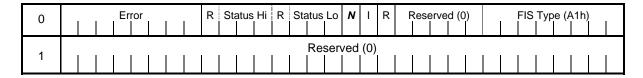

|    | 3.2.1.    | Set Device Bits FIS Enhancement                           | . 21 |

|    | 3.2.2.    | Notification Mechanism                                    | . 22 |

|    | 3.2.3.    | State Diagram for Asynchronous Notification               | . 22 |

|    | 3.2.4.    | ATAPI Notification                                        | . 23 |

|    | 3.3. Res  | erved FIS Types and Assignments                           | . 23 |

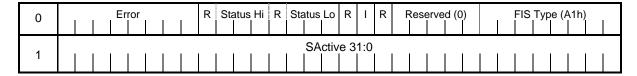

| 4. | Comm      | nand Layer                                                | . 24 |

|    | 4.1. Dev  | ice command layer protocol enhancements                   | . 24 |

|    | 4.2. Nati | ve Command Queuing                                        |      |

|    | 4.2.1.    | Goals, Objectives & Constraints                           |      |

|    | 4.2.2.    | Overview                                                  |      |

|    | 4.2.3.    | Definition                                                |      |

|    | 4.2.4.    | Intermixing Legacy Commands and Queued Commands           |      |

|    | 4.2.5.    | Command Definitions                                       |      |

|    | 4.2.6.    | State Diagrams for Command Queuing                        |      |

|    | 4.2.7.    | Host command layer protocol for command queuing           |      |

|    | 4.3. Phy  | Event Counters (Optional)                                 |      |

|    | 4.3.1.    | Counter Reset Mechanisms                                  |      |

|    | 4.3.2.    | Counter Identifiers                                       | . 53 |

|    | 4.3.3.    | READ LOG EXT Log Page 11h                                 |      |

|    | 4.4. Nor  | i-512 Byte Sector Size (Informative)                      | . 54 |

|    |           | NTIFY DEVICE/SET FÈATURES                                 |      |

|    | 4.5.1.    | Overview                                                  |      |

|    | 4.5.2.    | IDENTIFY DEVICE Definition                                |      |

|    | 4.5.3.    | IDENTIFY PACKET DEVICE Definition                         |      |

|    | 4.5.4.    | SET FEATURES Definition                                   |      |

|    | 4.5.5.    | READ LOG EXT Log Directory                                |      |

|    |           | ware Settings Preservation                                |      |

|    | 4.6.1.    | COMRESET Preservation Requirements                        |      |

|    | 4.7. Def  | ect Management (Informative)                              |      |

|    | 4.7.1.    | Overview (Informative)                                    |      |

|    | 4.7.2.    | Typical Serial ATA Reliability Metrics (Informative)      |      |

|    | 4.7.3.    | An Overview of Serial ATA Defect Management (Informative) |      |

|    | 4.7.4.    | Continuous Background Defect Scanning (Informative)       | . 67 |

| 4.7.5. Se                  | If-Monitoring, Analysis and Reporting Technology (Informative)    | 67  |

|----------------------------|-------------------------------------------------------------------|-----|

|                            | Configuration Overlay                                             |     |

|                            | finition                                                          |     |

|                            | troller Registers and Hardware Requirements                       |     |

|                            | r Definition                                                      |     |

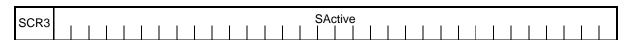

|                            | ctive register                                                    |     |

|                            | otification register                                              |     |

|                            | rror Register Enhancement for Device Change Detection             |     |

|                            | tatus Register Enhancement for Gen-2 Signaling Speed              |     |

|                            | Control Register Enhancement for Gen-2 Signaling Speed            |     |

| 5.2. HBA Er                | nforcement of FPDMA Data Phase Atomicity                          | 72  |

|                            | ansport Layer Accommodation for Asynchronous FIS Reception        |     |

|                            | arty DMA HBA Support (Informative)                                |     |

| <ol><li>Subsyste</li></ol> | m                                                                 | 76  |

|                            | ure Services/Management                                           |     |

|                            | als, Objectives, & Constraints                                    |     |

|                            | pology                                                            |     |

|                            | nitations                                                         |     |

|                            | finition                                                          |     |

| 6.1.5. SE                  | S and SAF-TE Extensions                                           | 85  |

|                            | closure Services Hardware Interface                               |     |

|                            | red Spin-up                                                       |     |

|                            | ctivity Indication                                                |     |

|                            | DD Activity Emulation of Desktop Behavior                         |     |

|                            | tivity/Status Indication Reference (Informative)                  |     |

|                            | g and Presence Detect                                             |     |

|                            | vice Requirements                                                 |     |

|                            | ceptacle Precharge (Informative)                                  |     |

| 6.4.3. Pre                 | esence Detection (Informative)                                    | 97  |

|                            | Backplane Interconnect Losses Estimations (Informative)           |     |

|                            | ology and Assumptions                                             |     |

|                            | nsidered Losses                                                   |     |

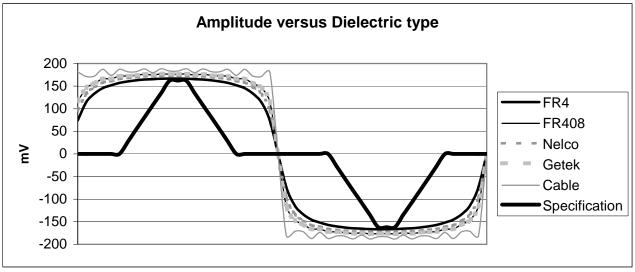

|                            | electric materials                                                |     |

|                            | ace widths                                                        |     |

| A.1.4 Ele                  | ectrical Specifications: Serial ATA 1.0a specification            | 100 |

|                            | Transmission deterioration over a backplane                       |     |

|                            | ceiver Sensitivity                                                |     |

|                            | ansmit Levels                                                     |     |

|                            | Sample Native Command Queuing Transaction Sequences (Informative) |     |

|                            | Sequences (Informative)                                           |     |

|                            | eued Commands with Out of Order Completion (Informative)          |     |

| B.1.2 Inte                 | errupt Aggregation (Informative)                                  | 104 |

## 1. Introduction

# 1.1. Goals, Objectives, & Constraints

This specification is one of a series of specifications that comprise Serial ATA II. This specification defines enhancements to the Serial ATA 1.0a specification that provide additional capabilities while retaining Serial ATA 1.0a compatibility and desktop cost structure

Additional features and capabilities are defined in a way that allow them to be selectively deployed, as business and market conditions require. Capabilities are defined in a way that costs associated with new feature support are incurred if and when the feature is implemented in order to realize customer benefit/value.

Some of the goals and requirements for the specification include:

- Compatibility must be maintained with Serial ATA 1.0a

- New features/capabilities must be separable/optional proper supersets of Serial ATA 1.0a

- Support for command queuing must be provided

- Means for supporting industry-standard enclosure services must be provided

- Device management expected of storage subsystems needs to be supported

## 1.2. References

This specification is an extension to the Serial ATA 1.0a specification. The Serial ATA 1.0a specification is presumed as the underlying baseline for this specification. This specification makes reference to the following specifications:

Serial ATA: High Speed Serialized AT Attachment revision 1.0a. Available for download at www.serialata.org.

Serial ATA II: Port Multiplier revision 1.0. Available for download at www.serialata.org.

AT Attachment with Packet Interface – 6 (ATA/ATAPI-6). Draft available at <a href="www.T13.org">www.T13.org</a>. Published ATA/ATAPI specifications available from ANSI at webstore.ansi.org or from Global Engineering.

SAF-TE – SCSI Accessed Fault-Tolerant Enclosure version 1.00 [revision R041497, April 14, 1997].

ANSI INCITS 305-1998, Information Technology – SCSI-3 Enclosure Services (SES) Command Set. Available from ANSI at webstore.ansi.org or from Global Engineering. Additional material and draft versions available from www.T10.org.

ANSI INCITS 230-1994 (R1999), Information Technology – Fibre Channel – Physical and Signaling Interface (FC-PH). Available from ANSI at webstore.ansi.org or from Global Engineering.

ANSI INCITS 301-1997, Information Technology – SCSI-3 Primary Commands (SPC). Available from ANSI at webstore.ansi.org or from Global Engineering.

I<sup>2</sup>C-Bus Specification version 2.1. Available from Philips Semiconductors at www.semiconductor.philips.com/buses/i2c.

IPMB - Intelligent Platform Management Bus Communications Protocol Specification version 1.0. Available for download at <a href="https://www.intel.com/design/servers/ipmi/spec.htm">www.intel.com/design/servers/ipmi/spec.htm</a>.

IPMI - Intelligent Platform Management Interface Specification version 1.5. Available for download at <a href="https://www.intel.com/design/servers/ipmi/spec.htm">www.intel.com/design/servers/ipmi/spec.htm</a>.

# 1.3. Definitions, abbreviations, and conventions

#### 1.3.1. Definitions and Abbreviations

The terminology used in this specification is consistent with the terminology used in the Serial ATA 1.0a specification, and all definitions and abbreviations defined in that specification are used consistently in this document. Additional terms and abbreviations introduced in this specification are defined in the following sections.

#### 1.3.1.1. Concentrator

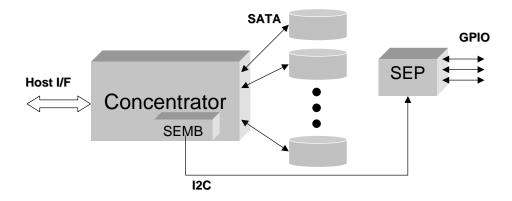

A concentrator is a generic term used to describe a logical block that has multiple Serial ATA ports to connect to Serial ATA devices plus some small number of ports to connect to a host. In the simplest case a concentrator may be a host bus adapter (HBA) that is plugged into the host that connects to some number of Serial ATA devices (like a PCI Serial ATA controller card). A concentrator may also be an internal or external RAID controller such as a fibre-channel to Serial ATA RAID controller, or may be some element that expands the number of ports through a fanout scheme.

#### 1.3.1.2. FPDMA Data Phase

The FPDMA Data Phase is the period from the reception of a DMA Setup FIS until either the exhaustion of the associated data transfer count or the assertion of the ERR bit in the shadow Status register.

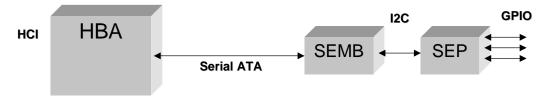

#### 1.3.1.3. HBA (Host Bus Adapter)

A Host Bus Adapter is a component that connects to the host system's expansion bus to provide connectivity for devices. Host Bus Adapters are also often referred to as controller cards or merely controllers.

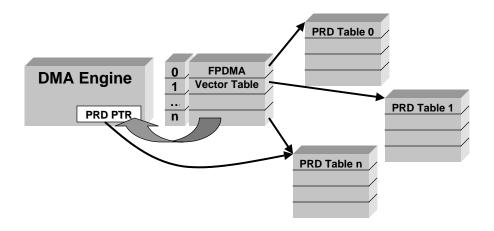

# 1.3.1.4. PRD (Physical Region Descriptor)

A Physical Region Descriptor table is a data structure used by DMA engines that comply with the SFF 8038i specification use to describe memory regions for transferring data to/from. A PRD table is also often referred to as a scatter/gather list.

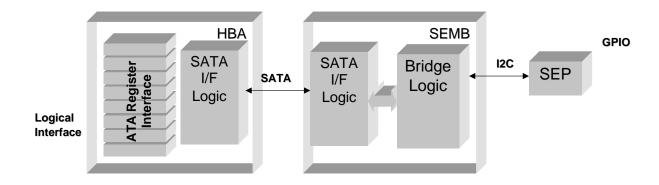

# 1.3.1.5. SEMB (Serial ATA Enclosure Management Bridge)

A SEMB is a logical block that translates Serial ATA transactions into I<sup>2</sup>C transactions to communicate enclosure services commands to a Storage Enclosure Processor.

# 1.3.1.6. SEP (Storage Enclosure Processor)

A SEP is a logical block that interfaces with the various enclosure sensors and actuators in an enclosure and is controlled through an I<sup>2</sup>C interface to the Serial ATA Enclosure Management Bridge.

## 1.3.2. Conventions

# 1.3.2.1. Register Naming Conventions

This specification uses the same naming conventions for the Command Block Registers as the Serial ATA 1.0a specification. However, the register naming convention is different from that used in the ATA/ATAPI-6 standard. Figure 1 defines the correspondence of the register names used in this specification with those used in the ATA/ATAPI-6 standard.

| Serial ATA register name | ATA/ATAPI-6 register name when writing registers | ATA/ATAPI-6 register name when reading registers |

|--------------------------|--------------------------------------------------|--------------------------------------------------|

| Features                 | Features Current                                 |                                                  |

| Features (exp)           | Features Previous                                |                                                  |

| Sector Count             | Sector Count Current                             | Sector Count HOB=0                               |

| Sector Count (exp)       | Sector Count Previous                            | Sector Count HOB=1                               |

| Sector Number            | LBA Low Current                                  | LBA Low HOB=0                                    |

| Sector Number (exp)      | LBA Low Previous                                 | LBA Low HOB=1                                    |

| Cylinder Low             | LBA Mid Current                                  | LBA Mid HOB=0                                    |

| Cylinder Low (exp)       | LBA Mid Previous                                 | LBA Mid HOB=1                                    |

| Cylinder High            | LBA High Current                                 | LBA High HOB=0                                   |

| Cylinder High (exp)      | LBA High Previous                                | LBA High HOB=1                                   |

| Device/Head              | Device                                           | Device                                           |

| Command                  | Command                                          | na                                               |

| Control                  | Control                                          | na                                               |

| Status                   | na                                               | Status                                           |

| Error                    | na                                               | Error                                            |

Figure 1 Register naming conventions and correspondence

# 2. Physical Layer

# 2.1. Backplane Interconnect Reference

## 2.1.1. Goals, Objectives, & Constraints

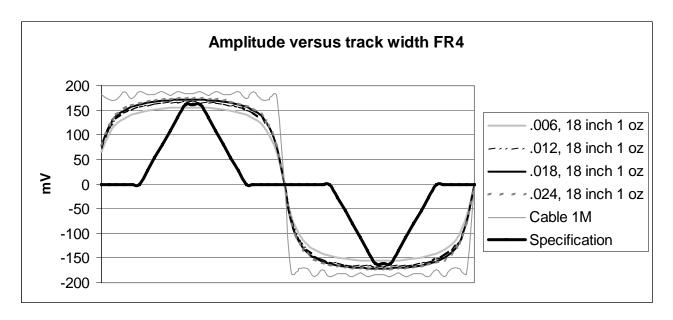

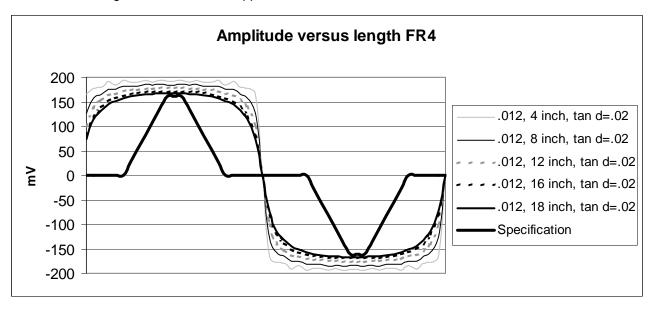

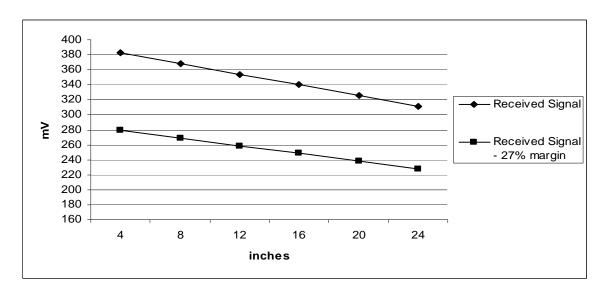

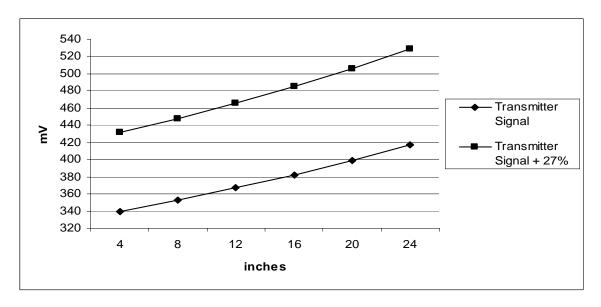

The Serial ATA 1.0a specification defines a cabled interconnect configuration and the corresponding Phy signaling parameters for that specific configuration. The parameters defined in the Serial ATA 1.0a specification do not directly apply to a backplane interconnect that has transmission characteristics substantially different from the cabled interconnect defined in the Serial ATA 1.0a specification. This section defines the host Phy parameters to accommodate a backplane interconnect of up to 18 inches in length. The solution is constrained to isolate all compensation for the losses and reflection characteristics of the backplane interconnect to the host side Phy, while leaving the device-side Phy wholly unchanged from that defined in the 1.0a specification.

#### 2.1.2. Introduction

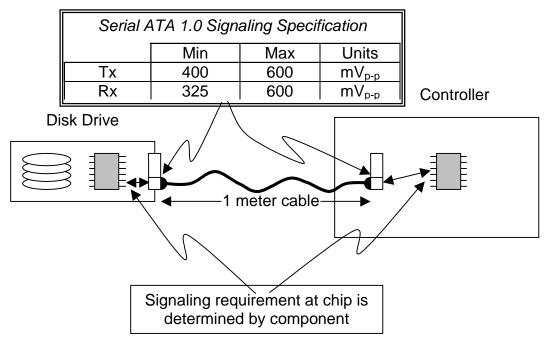

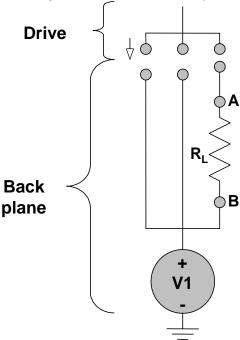

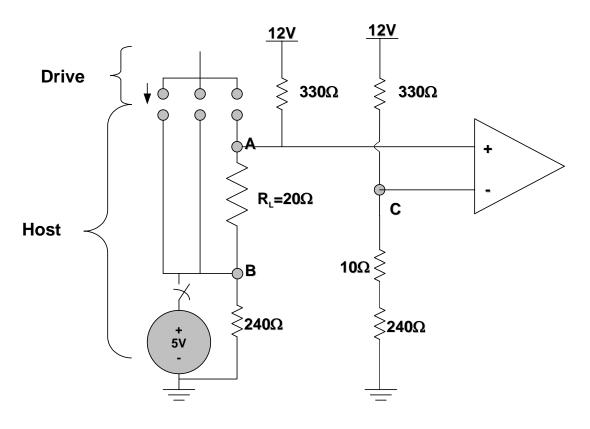

The Serial ATA 1.0a specification defines required signaling levels at the Serial ATA connector (see Figure 2). These parameters do not directly apply to the pins of the controller electronics and it is the responsibility of the interface component supplier to account for losses between the controller IC and the connector interface as part of the design collateral that accompanies the component.

This section provides additional host controller Phy parameter recommendations in order to promote timely and cost-effective solutions addressing the specific backplane requirements of storage subsystems. The overriding premise is that the device-side signal specification (at its connector) is an immutable given. All burdens for these new applications are placed upon the host-side controller.

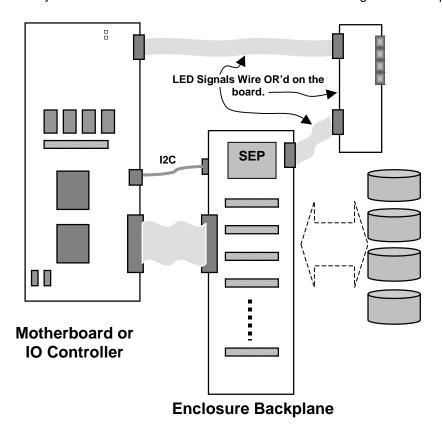

Figure 2 Interconnect configuration defined in Serial ATA 1.0a

## 2.1.3. Storage Arrays

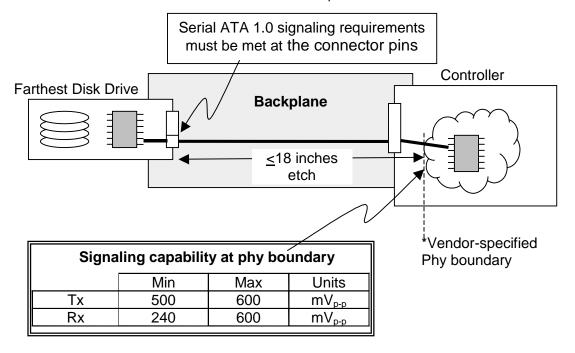

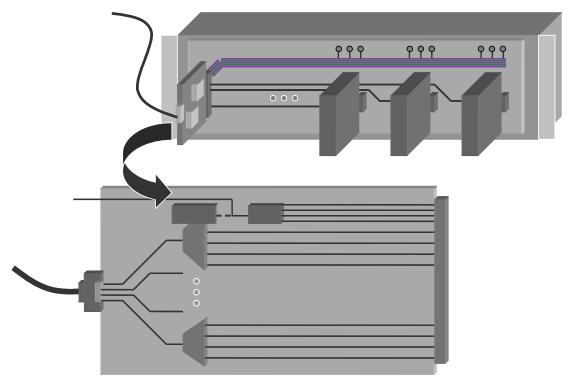

The application of Serial ATA to storage subsystems may include integration into backplane-based designs, typically 19-inch standard racks. A storage system may consist of an array of devices mounted side by side along the front panel of a 19-inch rack in order to allow any one of the devices to be removed. A backplane routes signals to each device from a central controller. In the worst case this controller could be positioned at one end of the device array, requiring routing from the controller silicon device to a connector on the backplane and then across the backplane. This type of application therefore defines a physical interconnect between the controller chip and the Serial ATA 1.0a device connector that consists of up to 18 inches of etch and one connector.

Figure 3 Definition reference configuration for multi-disk enclosure with internal controller using up to 18" of FR4 interconnect

#### 2.1.4. Conclusion & Recommendation

In order for a host controller to be able to reliably transmit to and receive from a Serial ATA 1.0a device within a backplane environment consisting of up to 18 inches of FR4 0.012 inch trace, greater minimum transmit levels and smaller minimum acceptable receive sensitivity levels are required. However, when that same host controller is applied in less lossy environments, the controller may run the risk of exceeding the maximum specified signal levels. This implies that it may be necessary for such a host controller to have a means of adjusting its signaling level as appropriate for the particular application. For example, the host controller may use an external set resistor that determines the transmit current level.

<sup>\*</sup>The vendor-specified Phy boundary encompasses design specific support elements including but not limited to coupling capacitors, compensating resistors, and tuned PCB trace geometries as part of the supplied controller component.

|                                                           | Nom Min Max Units Comments |                                 | Comments                        |

|-----------------------------------------------------------|----------------------------|---------------------------------|---------------------------------|

| Vdiff,tx - 400 500 600* mVp-p At host controller Phy bour |                            | At host controller Phy boundary |                                 |

| Vdiff,rx - 325 240 600 n                                  |                            | mVp-p                           | At host controller Phy boundary |

<sup>\*</sup> Maximum transmit voltage may be increased above specified maximum if means for ensuring that the specified maximum receiver voltage is not exceeded at the far end of the interconnect is provided. All other parameters are as specified in the Serial ATA 1.0a specification.

Figure 4 Host-controller 1.5 Gbps Phy specification recommendations for backplane application

# 2.2. Asynchronous Signal Recovery (Optional)

The Serial ATA 1.0a specification does not explicitly call out the Phy behavior for asynchronous signal recovery since the intended usage model for hot-plugging was insertion of a device into a receptacle where power would be applied as part of the insertion process.

Phys may optionally support Serial ATA II asynchronous signal recovery for those applications where the Serial ATA 1.0a usage model of device insertion into a receptacle (power applied at time of insertion) does not apply.

When signal is lost, both the host and the device may attempt to recover the signal. If the device attempts to recover the signal before the host by issuing a COMINIT, it is unclear what state the drive is in and whether the drive will return its signature. If a host supports asynchronous signal recovery, when the host receives an unsolicited COMINIT, the host shall issue a COMRESET to the device. An unsolicited COMINIT is a COMINIT that was not in response to a preceding COMRESET, as defined by the host not being in the HP2:HR\_AwaitCOMINIT state when the COMINIT signal is first received. As a consequence of the COMRESET, the device shall return its signature and will be in an unambiguous state.

When a COMRESET is sent to the device in response to an unsolicited COMINIT, the host shall set the Status register to 0x7F and shall set all other taskfile registers to 0xFF. When the COMINIT is received in response to the COMRESET, the Status register value shall be updated to either 0xFF or 0x80 to reflect that a device is attached.

## 2.2.1. Host Phy Initialization State Machine

Hosts that support asynchronous signal recovery have a modified Phy initialization state machine as defined in the following state diagram. Material depicted in bold italic typeface represents the changes from the behavior defined in the Serial ATA 1.0a specification.

As described in section 6.7.4.3 of the Serial ATA 1.0a specification, reception of a COMINIT signal shall cause the host to reinitialize communications with the device. Implementations that do not support asynchronous signal recovery shall unconditionally force the Host Phy state machine to transition to the HP2B:HR\_AwaitNoCOMINIT state when a COMINIT is received regardless of other conditions. Implementations that do support asynchronous signal recovery shall unconditionally force the Host Phy state machine to transition to the HP1:HR\_Reset state when an unsolicited COMINIT is received regardless of other conditions; if the COMINIT is not unsolicited the implementation shall force the Host Phy state machine to transition to the HP2B:HR\_AwaitNoCOMINIT state regardless of other conditions. Reception of COMINIT is effectively an additional transition into the HP2B:HR\_AwaitNoCOMINIT or HP1:HR\_Reset state that appears in every Host Phy state. For the sake of brevity, these implied transitions have been omitted from all the states.

A state variable called ResumePending is used to track whether the Host Phy has been to a power management state such that re-establishing communications is as a result of a resume

from a low power state. If a COMWAKE signal is not received when resuming from a low power state, the Host Phy must allow the device to retransmit COMWAKE and shall not initiate asynchronous signal recovery operations unless a COMRESET is explicitly triggered from a higher layer.

Designs that support asynchronous signal recovery have a state variable referred to as RetryInterval that determines the rate at which optional signal recovery polling is attempted. The value for RetryInterval is design specific but shall be no shorter than 10 ms. Implementations that do not implement optional retry polling may consider the RetryInterval value to be infinite.

| HP1: HR_Reset <sup>1</sup>                           | Transmit COMRESET <sup>2, 3, 4</sup> If asynchronous signal recovery is supported then clear ResumePending to 0. |  |                 |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|-----------------|

| Power-on reset and explicit reset request deasserted |                                                                                                                  |  | HR_AwaitCOMINIT |

| 2. Power-on reset or explicit reset request asserted |                                                                                                                  |  | HR_Reset        |

#### NOTE:

- 1. This state is entered asynchronously any time in response to power-on reset or an explicit reset request. For hosts supporting asynchronous signal recovery, this state is entered in response to receipt of a COMINIT signal from any state other than the HP2:HR\_AwaitCOMINITor the HP2B:HR\_AwaitNoCOMINIT state.

- 2. Must transmit COMRESET for a minimum of 6 bursts (and a multiple of 6)

- 3. As described in section 6.7.4.2 of the 1,0a specification, COMRESET may be transmitted for the duration of this state, or it may be transmitted starting in this state and cease transmission after departure of this state, or it may be transmitted upon departure of this state.

- 4. Hosts that support asynchronous signal recovery shall complete transmission of COMRESET in response to a received COMINIT that causes a transition to this state within 10 ms of the de-qualification of the received COMINIT signal.

| HP2: HR_AwaitCOMINIT Interface quiescent |                  |                                                                                                          |               |                   |

|------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|---------------|-------------------|

| 1.                                       | COMINIT detected | from device                                                                                              | $\rightarrow$ | HR_AwaitNoCOMINIT |

| 2.                                       | signal recovery  | cted from device and (asynchronous not supported or RetryInterval not htry into the HP2:HR_AwaitCOMINIT  |               | HR_AwaitCOMINIT   |

| 3.                                       |                  | detected from device and<br>signal recovery supported and<br>lapsed since entry into the<br>DMINIT state |               | HR_Reset          |

| HP2B:             |  |                  | Interface quiescent |               |                   |

|-------------------|--|------------------|---------------------|---------------|-------------------|

| HR_AwaitNoCOMINIT |  | NoCOMINIT        |                     |               |                   |

| COMINIT not dete  |  | COMINIT not dete | cted from device    | $\rightarrow$ | HR_Calibrate      |

| COMINIT detected  |  | COMINIT detected | d from device       | $\rightarrow$ | HR_AwaitNoCOMINIT |

#### NOTE:

1. For hosts that do not support asynchronous signal recovery, this state is entered asynchronously any time in response to COMINIT unless during a power-on reset or an explicit reset request (in which case HP1 is entered).

| HP3: | HR_Calibrate              | Perform calibration <sup>1</sup>  |               |                         |

|------|---------------------------|-----------------------------------|---------------|-------------------------|

|      | Calibration complete      | ete or bypass not implemented     | $\rightarrow$ | HR_COMWAKE              |

|      | Calibration not complete  |                                   |               | HR_Calibrate            |

|      | NOTE: 1. Calibration is o | ptional. If bypassed or not imple | mente         | ed, proceed directly to |

| HP4: HR_COMWAKE                  |                                 | COMWAKE             | Transmit COMWAKE |                   |  |

|----------------------------------|---------------------------------|---------------------|------------------|-------------------|--|

| COMWAKE not detected from device |                                 | etected from device | $\rightarrow$    | HR_AwaitCOMWAKE   |  |

|                                  | 2. COMWAKE detected from device |                     | $\rightarrow$    | HR_AwaitNoCOMWAKE |  |

| HP5: HR_AwaitCOMWAKE |                                |                                                                     |              |               |                   |

|----------------------|--------------------------------|---------------------------------------------------------------------|--------------|---------------|-------------------|

| 1. COMW              | AKE detected fr                | om device                                                           |              | $\rightarrow$ | HR_AwaitNoCOMWAKE |

| Retrylr              | hronous signa<br>terval not el | etected from<br>Il recovery not<br>apsed since e<br>AKE state or Re | ntry into th | or<br>e       | HR_AwaitCOMWAKE   |

| Retrylr<br>HP5:HI    |                                | al recovery su<br>ed since ent                                      | ry into th   | d<br>e        | HR_Reset          |

| HP5B:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interface quiescent  |               |                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|-------------------|

| HR_AwaitNoCOMWAKE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | _             |                   |

|                   | COMWAKE not of the control of t | letected from device | $\rightarrow$ | HR_AwaitAlign     |

| 2. COMWAKE detec  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | cted from device     | $\rightarrow$ | HR_AwaitNoCOMWAKE |

| T                                  | T                                                                     |               | . 2                     |

|------------------------------------|-----------------------------------------------------------------------|---------------|-------------------------|

| HP6: HR_AwaitAlign                 | Host transmits D10.2 characters at lowest supported rate <sup>2</sup> |               |                         |

| ALIGN detected f                   | om device (at any supported speed) <sup>3</sup>                       | $\rightarrow$ | HR_AdjustSpeed          |

| 2. ALIGN not dete                  | cted from device and 880us (32768                                     | $\rightarrow$ | HR_Reset <sup>1,4</sup> |

| ,                                  | has elapsed since entry to                                            |               |                         |

| HR_AwaitAlign                      |                                                                       |               |                         |

| <ol><li>ALIGN not detect</li></ol> | ted from device and less than 880us                                   | $\rightarrow$ | HR_AwaitAlign           |

| (32768 Gen1 d                      | words) has elapsed since entry to                                     |               |                         |

| HR_AwaitAlign                      |                                                                       |               |                         |

#### NOTE:

- 1. Host retries the power-on sequence indefinitely unless explicitly turned off by the application layer

- 2. Host must start transmitting d10.2 characters no later than 533ns (20 Gen1 dwords) after COMWAKE is deasserted as specified in the out of band signaling section

- 3. Host designers should be aware that the device is allowed 53.3ns (2 Gen1 dwords) after releasing COMWAKE (by holding the idle condition for more than 175ns) to start sending characters. Until this occurs, the bus will be at an idle condition and may be susceptible to crosstalk from other devices. Care must be taken so that crosstalk during this window doesn't result in a false detection of an ALIGN. For example: a compliant host may detect the deassertion of COMWAKE in as little as 112ns, such a host should wait at least 116.3ns (175+53.3-112) after detecting the release of COMWAKE to start looking for ALIGNs.

- 4. The Host PHY state machine may use the transition to HR\_Reset as a method of speed negotiation.

| HP7: HR_SendAlign                                                | Transmit ALIGN at speed detected              |               |                           |

|------------------------------------------------------------------|-----------------------------------------------|---------------|---------------------------|

| Three back-to-ba from device                                     | ck non-ALIGN primitives <sup>2</sup> detected | $\rightarrow$ | HR_Ready                  |

| Three back-to-back non-ALIGN primitives not detected from device |                                               |               | HR_SendAlign <sup>1</sup> |

#### NOTF :

- 1. Host retries indefinitely unless explicitly turned off by the application layer

- 2. Non-ALIGN primitives can be detected by the presence of the k28.3 control character in the byte0 position

| HP8: HR_F                                                                                                       | Ready                             | Transmit word from Link <sup>1</sup> . <i>If as supported then clear Resume</i>       |        |               |            |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------|--------|---------------|------------|

| 1.                                                                                                              | Partial signal from               | Link asserted                                                                         |        | $\rightarrow$ | HR_Partial |

| 2.                                                                                                              | Slumber signal from Link asserted |                                                                                       |        | $\rightarrow$ | HR_Slumber |

| 3. No power management request (asynchronous signal recovery no signal recovery poll not initiated of detected) |                                   | signal recovery not support                                                           | ted or | $\rightarrow$ | HR_Ready   |

| 4.                                                                                                              | asynchronous                      | nagement request received<br>signal recovery supported<br>not detected and signal red | and    | $\rightarrow$ | HR_Reset   |

# NOTE :

- 1. PhyRdy asserted only when in the HR\_Ready state and the Phy is maintaining synchronization with the incoming signal to its receiver and is transmitting a valid signal on its transmitter.

- 2. The latency at which a host elects to initiate an optional signal recovery poll is implementation specific but shall be greater than the ALIGN transmit interval.

| HP9: HR_Partia                                                                                                                              | Interface quiescent. If asynchronous supported then set ResumePendin           |               |                   |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|-------------------|

|                                                                                                                                             | al signal from Link deasserted and no COMWAKE<br>cted from device <sup>1</sup> | $\rightarrow$ | HR_COMWAKE        |

|                                                                                                                                             | al signal from Link deasserted and COMWAKE<br>cted from device <sup>1</sup>    | $\rightarrow$ | HR_AwaitNoCOMWAKE |

| 3. Parti                                                                                                                                    | al signal from Link asserted                                                   | $\rightarrow$ | HR_Partial        |

| NOTE:  1. Host Phy must remember if COMWAKE was detected during Partial to determine it wakeup request originated from the host or the Phy. |                                                                                |               |                   |

| HP10: HR_Slumber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interface quiescent. If asynchronous supported then set ResumePending |               |                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|-------------------|

| Slumber signal COMWAKE detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | from Link deasserted and no ted from device <sup>1,2</sup>            | $\rightarrow$ | HR_COMWAKE        |

| <ol> <li>Slumber signal from Link deasserted and COMWAKE detected from device<sup>1,2</sup></li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       | $\rightarrow$ | HR_AwaitNoCOMWAKE |

| <ol><li>Slumber signal from the signal from th</li></ol> | m Link asserted                                                       | $\rightarrow$ | HR_Slumber        |

#### NOTE:

- 1. Host Phy must remember if COMWAKE was detected during Slumber to determine if the wakeup request originated from the host or the Phy.

- 2. The host Phy may take this transition only after it has recovered from slumber mode and the Phy is prepared to initiate communications. If Phy has not yet recovered from the slumber mode it shall remain in this state.

|   | HP11: HR_AdjustSpeed                            |  | _AdjustSpeed      | Interface undefined but not quiescent <sup>1</sup> |               |              |

|---|-------------------------------------------------|--|-------------------|----------------------------------------------------|---------------|--------------|

| _ | 1 Transition to appre                           |  | Transition to app | ropriate speed completed                           | $\rightarrow$ | HR_SendAlign |

|   | 2 Transition to appropriate speed not completed |  | $\rightarrow$     | HR_AdjustSpeed                                     |               |              |

|   |                                                 |  |                   |                                                    |               |              |

#### NOTE:

1. Some implementations may undergo a transient condition where invalid signals are transmitted during the change in their internal transmission/reception speed. The host may transmit invalid signals for a period of up to 53ns (two Gen1 dwords) during the speed transition. Transmit jitter and unit interval timing requirements may not be met during this period but shall be met for all other bits transmitted in this state. A Phase shift may occur across the speed transition time.

# 2.2.2. Device Phy Initialization State Machine

Devices that support asynchronous signal recovery have a modified Phy initialization state machine as defined in the following state diagram. Material depicted in bold italic typeface represents the changes from the behavior defined in the Serial ATA 1.0a specification.

As described in section 6.7.4.2 of the 1.0a specification, reception of a COMRESET signal shall be treated by the device as a hard reset signal and shall unconditionally force the Device Phy state machine to transition to the DP1:DR\_Reset initial state regardless of other conditions. Reception of COMRESET is effectively an additional transition into the DP1:DR\_Reset state that appears in every Device Phy state. For the sake of brevity, this implied transition has been omitted from all the states.

| DP1: D                                         | PR_Reset <sup>1</sup>                                     | Interface quiescent |                 |        |               |                             |

|------------------------------------------------|-----------------------------------------------------------|---------------------|-----------------|--------|---------------|-----------------------------|

|                                                | COMRESET no deasserted                                    | t detected and      | power-on i      | reset  | $\rightarrow$ | DR_COMINIT                  |

| 2. COMRESET detected or power-on reset asserte |                                                           |                     | et asserted     |        | $\rightarrow$ | DR_Reset                    |

|                                                | NOTE:                                                     |                     |                 |        |               |                             |

|                                                | <ol> <li>This state is entered a COMRESET sign</li> </ol> |                     | any time in res | sponse | to p          | ower-on reset or receipt of |

| DP2: DR_COMINIT  | Transmit COMINIT <sup>1, 2</sup>                                                                                   |               |                 |

|------------------|--------------------------------------------------------------------------------------------------------------------|---------------|-----------------|

| 1. Unconditional |                                                                                                                    | $\rightarrow$ | DR_AwaitCOMWAKE |

| COMINIT signal w | for a 6 bursts duration tion 5.2 of the 1.0a specification, ithin 10 ms of the deassertion ceived COMRESET signal. |               |                 |

| _       | vaitCOMWAKE                                                                                                                        | Interface quiescent                                      |                     |                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|-------------------|

| 1. C    | COMWAKE detected from host                                                                                                         |                                                          |                     | DR_AwaitNoCOMWAKE |

| si      | COMWAKE not detected from host and (asynchronous signal recovery not implemented or RetryInterval not elapsed since entry into the |                                                          |                     | DR_AwaitCOMWAKE   |

| D       | P3:DR_AwaitC                                                                                                                       | OMWAKE state)                                            |                     |                   |

| as<br>R | synchronous s                                                                                                                      | signal recovery implemented a<br>lapsed since entry into | and →<br>and<br>the | DR_Reset          |

| DP3B                       | DP3B: DR_AwaitNoCOMWAKE                                                                    |                                                   |               |                   |                          |

|----------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------|---------------|-------------------|--------------------------|

|                            | 1.                                                                                         | COMWAKE not detected from host and part of power- | on            | $\rightarrow$     | DR_Calibrate             |

| l                          |                                                                                            | reset sequence <sup>1</sup>                       |               |                   |                          |

|                            | 2.                                                                                         | COMWAKE not detected from host and part           | of            | $\rightarrow$     | DR_COMWAKE               |

| ļ                          |                                                                                            | partial/slumber awake sequence <sup>1</sup>       |               |                   |                          |

| COMWAKE detected from host |                                                                                            |                                                   | $\rightarrow$ | DR_AwaitNoCOMWAKE |                          |

|                            | •                                                                                          | OTE :                                             |               |                   |                          |

| Į.                         | 1. Device must remember if it was sent to partial or slumber mode for proper wakeup action |                                                   |               |                   | or proper wakeup action. |

| DP4: DR_Calibrate           |                                                                                    | Perform calibration <sup>1</sup> |               |                           |

|-----------------------------|------------------------------------------------------------------------------------|----------------------------------|---------------|---------------------------|

|                             | Calibration complete or bypass not implemented                                     |                                  |               | DR_COMWAKE                |

| 2. Calibration not complete |                                                                                    |                                  | $\rightarrow$ | DR_Calibrate              |

|                             | NOTE:                                                                              |                                  |               | to I was a distributed of |

|                             | <ol> <li>Calibration is optional. If bypassed or not im<br/>DR_COMWAKE.</li> </ol> |                                  |               | ited, proceed directly to |

| DP5: | DR_COMWAKE    | Transmit COMWAKE |               |              |

|------|---------------|------------------|---------------|--------------|

|      | Unconditional |                  | $\rightarrow$ | DR_SendAlign |

| DP6: DR_SendAlign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                               | Transmit ALIGN <sup>1,2,3,5</sup>                                   |               |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------|----------------|

| ALIGN detected from host (device locked to incoming data) <sup>4</sup> 1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data)  1. ALIGN detected from host (device locked to incoming data) |                                                                                                                                                               |                                                                     | $\rightarrow$ | DR_Ready       |

| 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2. ALIGN not detected from host and ALIGN primitives transmitted for 54.6us (2048 <sup>5</sup> Gen1 ALIGN primitives) at speed other than lowest <sup>6</sup> |                                                                     | <b>→</b>      | DR_ReduceSpeed |

| <ol> <li>ALIGN not detected from host and ALIGN transmitted for 54.6us (2048<sup>5</sup> Gen1 ALIGN prin lowest speed<sup>6</sup></li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                               |                                                                     | <b>→</b>      | DR_Error       |

| 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                               | ted from host and ALIGN primitives ess than 54.6us (2048 Gen1 ALIGN | $\rightarrow$ | DR_SendAlign   |

#### NOTE:

- 1. ALIGN should be sent at the devices fastest supported speed first

- 2. ALIGNS should be sent only at valid frequencies (if PLL not locked, send D10.2)

- 3. After COMWAKE is released as specified in the out of band signaling section, the device must ensure the interface is active (not quiescent).

- 4. Device designers should be aware that the host is allowed 533ns (20 Gen1 dwords) after detecting the deassertion of COMWAKE to start sending d10.2 characters. Until this occurs, the bus will be at an idle condition and may be susceptible to crosstalk from other devices. Care must be taken so that crosstalk during this window doesn't result in a false detection of an ALIGN. Devices may extend this timeout up to an additional 54.6us (2048 Gen1 dwords) (for a max total of 109.2us), as necessary to allow their receiver time to lock to the host ALIGN.

- 5. Device must not leave the bus idle more than 53.3ns (2 Gen1 dwords) longer than the required 175ns to deassert COMWAKE.

- 6. If this is part of a device-initiated recovery from the Slumber or Partial power management state, the device Phy should resume at the speed previously negotiated and should not reduce its speed in response to failure to establish communications. Upon failing to establish communications it should instead transition directly to the DR\_Error state to initiate a re-try of the ComWake sequence.

| DP7: DR_Re | ady <sup>1</sup>                               | Transmit word from Link                               |            |              |     |            |  |  |  |

|------------|------------------------------------------------|-------------------------------------------------------|------------|--------------|-----|------------|--|--|--|

| 1. Pa      | artial signal from                             | Link asserted                                         |            | _            | → [ | DR_Partial |  |  |  |

| 2. S       | lumber signal fro                              |                                                       | → [        | OR_Slumber   |     |            |  |  |  |

| (a         | o power ma<br>esynchronous<br>eceived signal o |                                                       | <b>→</b> [ | DR_Ready     |     |            |  |  |  |

| as         |                                                | nagement request<br>signal recovery s<br>not detected |            | and _<br>and | > [ | DR_Error   |  |  |  |

#### NOTE:

1. PhyRdy asserted only when in the DR\_Ready state and the Phy is maintaining synchronization with the incoming signal to its receiver and is transmitting a valid signal on its transmitter.

| DP8: [ | DR_ | Partial                              | Interface quiescent              |               |                   |

|--------|-----|--------------------------------------|----------------------------------|---------------|-------------------|

|        | 1.  | Partial signal from                  | Link deasserted                  | $\rightarrow$ | DR_COMWAKE        |

|        | 2.  | Partial signal fro detected from hos | m Link deasserted and COMWA<br>t | KE →          | DR_AwaitNoCOMWAKE |

|        | 3.  | Partial signal from                  | Link asserted                    | $\rightarrow$ | DR_Partial        |

| DP9: I | DR_ | Slumber                                | Interface quiescent              |               |                   |

|--------|-----|----------------------------------------|----------------------------------|---------------|-------------------|

|        | 1.  | Slumber signal fro                     | m Link deasserted                | $\rightarrow$ | DR_COMWAKE        |

|        | 2.  | Slumber signal fr<br>detected from hos | om Link deasserted and COMWAKE t | $\rightarrow$ | DR_AwaitNoCOMWAKE |

|        | 3.  | Slumber signal fro                     | m Link asserted                  | $\rightarrow$ | DR_Slumber        |

| DP10 | : DR                                                                                    | _ReduceSpeed         | Interface quiescent                        |               |                           |  |  |  |  |

|------|-----------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------|---------------------------|--|--|--|--|

|      | 1.                                                                                      | Transition to legac  | cy (slower) speed complete                 | $\rightarrow$ | DR_SendAlign <sup>1</sup> |  |  |  |  |

|      | 2.                                                                                      | Transition to legac  | cy speed not complete                      | $\rightarrow$ | DR_ReduceSpeed            |  |  |  |  |

|      | NC                                                                                      | TE:                  |                                            |               |                           |  |  |  |  |