# Semiconductor Packaging Assembly Technology

## Introduction

This chapter describes the fundamentals of the processes used by National Semiconductor to assemble IC devices in electronic packages. Electronic packaging provides the interconnection from the IC to the printed circuit board (PCB). Another function is to provide the desired mechanical and environmental protection to ensure reliability and performance. Three fundamental assembly flow processes (*Table 1*) are covered in this chapter: 1) plastic leadframe-based packages, 2) plastic ball grid array (PBGA), and 3) hermetic packages.

TABLE 1. Assembly Flow Processes for Electronic Packages

| Plastic<br>(Leadframe)      | Plastic (BGA)                                 | Hermetic        |  |

|-----------------------------|-----------------------------------------------|-----------------|--|

| Wafer Sort                  | Wafer Sort                                    | Wafer Sort      |  |

| 2nd Optical                 | 2nd Optical                                   | 2nd<br>Optical  |  |

| Wafer Mount                 | Wafer Mount                                   | Wafer<br>Mount  |  |

| Wafer Sawing                | Wafer Sawing                                  | Wafer<br>Sawing |  |

| Die Attach                  | Die Attach                                    | Die Attach      |  |

| Wire Bond                   | Wire Bond                                     | Wire Bond       |  |

| 3rd Optical                 | 3rd Optical                                   | 3rd<br>Optical  |  |

| Encapsulate (Mold Compound) | Encapsulate (Mold<br>Compound or Glob<br>Top) | Lid Seal        |  |

| Dejunk                      | Ball Attach and<br>Reflow                     | Leakage<br>Test |  |

| Deflash                     | Singulate                                     |                 |  |

| Marking                     | Ball Inspection                               |                 |  |

| Plating                     | Marking                                       |                 |  |

| Trim and Form               |                                               |                 |  |

| Final Inspection            |                                               |                 |  |

The fundamental package assembly processes for lead-frame and hermetic packaging have remained relatively unchanged over the past 30 years, though the equipment and materials have undergone considerable advancement. Assembly equipment is no longer as labor intensive. Processing is typically carried out on automated equipment designed and manufactured for high-volume production. Materials are of higher purity and have properties tailored for a specific application.

# New Technology Introduction And Verification

Before implementing a new technology, either a material or an assembly technology, National Semiconductor utilizes a rigorous system to characterize and verify the suitability of the change for high-volume production.

#### 1. Feasibility

A preliminary analysis of the process or material is conducted to determine the feasibility of introducing a new or changing a material/process technology. This analysis includes a benchmark assessment of available and competing technologies.

#### 2. Prototypes

Prototype parts are assembled to provide an initial sample size for analysis.

#### Assembly

Parts are assembled in production equipment to further verify the technology change.

#### 4. Testing

Assembled devices are put through testing to ensure the integrity of the technology.

#### 5. Process Characterization

A full process characterization is conducted to determine the readiness of the new technology for high-volume manufacturing. This step utilizes design of experiment (DOE) methodologies.

#### 6. Manufacturing Verification

Production lots are assembled and put through the required qualification test to determine package reliability.

### 7. Production

After successfully completing the previous steps, the technology is released for full production.

# **Die Preparation**

Die preparation is common to all three types of process flows

First wafers are sorted at the assembly site and stored in a die bank. A 2nd optical visual inspection is conducted to inspect for defects before the wafers are released for production.

Next wafers are mounted on a backing tape that adheres to the back of the wafer. The backing/mounting tape provides support for handling during wafer saw and the die attach process.

The wafer saw process cuts the individual die from the wafer leaving the die on the backing tape. The wafer saw equipment consists of automated handling equipment, saw blade, and an image recognition system. The image recognition system maps the wafer surface to identify the areas to be cut, known as the saw street. DI Water is dispensed on the wafer during the saw process to wash away particles (Si

## Die Preparation (Continued)

Dust) and to provide lubrication during the dicing process. Wafers are dried by spinning the wafer at a high RPM before going to the die attach process.

# Plastic Leadframe-Based Packages DIE ATTACH

Die attach provides the mechanical support between the silicon die and the substrate, i.e,. leadframe, plastic or ceramic substrate. The die attach is also critical to the thermal and, for some applications, the electrical performance of the device.

#### Equipment

The die attach equipment is configured to handle the incoming wafer and substrate simultaneously. An image recognition system identifies individual die to be removed from the wafer backing/Mounting tape, while die attach material is dispensed in controled amounts on to the substrate. A non pierce through plunge up needle/s assists to separate an individual die to be picked by the collet on the pick-up head of the die attacher. Finally, the die is aligned in the proper orientation and position on the substrate.

#### **Materials**

The type of material used for die attach is a function of the package type and performance requirements. *Table 2* lists general materials for the various package types.

**TABLE 2. Overview of Die Attach Materials**

| Package Type    | Material         | Requirements  |

|-----------------|------------------|---------------|

| Plastic         | Epoxy (silver    | Low Moisture  |

| (Leadframe)     | filled) Modified | Absorption    |

|                 | Epoxies Cyanate  | Thermal       |

|                 | Ester Blends     | Dissipation   |

| Plastic (Power) | Solder (Soft     | Uniform       |

|                 | solders)         | Intermetallic |

|                 |                  | Formation     |

|                 |                  | Thermal       |

|                 |                  | Dissipation   |

The epoxy and cyanate ester are two types of polymers used as a die attach between the die and the leadframe. Depending on the leadframe design, adhesion may be directly to copper, silver plating, or palladium plating. Die attach materials are filled with silver particles to increase the thermal dissipation properties. Material is dispensed from syringes in controlled amounts. These materials have defined shelve lifes and, therefore, the recommended guidelines must be followed when handling in a manufacturing environment. After placement of the die, the die attach is cured; typical cure temperatures are in the 125-175°C range

Some power packages use soft solders as the die attach material between the die and the leadframe. These materials are lead-tin based and provide an excellent mechanical bond with superior thermal dissipation properties compared to polymer die attach. A wafer back metal is required to form the bond between the solder and the wafer. An intermetallic layer forms between two interfaces to provide the mechanical strength needed for die attach: 1) between the solder and the wafer backmetal and 2) the solder and the leadframe. The solder die attach equipment dispenses the solder in wire or ribbon form onto the leadframe. Temperatures used in solder die attach range from 260°C to 345°C depending on the solder metallurgy used.

#### Quality

The coverage of the material dispensed during the die attach process is critical to the reliability and performance of the package. The presence of voids and variations in thickness are undesirable. Excessive or insufficient coverage of the die attach material makes the device susceptible to reliability failures. The adhesion strength of the die attach is weakened by the presence of voids, particularly during temperature cycle excursions, and can impact the ability of the die attach material to dissipate heat away from the device. Lack of thickness control can contribute to reliability failures and impact the subsequent wire bond process. Typical Bond line thickness is between 1 to 2 mils.

#### **WIRE BOND**

Wire bonds are the most common means of providing an electrical connection from the IC device to the substrate/ Leadframe. The wire bond process must achieve high throughputs and production yields to be acceptable on a cost basis. High-speed wire bond equipment consists of a handling system to feed the substrate/leadframe into the work area. Image recognition systems ensure the die is orientated to match the bonding diagram for a particular device. Wires are bonded one wire at a time.

#### **Process**

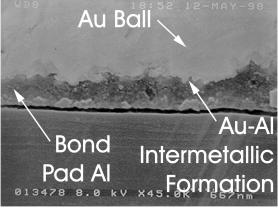

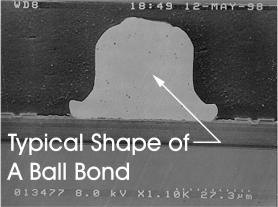

Thermosonic bonding is used with gold and copper wire. The wire is fed through a ceramic capillary. A combination of temperature and ultrasonic energy forms the metallic wire bond. For each interconnection two wire bonds are formed, one at the die and the other at the leadframe/substrate. The first bond involves the formation of a ball with an electric flameoff (EFO) process. The ball is placed in direct contact within the bond pad opening on the die, under load (Bond Force) and ultrasonic energy within a few milliseconds (Bond Time) & forms a ball bond at the Al bond pad metal. The Bond Force, US Power & Time forms a Au-Al intermetallic layer that makes the connection on the Bond Pad of the Die. The wire is then lifted to form a loop and then is placed in contact with the desired bond area of the leadframe/substrate to form a wedge bond. Bonding temperature, ultrasonic energy, and bond force & Time are key process parameters controlled to form a reliable connection from the Die to the Leadframe/Substrate. The Shape of the loop for a specific capability is controlled by the software that drives the motion of the bondhead. The Ball Bond reliability at 1st bond (ball Bond) & 2nd bond (wedge) is very sensitive to any movement of the Die or the Substrate/leadframe. So during wire bond operation, the die & the substrate/leadframe must be held rigidly.

Next major issue with regards to 1st bond reliability is the Brittle intermetallic (Purple Plague; AuAl2) formation. The Au-Al ntermetallic formation has 5 different phases (Au5Al2,Au2Al,AuAl2,AuAl & Au4Al). Au-Al phase changes are a factor of temperature & time. So if the bonds are heated at a high temperature (350°C) over a period of 5 hrs, it will form a brittle Au-Al intermetallic phase & form voids within the ball bond & finally lifts the ball & opens the connection. This will result in failure of the device. The desired intermetallic formation which will form a reliable bonds are Au5Al2 & Au2Al.

MS011900

MS011800-5

FIGURE 1. Shows a cross section of a Au-Al bond

Ultrasonic bonding is used to form aluminum wire bonds. There is no heat needed to diffuse the Al wire into the Al bond pad. The Al-Al bonds are mechanically welded. The wire is placed in direct contact with the bonding tool and the bond pad. Application of ultrasonic energy forms a wedge bond.

#### **Bond Pad Metallurgy**

The type and cleanliness of the aluminum bond pad metallization are important factors to be considered in forming this first wire bond. The bonding force and ultrasonic energy are optimized for the bond pad metallurgy. Attributes effecting the bond pad metallization include alloy content, grain size, underlying metallurgy, and surface roughness and cleanliness. Typically all of National Semiconductor Devices are Cu Doped up to 0.5%. Some customized process technologies may be different which require up to 1% of Si doping. Top layer Bond Pad Metallization Thickness & all of the metal Structure is also critical to the bond integrity. Thicker Top layer metallization & a robust structure is ideal to avoid any lifted Bonds or Bond Cratering which is a phenomena where damages are seen in the underlying structure under the top layer metal.

#### **Materials**

The mechanical properties and diameter of the wire are important wire attributes that impact the bonding process and yield. Gold wire is 99.99% pure with 100 ppm dopant level. The dopants impart the desired mechanical properties without severely limiting the electrical conductivity. Copper wire requires an inert gas environment to prevent oxidation.

#### Quality

Several methods are employed to evaluate and ensure the integrity of the wire bond process.

#### 1. Visual Inspection

Visual techniques are used to ensure the proper ball and wedge bonds have been formed. Visual inspection also verifies the bonds are properly placed with respect to the bond pads & Bond Fingers of the leadframe/substrate. Besides that, the visual inspection also screens possible bond defects that may results to an open or short based on a specified defined criteria of wire clearance & close proximity of each bond to the other.

#### 2. Pull Test

The wire pull test is used to measure the strength and failure mode of the wire bond. A small hook is attached to the wire loop and pulled. The hook is generally placed at the highest point close to the 1st bond to gauge the strength of the 1st bond or next to the wedge at the 2nd bond to ensure a reliable weld. Generally, if the hook is placed at the mid span of the wire, then the test will show the weakest link of the bond. This is typically either the neck of the ball bond (right above the ball) or at the heel of the wedge bond. The Pull test is basically a function of the wire diameter. Loop height & wire span are the most significant factors that determines the strength of a wire for a given wire diameter. Shorter span & a lower loop will result in a lower pull strength. As opposed to a longer span & a higher loop height which will result in higher pull strength. Pull Test is a destructive test & it's a Statistical Process Control monitor at all of National Semiconductors' Assembly sites. Min. Pull for 0.9, 1.0 & 1.3 mils wire diameters are 3.0, 4.0 & 5.0 gm respectively. Besides the gm Force value, the pull test modes are also recorded & monitored regularly. Pull Test parameters like pull speed must be optimized for best results. This test monitors the quality of the wire bond process.

#### 3. Ball Shear Test

Ball shear test is another method for evaluating the quality of a ball bond. A shear tool is aligned adjacent to the ball bond and a force is applied. The bond strength and failure mode are measures of the ball bond quality. Ball Shear Data reflects the intermetalic formation & its coverage of the bonds. So a larger ball should have a higher shear strength based on a larger area of intermetalic formation between the Au ball & Al bond pad metal. The ball shear is gauged by gm Force over the area of the ball formation. Based on reliability data, 6gm/sq mil ball shear over an area will result in a reliable interconnect. Just like pull test, Ball shear test is also a destructive test. The Shear Force/gm is recorded on a Statistical Process Control Chart & monitored regularly. The shear modes of Au on the bond pad after the shear is also recorded on the SPC charts. Ball shear results are best if the Shear tool is 1 mil smaller than the desired ball size being sheared & the tool is setback to at least 3 micron from the shear surface prior to shear. Like Pull Test, shear speed & shear distance must be optimized for best results. This Test also monitors the quality of the wire bond process.

3 www.national.com

#### 4. Bake Test

Wire pull and ball shear are also employed not only to measure the quality of the wire bond but used to evaluate the long-term quality following a bake test. During the bonding process and during subsequent exposures to elevated temperatures, intermetalic compounds form along the gold wire-aluminum bond pad interface. These intermetalic layers, which are a function of temperature & time are necessary in achieving the desired bond strength, but are also prone to void formation when aged at elevated temperatures.

The void formation is referred to as Kirkendahl voiding and is caused by the rapid diffusion of aluminum into the intermetalic phase. If excessive diffusion of aluminum occurs, voids accumulate along with the intermetalic, and weaken the wire bond. To ensure the long-term reliability of wire bonds, samples are tested at evaluated temperatures like 175°C at 5 to 24 hrs depending on package or device, and bond strengths characterized by wire pull and ball shear.

#### Nickel Decoration

A nickel decoration test is employed to determine if the bonding process has induced cratering within the bond pad. Cratering is the cracking and failure of the glass layers underlying the bond pad because of excessive bond US Power/force during the wire bond process. Nickel decoration involves the wet etching of the aluminum metallization and the deposition of a thin nickel layer. This layer will highlight the presence of cracks in the underlying dielectric. Aluminum bond pads without a titanium-tungsten underlayer are particularly prone to the cratering problem and require tight wire bond process windows to avoid this problem. Increasing the aluminum thickness is one solution to eliminate cratering, though this option may not always be desirable.

#### Fine Pitch Wire Bonding

To support the need to increase the functions on single Si devices, the number of bond pads will have to increase to accommodate the added functions. The impact of increasing the number of bond pads will result in larger die sizes, increasing the cost of Si. This raises the need to optimize the resulting layouts to overcome this cost impact.

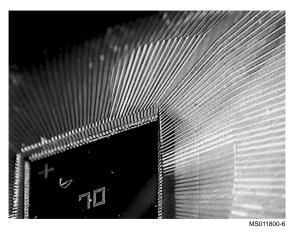

Based on all the optimization, the bond pad must be packed closer which means reducing the bond pad pitches, bond pad metal & passivation sizes. There are 2 alternatives to doing this. First, if the density of the circuit is core limited, than the bond pad layout will be maintained in an in-line configuration with much smaller pitch. Typically the standard bond pad pitches are 100 to 125 micron. In a fine pitch layout the bond pad pitches will now be reduce to 80 to 90 micron. Assembly Sites are qualified to assemble high volume products with 90 micron in-line bond pad pitch. 80 micron in-line pitch is also qualified but pending high volume verification rampup.

FIGURE 2. 70 micron in-line Fine Pitch Wire Bonding

Second, if the device is pad limited & not core limited, than the bond pad configuration can be staggered. Wire Bonds are made from both rows of staggered bond pads at different loop heights. Wire bonds from outer row of staggered bond pads are bonded to inner bond fingers at a lower loop. The inner row of the bond pads are bonded to the outer bond fingers at a higher loop. The vertical wire to wire clearance from both row of bond pads should not be less than 3 mils. Assembly sites(NSSG) is currently qualified with 64 micron staggered wire bond capability. 60 micron staggered is also qualified pending high volume verification rampup.

FIGURE 3. 60 micron Staggered Fine Pitch Wire Bonding Capability

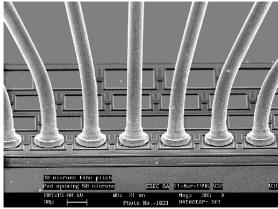

Fine Pitch wirebonding require precision ball size formation & bond placement. One of the critical design rules of fine pitch wire bonding is forming the ball bond 100% within the Bond Pad. The consistent ball size formation has been improved tremendously by the Wire Bond Equipment Suppliers by improving the Electrical Flame Off(EFO) unit & Bond Force Control. The Bond Placement accuracy has also been upgraded by means of a combination of Hardware & Software Control by the Equipment Suppliers, Especially ESEC & KNS. Ball Shear & Pull Test requirements have been maintained with all these modifications & upgrades.

www.national.com

4

MS011800-

FIGURE 4. Shows a series of in-line Ball Bond at 70 micron Pad Pitch with Ball Placement 100% within the Bond Pad Opening.

#### **MOLDING**

Mold compound protects the device mechanically and environmentally from the outside environment. Transfer molding is used to encapsulate most plastic packages.

#### **Mold Compounds**

Mold compounds are formulated from epoxy resins containing inorganic fillers, catalysts, flame retardants, stress modifiers, adhesion promoters, and other additives. Fused silica, the filler most commonly used, imparts the desired coefficient of thermal expansion, elastic modulus, and fracture toughness properties.

Most resin systems are based on an epoxy cresol novolac (ECN) chemistry though advanced resin systems have been developed to meet demanding requirements associated with moisture sensitivity and high temperature operation. Filler shape impacts the loading level of the filler.

TABLE 3. Basic Mold Compound Formulations

| Туре            | Basic<br>Formulation                                                     | Comments                                                                 |  |

|-----------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| "Standard"      | ECN/angular fused silica                                                 | Relatively<br>High Stress                                                |  |

| "Low Stress"    | ECN/angular<br>and round<br>fused silica                                 | Contains silicon rubber additive for low stress                          |  |

| Biphenyl        | Biphenyl<br>epoxy<br>resin/angular<br>and round<br>fused silica          | Low moisture absorption                                                  |  |

| Multifunctional | Multifunctional<br>epoxy resins/<br>angular and<br>round fused<br>silica | High<br>temperature<br>applications<br>and warp<br>sensitive<br>packages |  |

#### Transfer Molding

Transfer molding is used to encapsulate leadframe based packages and some PBGA packages. This process involves

the liquidification and transfer of pelletized mold compound in a mold press. The liquidification results in a low viscosity material that readily flows into the mold cavity and completely encapsulates the device. Shortly after the transfer process into the mold cavity, the cure reaction begins and the viscosity of the mold compound increases until the resin system is hardened. A further cure cycle takes place outside the mold in an oven to ensure the mold compound is completely cured.

Process parameters are optimized to ensure the complete fill of the mold cavity and the elimination of voids in the mold compound. Also critical to the mold process is the design of the mold tool. Runners and gates are designed so the flow of mold compound into the mold cavity is complete without the formation of voids.

Depending on the wire pitch, the mold process is further optimized to prevent wire sweep that can result in electrical shorts inside the package. Process parameters that are controlled are the transfer rate, temperature, and pressure. The final cure cycle (temperature and time) determines the final properties and, thus, the reliability of the molded package.

MS011800-

FIGURE 5. Wire Sweep In A Fine Pitch Device Resulting in Shorts

#### **DEJUNK AND DEFLASH**

The dejunk process removes excess mold compound that may be accumulated on the leadframe from molding.

Media deflash bombards the package surface with small glass particles to prepare the leadframe for plating and the mold compound for marking.

### **LEAD FINISH**

The lead finish allows for the mechanical and electrical connection between the package and the printed circuit board. Leadframe based packages most commonly use tin-lead solder plating as the final lead finish. Nickel-palladium finishes are also available.

During the plating process the leadframe strip goes through a series of steps involving pretreatment, rinse, plating, drying, and inspection. Process baths are carefully monitored for chemical composition and plating parameters such as voltage, current density, temperature, and time. Appearance, solderability, composition, and thickness are key quality items for plating.

#### TRIM AND FORM

Trim and form is the process where the individual leads of the leadframe are separated from the leadframe strip. First, the process involves the removal of the dambar that electrically isolates the leads. Second, the leads are placed in tool-

5 www.national.com

ing, cut, and formed mechanically to the specified shaped. J-bend and gull-wing shapes are used for surface mounted plastic packages. Individual units are singulated from the leadframe strip, inspected for lead coplanarity, and placed in trays or tubes.

The lead forming process is critical to achieve the coplanar leads required for surface mount processes. Tool cleaning during maintenance is crucial to ensure the quality of the process.

#### **MARKING**

Marking is used to place corporate and product identification on a packaged device. Marking allows for product differentiation. Either ink or laser methods are used to mark packages. Laser marking is preferred in many applications because of its higher throughput and better resolution.

# Plastic Ball Grid Array (PBGA)

#### DIE ATTACH

The die attach process and equipment for PBGA are similar to the leadframe based packaging. Die attach material formulations are optimized to provide strong adhesion to the plastic substrate.

TABLE 4. Die Attach Materials for PBGA

| Package<br>Type | Material | Requirements |

|-----------------|----------|--------------|

| Plastic (BGA)   | Ероху    | Low Moisture |

|                 | Modified | Absorption   |

|                 | Epoxies  | Thermal      |

|                 |          | Dissipation  |

#### **WIRE BOND**

Bonding to a plastic substrate typically involves lower temperatures than bonding to a leadframe alloy. Temperatures are reduced (to 160° C) to maintain sufficient strength in the substrate material so that the ultrasonic energy is efficiently utilized.

#### MOLDING/ENCAPSULATION

Transfer molding is used to encapsulate some PBGA packages. Emerging for other PBGA applications is the use of liquid encapsulants. Liquid encapsulants are used where wire pitch is tight and for filling cavity packages.

Liquid encapsulants are also formulated using epoxy resins, fused silica filler, and other additives. Being in liquid form, these encapsulant materials have low viscosity and can be filled with high levels of silica to impart desired mechanical properties.

Liquid encapsulants are dispensed from a syringe. Depending on the PBGA configuration, a dam resin may be deposited as the first step. The dam resin defines the encapsulation area around the device. The cavity or defined area is filled with encapsulant that covers the device and the wires. Finally a cure process is used. The lower viscosity of liquid encapsulants greatly diminishes the probability of wire sweep.

#### **SOLDER BALL ATTACH**

Unlike leadframe packages, PBGA's use solder balls as the interconnect path from the package to the printed circuit board. Instead of lead forming processes, solder balls are attached to the substrate. Solder balls are attached by applying a flux, placing the balls on the pads, and reflowing the PBGA. The reflow process forms a metallurgical joint be-

tween the solder ball and the substrate ball pad. Alignment is a key parameter during ball placement to avoid missing balls or solder bridging.

#### **MARKING**

Marking of PBGAs is the same as for the plastic leadframe packages.

#### **SINGULATION**

Individual PBGA units are cut from the substrate strip and placed in trays for subsequent handling.

#### INSPECTION

Assembled PBGAs are inspected to measure the coplanarity of the solder balls.

# **Hermetic Packaging**

National Semiconductor offers a wide variety of ceramic and metal can packages for through-hole and surface mount applications. These ceramic and metal can packages are offered as solutions for high reliability, high performance applications and are extensively used in military/aerospace and commercial applications. By design, a hermetic seal prevents gases and liquids from entering the package cavity where the die is mounted. Because of the package materials, hermetic packages are able to withstand higher temperatures than equivalent plastic packages.

#### DIE ATTACH

Hermetic packaging uses a Gold-Silicon eutectic or Silver filled glass to attach the die to the substrate. These materials are processed at high temperatures and have good thermal dissipation properties. The Gold-Silicon eutectic requires a wafer backmetal to achieve a high reliability die attach. The die is placed onto a gold preform of the die attach material and is heated in a controlled atmosphere. At the elevated process temperatures silicon from the die diffuses into the gold preform forming a liquid material. The liquid material readily wets the wafer backside and the substrate metallization to form the gold-silicon eutectic die attach.

TABLE 5. Die Attach Materials for Hermetic Packaging

| Package<br>Type | Material             | Requirements |  |

|-----------------|----------------------|--------------|--|

| Ceramic         | Silver-Filled        | High Process |  |

| (CERDIP)        | Glass                | Temperature  |  |

| CERAMIC         | Gold-Silicon         | High Process |  |

| (PGA, Side      | Eutectic             | Temperature  |  |

| -Braze)         | Silver-filledCyanate |              |  |

|                 | Ester                |              |  |

#### WIRE BOND

Typically Ultrasonic Al wdge Bonding is widely used in a ceramic package. The Au Ball Bond can also be used.

#### HERMETIC PACKAGE CONSTRUCTION

The construction of hermetic packages is divided into three main categories:

- 1. Multilayer ceramic packages

- 2. Pressed ceramic packages

- 3. Metal Can packages

## **Multilayer Ceramic Packages**

For multilayer packages, ceramic tape layers are metallized, laminated and fired to create the package body. The metallized areas are then brazed to the package body. The metallized areas of the package are then electroplated (usually

nickel followed by gold). After assembly, the hermetic seal is achieved by soldering a metal lid onto the metallized and plated seal ring. These packages therefore are often referred to as solder seal packages.

The multilayer construction allows the package designer to incorporate electrical enhancements within the package body. For example, power and ground planes to reduce inductance, shield planes to reduce cross talk, and controlled characteristic impedance of signal lines have been incorporated into multilayer ceramic packages.

#### **Pressed Ceramic Packages**

Pressed ceramic packages are usually a three part construction:

- 1. Base

- 2. Lid

- 3. Leadframe

The base and lid are manufactured in the same manner by pressing ceramic powder into the desired shape, and then firing. Glass is then screened onto the fired base and lid. The glass paste is then fired. During package assembly, a separate leadframe is embedded into the base glass. The hermetic seal is formed by melting the lid glass over the base and leadframe combination. This seal method is referred to as a frit seal and therefore this package is often called a glass frit seal package.

The pressed ceramic packages are typically lower in cost than the multilayer packages. However, the simple construction does not allow for many electrical enhancements.

#### **Metal Can**

Metal can packages consist of a metal base with leads exited through a glass seal. This glass seal can be a compression seal or a matched seal. After device assembly in the package, a metal lid (or can) is resistance welded to the metal base forming the hermetic seal. The metal can packages are usually low lead count, less than 24 leads, and low in cost. Certain outlines, such as the TO-3, have very low thermal resistance. These packages are used in many linear and hybrid applications.

#### **LEAKAGE TEST**

This Test is specified by MIL-STD-883, method 1014. It is designed to determine the seal integrity of hermetically packaged devices. Any defect in the package construction & lid seal is revealed by applying a pressure differential between the cavity & the exterior of the package & detecting a resultant leak.

#### **MATERIAL PROPERTIES**

Properties of some materials used in electronic packaging are listed in *Table 6*. Differences in the Coefficient of Thermal Expansion (CTE) between materials contributes to stresses along interfaces and between joints as the electronic package is cycled between temperature extremes.

**TABLE 6. Material Properties**

| Material            | CTE (ppm/°C) | Density<br>(g/cm³) | Thermal<br>Conductivity<br>(W/m K) | Electrical<br>Resistivity<br>(μΩ-cm) | Tensile<br>Strength<br>(GPa) | Melting Point<br>(°C) |

|---------------------|--------------|--------------------|------------------------------------|--------------------------------------|------------------------------|-----------------------|

| Silicon             | 2.8          | 2.4                | 150                                | -                                    | -                            | 1430                  |

| Mold<br>Compound    | 18-65        | 1.9                | 0.67                               | -                                    | -                            | 165 (Tg)              |

| Copper              | 16.5         | 8.96               | 395                                | 1.67                                 | 0.25-0.45                    | 1083                  |

| Alloy 42            | 4.3          | -                  | 15.9                               | -                                    | 0.64                         | 1425                  |

| Gold                | -            | 19.3               | 293                                | 2.2                                  | -                            | 1064                  |

| Aluminum            | 23.8         | 2.80               | 235                                | 2.7                                  | 83                           | 660                   |

| Eutectic<br>Solder  | 23.0         | 8.4                | 50                                 | -                                    | -                            | 183                   |

| Alumina             | 6.9          | 3.6                | 22                                 | -                                    | -                            | 2050                  |

| Aluminum<br>Nitride | 4.6          | 3.3                | 170                                | -                                    | -                            | 2000                  |

7 www.national.com

## **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

**National Semiconductor**

Europe

Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Francais Tel: +49 (0) 1 80-532 93 58

Français Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: sea.support@nsc.com

or National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.