# **Digital Logic Basics**

Chapter 2 S. Dandamudi

# Outline

- Basic concepts

- \* Simple gates

- \* Completeness

- Logic functions

- \* Expressing logic functions

- \* Equivalence

- Boolean algebra

- \* Boolean identities

- \* Logical equivalence

- Logic Circuit Design Process

- Deriving logical expressions

- Sum-of-products form

- \* Product-of-sums form

- Simplifying logical expressions

- \* Algebraic manipulation

- \* Karnaugh map method

- \* Quine-McCluskey method

- Generalized gates

- Multiple outputs

- Implementation using other gates (NAND and XOR)

© S. Dandamudi

# Introduction

- Hardware consists of a few simple building blocks

- \* These are called *logic gates*

- » AND, OR, NOT, ...

- » NAND, NOR, XOR, ...

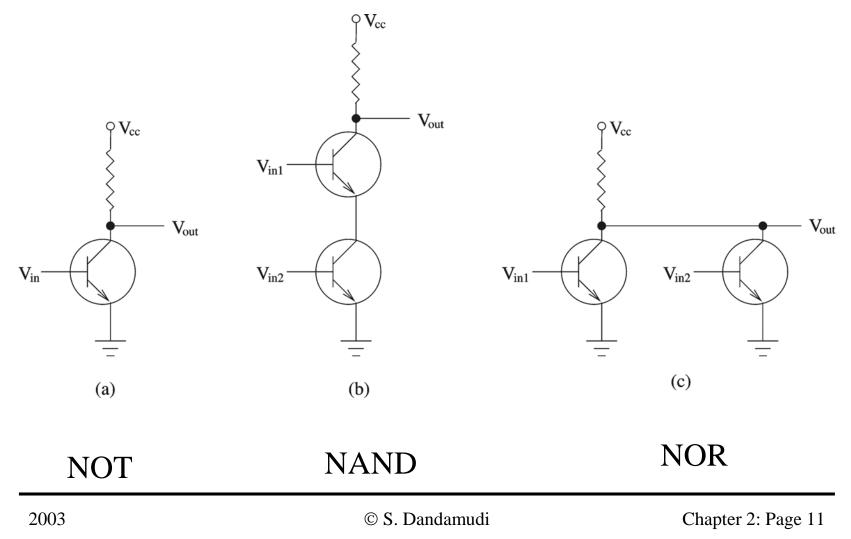

- Logic gates are built using transistors

- » NOT gate can be implemented by a single transistor

- » AND gate requires 3 transistors

- Transistors are the fundamental devices

- » Pentium consists of 3 million transistors

- » Compaq Alpha consists of 9 million transistors

- » Now we can build chips with more than 100 million transistors

## **Basic Concepts**

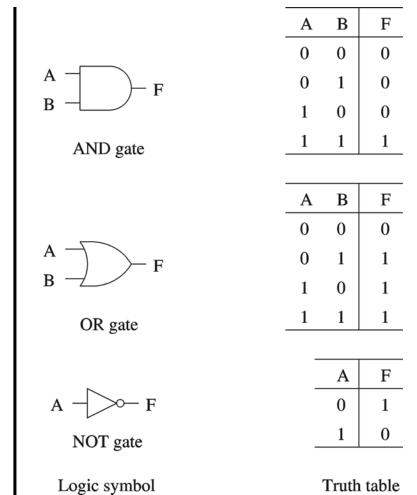

- Simple gates

- \* AND

- \* OR

- \* NOT

- Functionality can be expressed by a truth table

- \* A truth table lists output for each possible input combination

- Other methods

- \* Logic expressions

- \* Logic diagrams

© S. Dandamudi

Chapter 2: Page 4

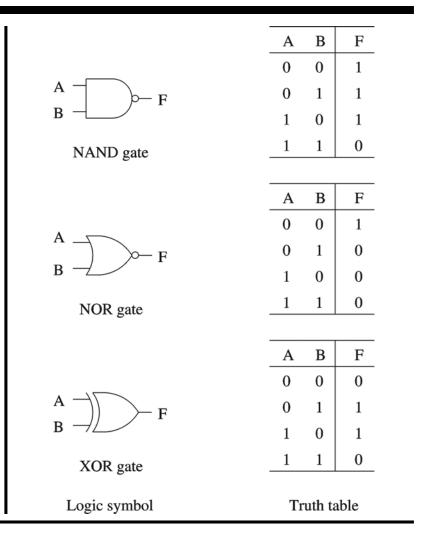

- Additional useful gates

- \* NAND

- \* NOR

- \* XOR

- NAND = AND + NOT

- NOR = OR + NOT

- XOR implements exclusive-OR function

- NAND and NOR gates require only 2 transistors

- \* AND and OR need 3 transistors!

© S. Dandamudi

Chapter 2: Page 5

- Number of functions

- \* With *N* logical variables, we can define  $2^{2^N}$  functions

- \* Some of them are useful

- » AND, NAND, NOR, XOR, ...

- \* Some are not useful:

- » Output is always 1

- » Output is always 0

- \* "Number of functions" definition is useful in proving completeness property

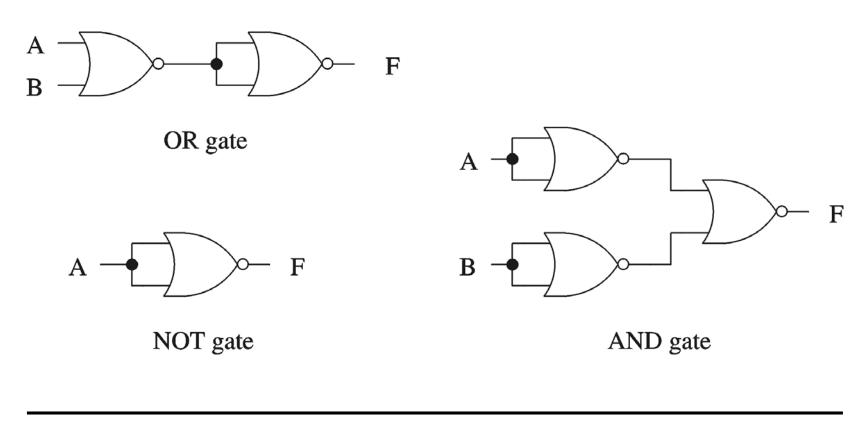

- Complete sets

- \* A set of gates is complete

- » if we can implement any logical function using only the type of gates in the set

- You can uses as many gates as you want

- \* Some example complete sets

- » {AND, NOT}

- » {OR, NOT}

- {NAND}

- » {NOR}

- \* Minimal complete set

– A complete set with no redundant elements.

• Proving NAND gate is universal

© S. Dandamudi

• Proving NOR gate is universal

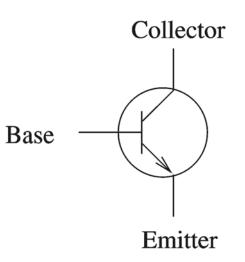

# Logic Chips

- Basic building block:

- » Transistor

- Three connection points

- \* Base

- \* Emitter

- \* Collector

- Transistor can operate

- \* Linear mode

- » Used in amplifiers

- \* Switching mode

- » Used to implement digital circuits

© S. Dandamudi

#### Logic Chips (cont'd)

# Logic Chips (cont'd)

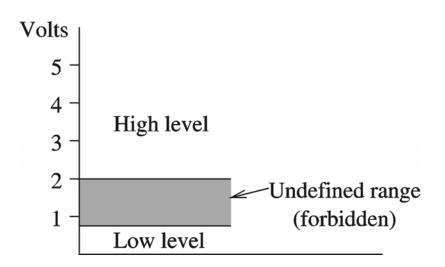

- Low voltage level: < 0.4V

- High voltage level: > 2.4V

- Positive logic:

- \* Low voltage represents 0

- \* High voltage represents 1

- Negative logic:

- \* High voltage represents 0

- \* Low voltage represents 1

- Propagation delay

- \* Delay from input to output

- \* Typical value: 5-10 ns

Logic Chips (cont'd)

© S. Dandamudi

To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

# Logic Chips (cont'd)

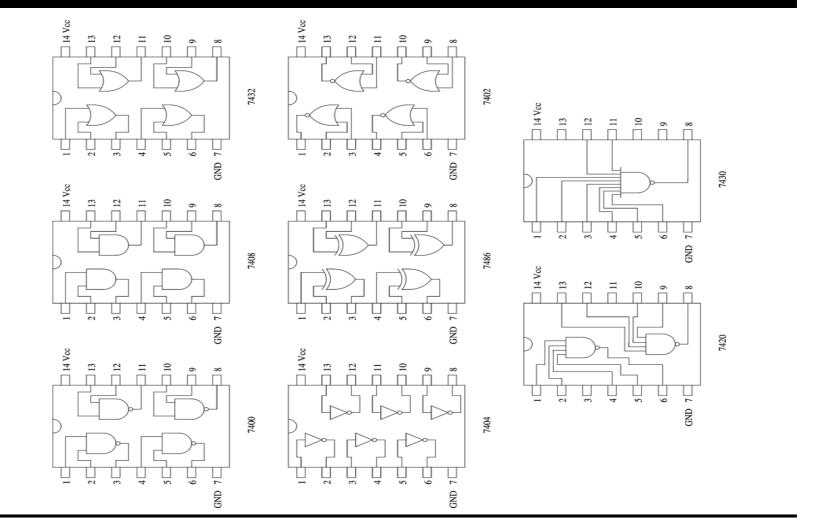

- Integration levels

- \* SSI (small scale integration)

- » Introduced in late 1960s

- » 1-10 gates (previous examples)

- \* MSI (medium scale integration)

- » Introduced in late 1960s

- » 10-100 gates

- \* LSI (large scale integration)

- » Introduced in early 1970s

- » 100-10,000 gates

- \* VLSI (very large scale integration)

- » Introduced in late 1970s

- » More than 10,000 gates

2003

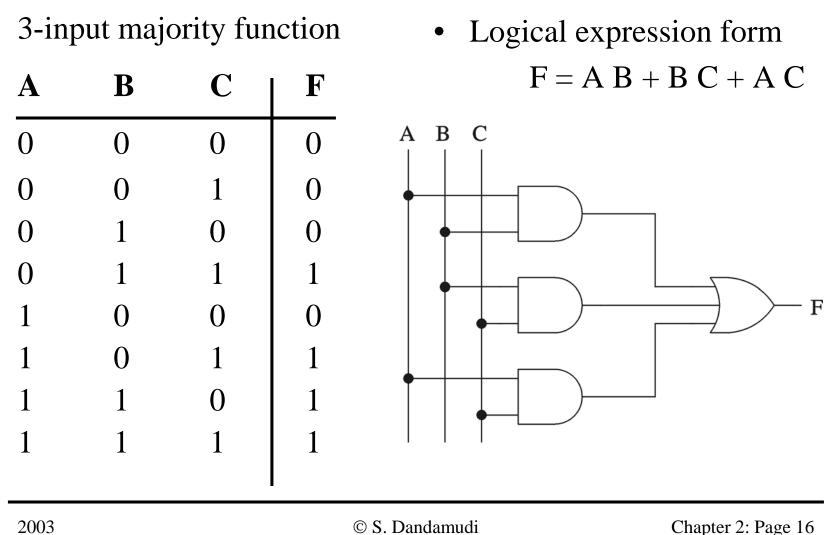

# Logic Functions

- Logical functions can be expressed in several ways:

- \* Truth table

- \* Logical expressions

- \* Graphical form

- Example:

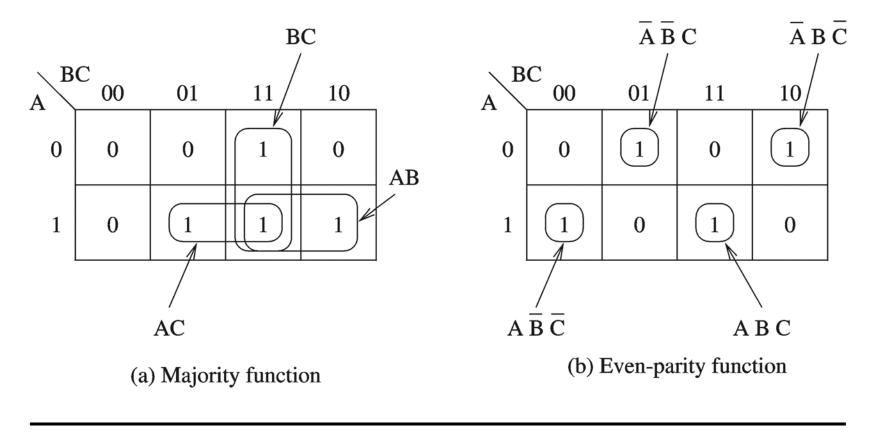

- \* Majority function

- » Output is one whenever majority of inputs is 1

- » We use 3-input majority function

Chapter 2: Page 15

© S. Dandamudi

#### Logic Functions (cont'd)

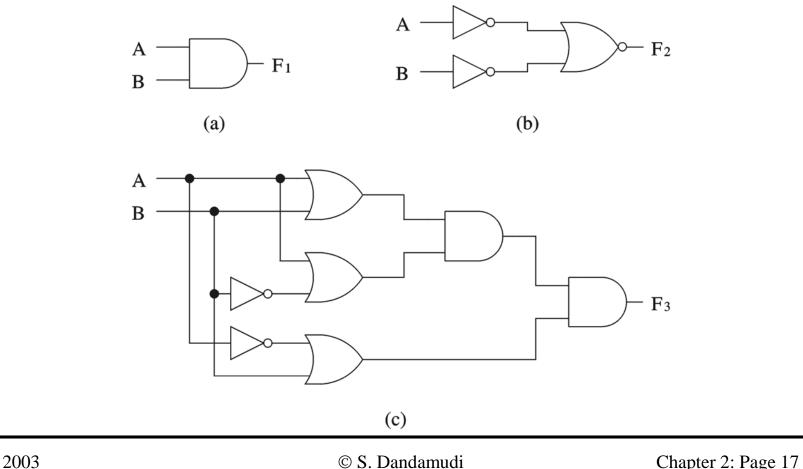

### Logical Equivalence

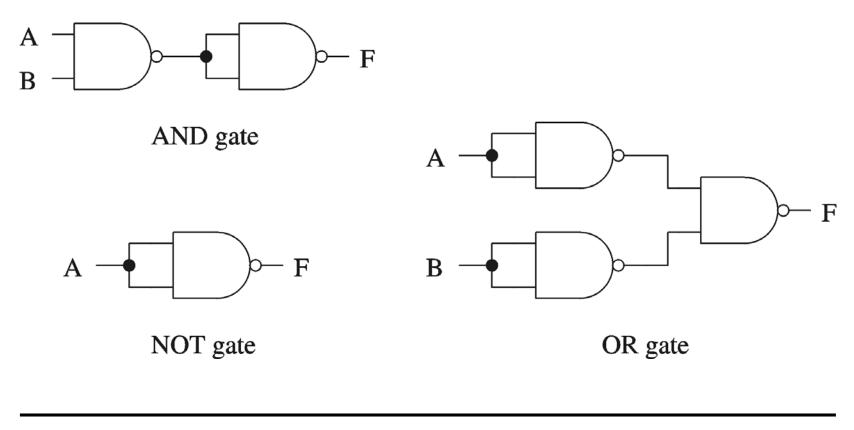

All three circuits implement F = A B function •

© S. Dandamudi

Chapter 2: Page 17

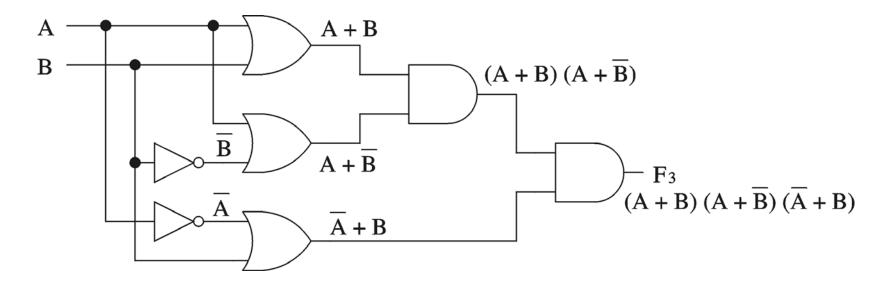

# Logical Equivalence (cont'd)

- Proving logical equivalence of two circuits

- \* Derive the logical expression for the output of each circuit

- \* Show that these two expressions are equivalent

- » Two ways:

- You can use the truth table method

- →For every combination of inputs, if both expressions yield the same output, they are equivalent

- →Good for logical expressions with small number of variables

- You can also use algebraic manipulation

→Need Boolean identities

© S. Dandamudi

# Logical Equivalence (cont'd)

- Derivation of logical expression from a circuit

- \* Trace from the input to output

- » Write down intermediate logical expressions along the path

To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

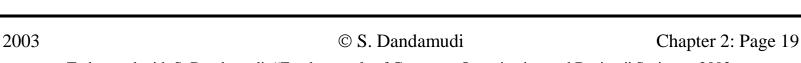

# Logical Equivalence (cont'd)

• Proving logical equivalence: Truth table method

| Α | B | <b>F1 = A B</b> | $\mathbf{F3} = (\mathbf{A} + \mathbf{B}) \ (\mathbf{\overline{A}} + \mathbf{B}) \ (\mathbf{A} + \mathbf{\overline{B}})$ |

|---|---|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 0               | 0                                                                                                                       |

| 0 | 1 | 0               | 0                                                                                                                       |

| 1 | 0 | 0               | 0                                                                                                                       |

| 1 | 1 | 1               | 1                                                                                                                       |

|   |   |                 |                                                                                                                         |

© S. Dandamudi

#### Boolean Algebra

| Boolean identities |                                                                                            |                                                     |  |  |

|--------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Name               | <b>AND</b> version                                                                         | <b>OR version</b>                                   |  |  |

| Identity           | $\mathbf{x} \cdot 1 = \mathbf{x}$                                                          | $\mathbf{x} + 0 = \mathbf{x}$                       |  |  |

| Complement         | $\mathbf{x} \cdot \overline{\mathbf{x}} = 0$                                               | $x + \overline{x} = 1$                              |  |  |

| Commutative        | $\mathbf{x} \cdot \mathbf{y} = \mathbf{y} \cdot \mathbf{x}$                                | $\mathbf{x} + \mathbf{y} = \mathbf{y} + \mathbf{x}$ |  |  |

| Distribution       | $\mathbf{x} \cdot (\mathbf{y} + \mathbf{z}) = \mathbf{x}\mathbf{y} + \mathbf{x}\mathbf{z}$ | $x + (y \cdot z) =$                                 |  |  |

|                    |                                                                                            | (x+y)(x+z)                                          |  |  |

| Idempotent         | $\mathbf{x} \cdot \mathbf{x} = \mathbf{x}$                                                 | $\mathbf{x} + \mathbf{x} = \mathbf{x}$              |  |  |

| Null               | $\mathbf{x} \cdot 0 = 0$                                                                   | x + 1 = 1                                           |  |  |

© S. Dandamudi

## Boolean Algebra (cont'd)

• Boolean identities (cont'd)

| Name        | AND version                                                                                       | <b>OR version</b>                                                                        |

|-------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Involution  | $\overline{\overline{\mathbf{x}}} = \mathbf{x}$                                                   |                                                                                          |

| Absorption  | $x \cdot (x+y) = x$                                                                               | $\mathbf{x} + (\mathbf{x} \cdot \mathbf{y}) = \mathbf{x}$                                |

| Associative | $\mathbf{x} \cdot (\mathbf{y} \cdot \mathbf{z}) = (\mathbf{x} \cdot \mathbf{y}) \cdot \mathbf{z}$ | x + (y + z) =                                                                            |

|             |                                                                                                   | (x + y) + z                                                                              |

| de Morgan   | $\overline{\mathbf{x} \cdot \mathbf{y}} = \overline{\mathbf{x}} + \overline{\mathbf{y}}$          | $\overline{\mathbf{x} + \mathbf{y}} = \overline{\mathbf{x}} \cdot \overline{\mathbf{y}}$ |

| 2003 | © S. Dandamudi                                                                                    | Chapter 2: Page 22 |  |

|------|---------------------------------------------------------------------------------------------------|--------------------|--|

|      | To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003. |                    |  |

# Boolean Algebra (cont'd)

- Proving logical equivalence: Boolean algebra method

- \* To prove that two logical functions F1 and F2 are equivalent

- » Start with one function and apply Boolean laws to derive the other function

- » Needs intuition as to which laws should be applied and when

- Practice helps

- Sometimes it may be convenient to reduce both functions to the same expression

- \* Example: F1= A B and F3 are equivalent

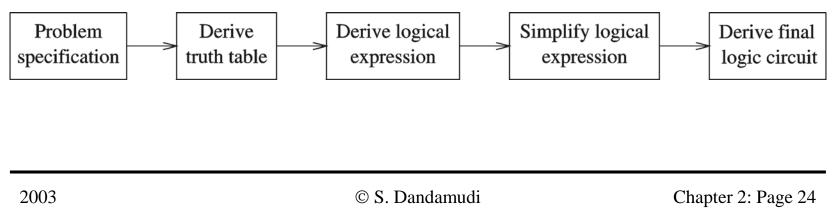

# Logic Circuit Design Process

- A simple logic design process involves

- » Problem specification

- » Truth table derivation

- » Derivation of logical expression

- » Simplification of logical expression

- » Implementation

# **Deriving Logical Expressions**

- Derivation of logical expressions from truth tables

\* sum-of-products (SOP) form

- \* product-of-sums (POS) form

- SOP form

- \* Write an AND term for each input combination that produces a 1 output

- » Write the variable if its value is 1; complement otherwise

- \* OR the AND terms to get the final expression

- POS form

- \* Dual of the SOP form

# Deriving Logical Expressions (cont'd)

• 3-input majority function

| A | B | С | $\mathbf{F}$ |

|---|---|---|--------------|

| 0 | 0 | 0 | 0            |

| 0 | 0 | 1 | 0            |

| 0 | 1 | 0 | 0            |

| 0 | 1 | 1 | 1            |

| 1 | 0 | 0 | 0            |

| 1 | 0 | 1 | 1            |

| 1 | 1 | 0 | 1            |

| 1 | 1 | 1 | 1            |

|   |   |   |              |

- SOP logical expression

- Four product terms

- \* Because there are 4 rows with a 1 output

```

F = \overline{A} B C + A \overline{B} C + A \overline{B} C + A B \overline{C} + A B C

```

• Sigma notation

$\Sigma(3, 5, 6, 7)$

© S. Dandamudi

# Deriving Logical Expressions (cont'd)

• 3-input majority function

| A | B | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

- POS logical expression

- Four sum terms

- \* Because there are 4 rows with a 0 output

$$F = (A + B + C) (A + B + \overline{C})$$

$$(A + \overline{B} + C) (\overline{A} + B + C)$$

Pi notation

Π (0, 1, 2, 4)

© S. Dandamudi

### Brute Force Method of Implementation

To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

### Brute Force Method of Implementation

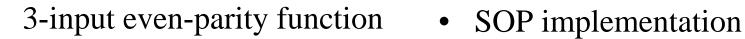

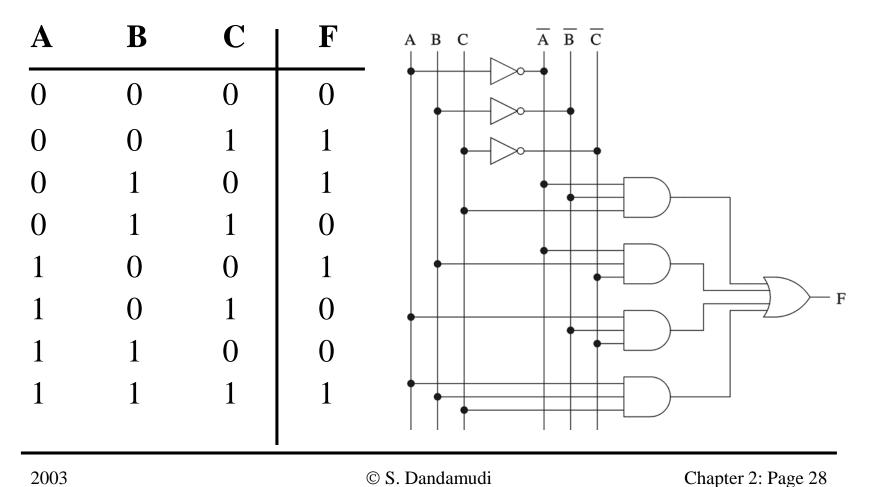

| 3-input even-parity function | • |  |

|------------------------------|---|--|

|------------------------------|---|--|

2003

• POS implementation

Chapter 2: Page 29

To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

© S. Dandamudi

# Logical Expression Simplification

- Three basic methods

- \* Algebraic manipulation

- » Use Boolean laws to simplify the expression

- Difficult to use

- Don't know if you have the simplified form

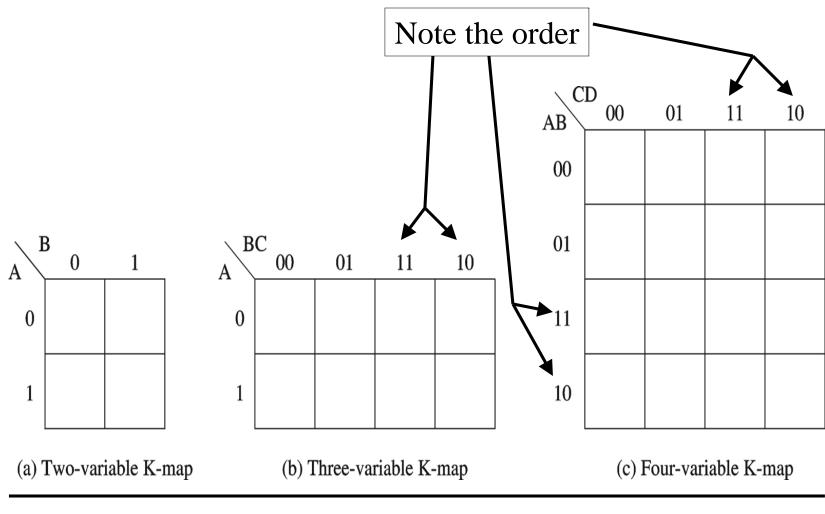

- \* Karnaugh map method

- » Graphical method

- » Easy to use

- Can be used to simplify logical expressions with a few variables

- \* Quine-McCluskey method

- » Tabular method

- » Can be automated

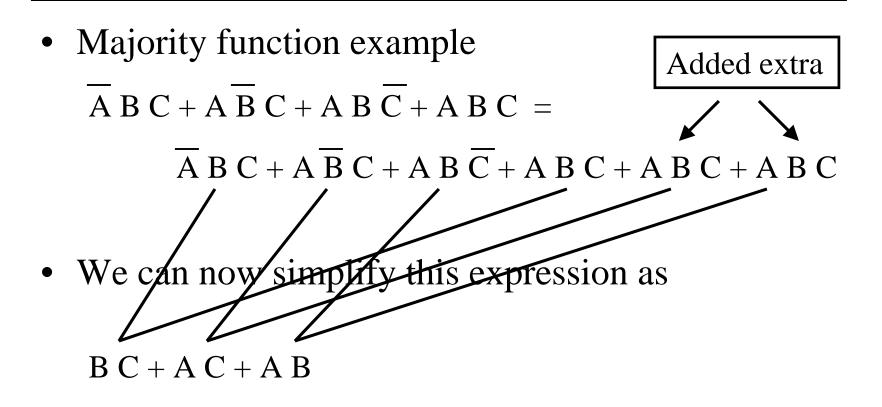

### Algebraic Manipulation

• A difficult method to use for complex expressions

#### Karnaugh Map Method

2003

$\ensuremath{\mathbb{C}}$  S. Dandamudi

Chapter 2: Page 32

# Simplification examples

To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

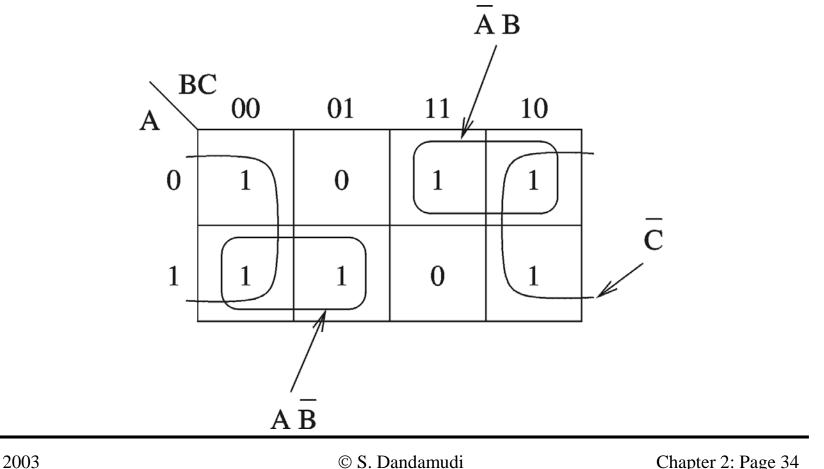

#### First and last columns/rows are adjacent

© S. Dandamudi

Chapter 2: Page 34

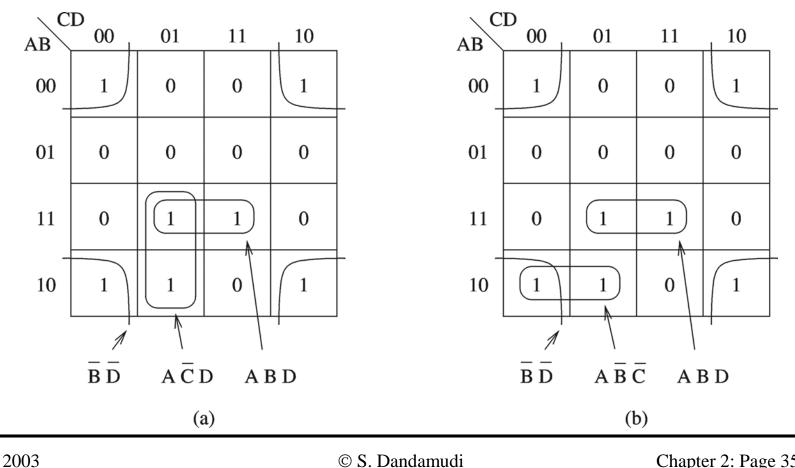

#### Minimal expression depends on groupings

© S. Dandamudi

Chapter 2: Page 35

### No redundant groupings

(a) Nonminimal simplification

(b) Minimal simplification

© S. Dandamudi

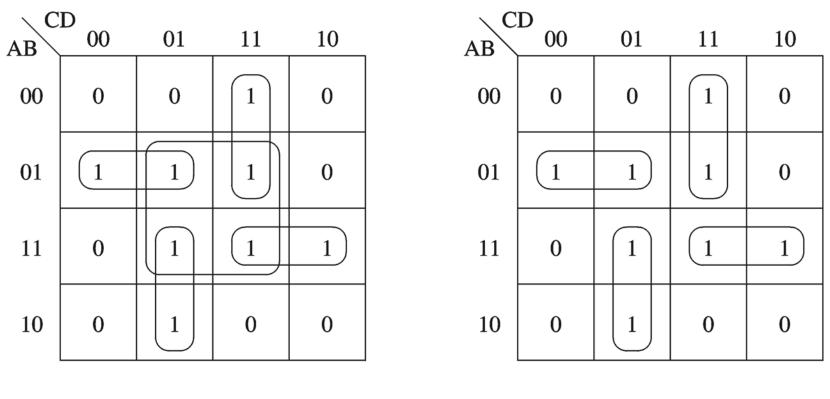

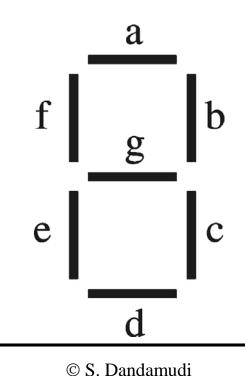

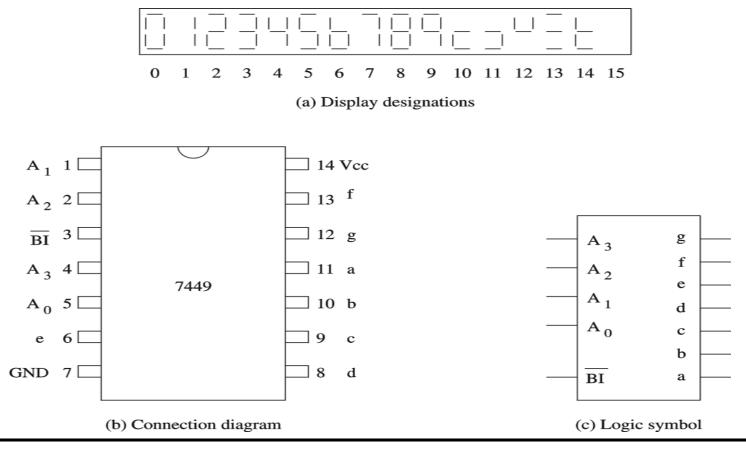

• Example

\* Seven-segment display

\* Need to select the right LEDs to display a digit

## Truth table for segment d

| No | A | B | С | D | Seg. | No | A | B | С | D | Seg. |

|----|---|---|---|---|------|----|---|---|---|---|------|

| 0  | 0 | 0 | 0 | 0 | 1    | 8  | 1 | 0 | 0 | 0 | 1    |

| 1  | 0 | 0 | 0 | 1 | 0    | 9  | 1 | 0 | 0 | 1 | 1    |

| 2  | 0 | 0 | 1 | 0 | 1    | 10 | 1 | 0 | 1 | 0 | ?    |

| 3  | 0 | 0 | 1 | 1 | 1    | 11 | 1 | 0 | 1 | 1 | ?    |

| 4  | 0 | 1 | 0 | 0 | 0    | 12 | 1 | 1 | 0 | 0 | ?    |

| 5  | 0 | 1 | 0 | 1 | 1    | 13 | 1 | 1 | 0 | 1 | ?    |

| 6  | 0 | 1 | 1 | 0 | 1    | 14 | 1 | 1 | 1 | 0 | ?    |

| 7  | 0 | 1 | 1 | 1 | 0    | 15 | 1 | 1 | 1 | 1 | ?    |

|    | I |   |   |   | I    | I  | I |   |   |   | I    |

© S. Dandamudi

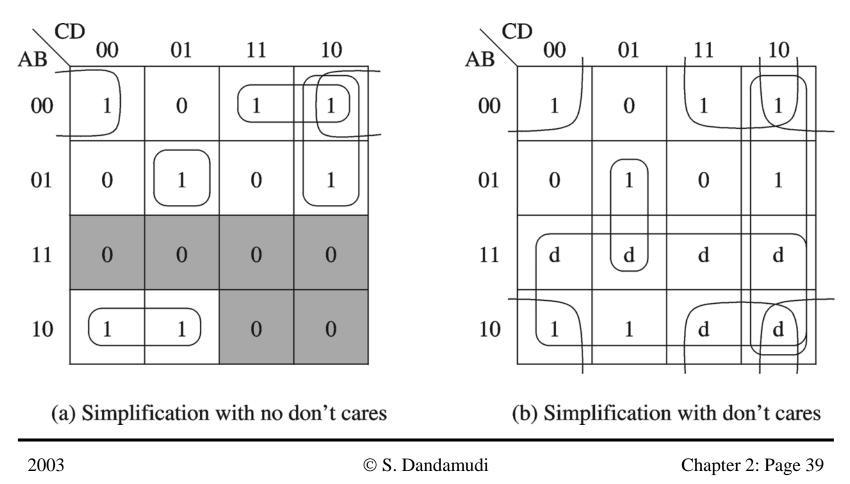

#### Don't cares simplify the expression a lot

#### Example 7-segment display driver chip

© S. Dandamudi

Chapter 2: Page 40

# Quine-McCluskey Method

- Simplification involves two steps:

- \* Obtain a simplified expression

- » Essentially uses the following rule

$X \ Y + X \overline{Y} = X$

- » This expression need not be minimal

- Next step eliminates any redundant terms

- \* Eliminate redundant terms from the simplified expression in the last step

- » This step is needed even in the Karnaugh map method

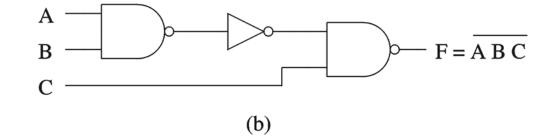

### Generalized Gates

- Multiple input gates can be built using smaller gates

- Some gates like AND are easy to build

• Other gates like NAND are more involved

© S. Dandamudi

## Generalized Gates (cont'd)

- Various ways to build higher-input gates

- \* Series

- \* Series-parallel

- Propagation delay depends on the implementation

- \* Series implementation

- » 3-gate delay

- \* Series-parallel implementation

- » 2-gate delay

© S. Dandamudi

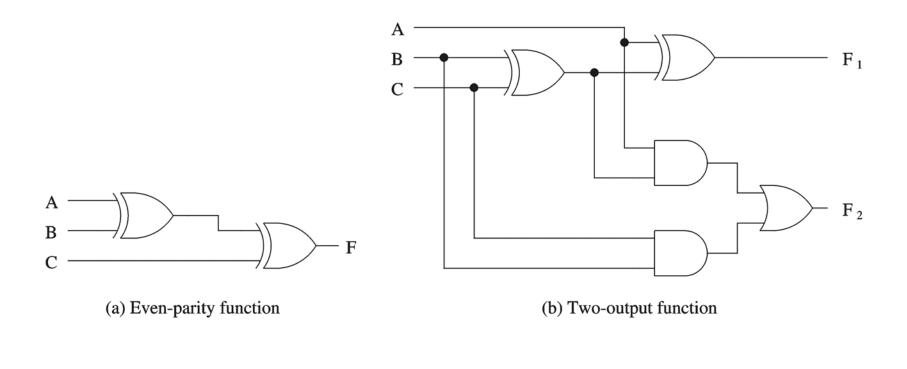

## Multiple Outputs

|   | Two- | output | function   | • F1 and F2 are |                             |  |  |

|---|------|--------|------------|-----------------|-----------------------------|--|--|

| A | B    | С      | <b>F</b> 1 | <b>F</b> 2      | familiar functions          |  |  |

| 0 | 0    | 0      | 0          | 0               | » F1 = Even-parity function |  |  |

| 0 | 0    | 1      | 1          | 0               | » F2 = Majority             |  |  |

| 0 | 1    | 0      | 1          | 0               | function                    |  |  |

| 0 | 1    | 1      | 0          | 1               | • Another                   |  |  |

| 1 | 0    | 0      | 1          | 0               | interpretation              |  |  |

| 1 | 0    | 1      | 0          | 1               | * Full adder                |  |  |

| 1 | 1    | 0      | 0          | 1               | $ F_1 = Sum $               |  |  |

| 1 | 1    | 1      | 1          | 1               | » F2 = Carry                |  |  |

|   |      |        |            |                 |                             |  |  |

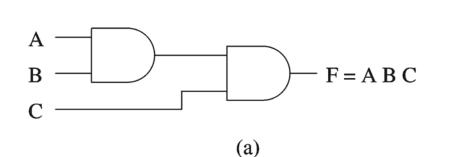

Implementation Using Other Gates

• Using NAND gates

\* Get an equivalent expression

$$A B + C D = A B + C D$$

\* Using de Morgan's law

$$A B + C D = A B \cdot C D$$

\* Can be generalized

» Majority function

#### $A B + B C + AC = A B \cdot BC \cdot AC$

© S. Dandamudi

Chapter 2: Page 45

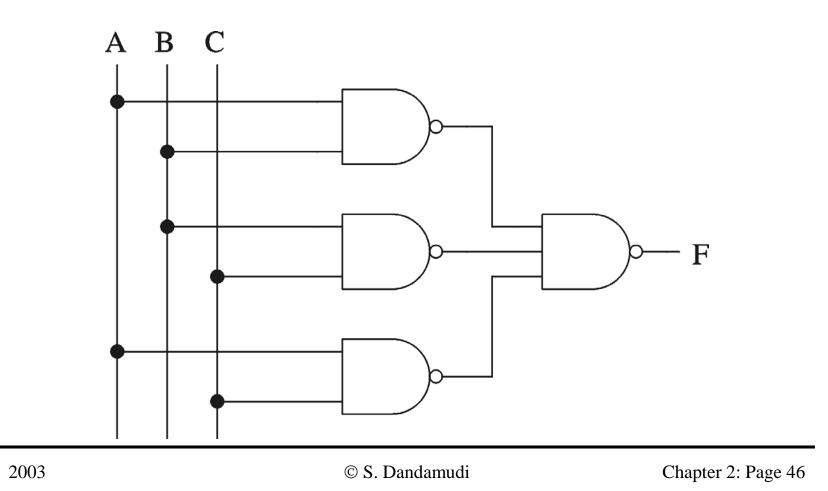

# Implementation Using Other Gates (cont'd)

• Majority function

To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

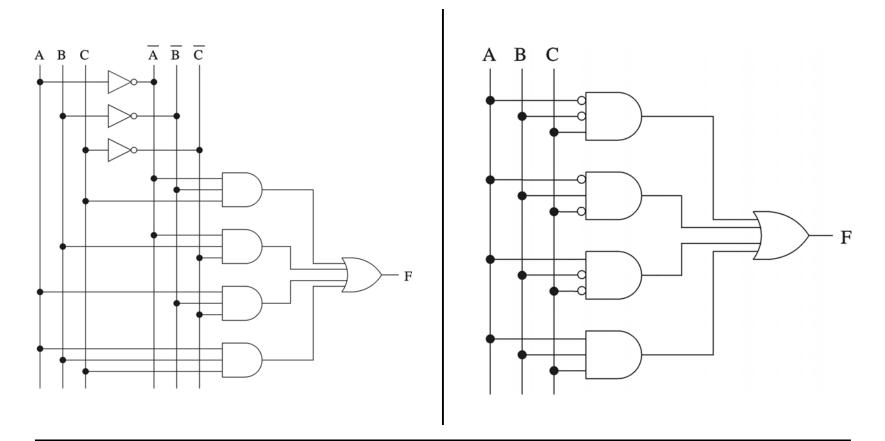

#### Implementation Using Other Gates (cont'd)

**Bubble Notation**

2003 © S. Dandamudi Chapter 2: Page 47 To be used with S. Dandamudi, "Fundamentals of Computer Organization and Design," Springer, 2003.

# Implementation Using Other Gates (cont'd)

- Using XOR gates

- \* More complicated

2003

© S. Dandamudi

#### Summary

- Logic gates

- » AND, OR, NOT

- » NAND, NOR, XOR

- Logical functions can be represented using

- » Truth table

- » Logical expressions

- » Graphical form

- Logical expressions

- \* Sum-of-products

- \* Product-of-sums

# Summary (cont'd)

- Simplifying logical expressions

- \* Boolean algebra

- \* Karnaugh map

- \* Quine-McCluskey

- Implementations

- \* Using AND, OR, NOT

- » Straightforward

- \* Using NAND

- \* Using XOR

Last slide