#### EECS150 - Digital Design

Lecture 18 - Counters

October 24, 2002 John Wawrzynek

Fall 2002 EECS150 - Lec18-counters

### What are they used?

Page 1

- · Examples from this semester:

- Clock divider circuits

- Network packet parser/filter control.

- Bit-serial multiplier control circuitry (from HW)

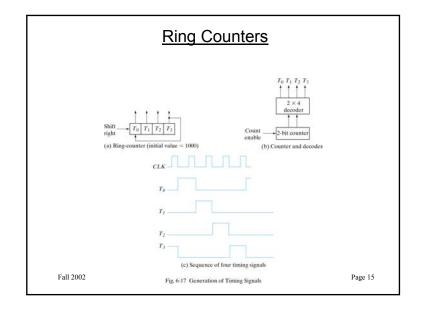

- In general: counters simplify controller design by

- providing a specific number of cycles of action,

- sometimes used in with a decoder to generate a sequence of control signals.

Fall 2002 EECS150 - Lec18-counters Page 3

#### Counters

- Special sequential circuits (FSMs) that sequence though a set outputs.

- · Examples:

- binary counter: 000, 001, 010, 011, 100, 101, 110, 111, 000, 001, ...

- gray code counter:

000, 010, 110, 100, 101, 111, 011, 001, 000, 010, 110, ...

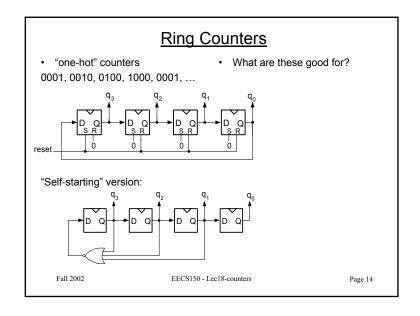

- $-\,$  one-hot counter: 0001, 0010, 0100, 1000, 0001, 0010,  $\dots$

- BCD counter: 0000, 0001, 0010, ..., 1001, 0000, 0001

- pseudo-random sequence generators: 10, 01, 00, 11, 10, 01, 00, ...

- Moore machines with "ring" structure to STD:

Fall 2002 EECS150 - Lec18-counters Page 2

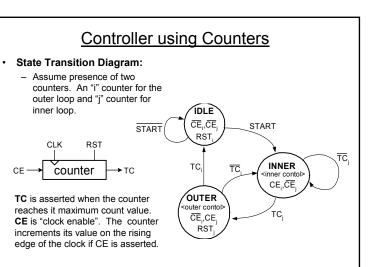

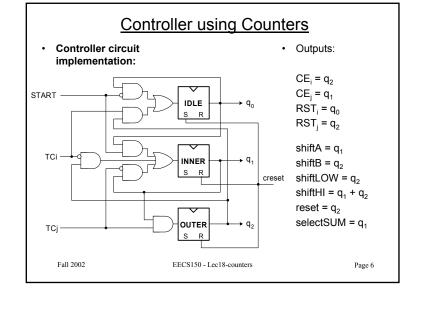

#### Controller using Counters

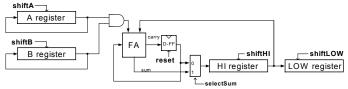

· Bit-serial multiplier:

· Control Algorithm:

Fall 2002

```

repeat n cycles { // outer (i) loop

repeat n cycles { // inner (j) loop

shiftA, selectSum, shiftHI

}

shiftB, shiftHI, shiftLOW, reset

}

Note: The occurrence of a control signal x means x=1. The absence of x means x=0.

```

EECS150 - Lec18-counters

Page 4

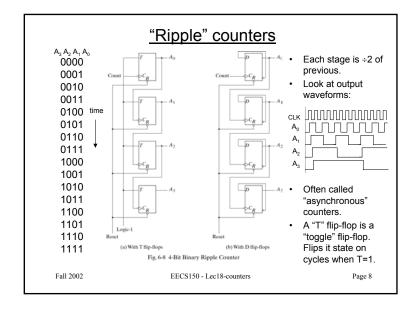

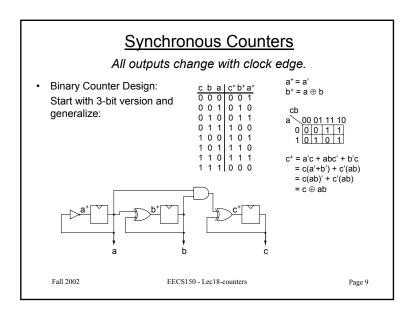

# How do we design counters?

EECS150 - Lec18-counters

Page 5

For binary counters (most common case) incrementer circuit would work:

1 + register

- In Verilog, a counter is specified as: x = x+1;

- This does not imply an adder

Fall 2002

- An incrementer is simpler than an adder

- And a counter is simpler yet.

- In general, the best way to understand counter design is to think of them as FSMs, and follow general procedure. But before that ...

Fall 2002 EECS150 - Lec18-counters Page 7

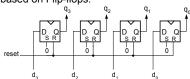

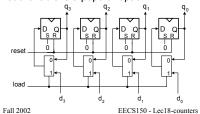

### Register Summary

All registers (this semester) based on Flip-flops:

· Load-enable is a popular option:

Xilinx flip-flops employ a clock enable (CE) for same purpose.

Page 17

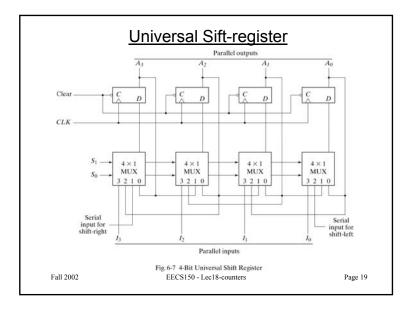

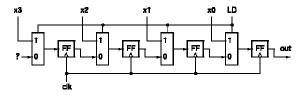

## **Shift-registers**

· Parallel load shift register:

- "Parallel-to-serial converter"

- Also, works as "Serial-to-parallel converter", if q values are connected out.

- Also get used as controllers (ala "ring counters")

Fall 2002 EECS150 - Lec18-counters Page 18