# ATM SWITCHING

## **OPERATIONS**

#### Abstract:

The purpose of this document is to provide an overview of the ATM technology and to describe its switching functions, architecture, and techniques.

| DATE:<br>NAME:<br>STUDENT ID:<br>SECTION:<br>COURSE: | May 1 <sup>st</sup> , 1998<br>Thanh Pham<br>xxx-xx-xxxx<br>799<br>EE6304 / Spring 1998 |

|------------------------------------------------------|----------------------------------------------------------------------------------------|

| ADDRESS:                                             | street address<br>Dallas, TX 75xxx                                                     |

| PHONE:                                               | 972-xxx-xxxx (home)<br>972-yyy-yyyy (work)                                             |

## Table of Contents

- I. Introduction

- II. ATM Basics

- III. ATM Adaptation Layers

- IV. ATM Switching Functions

- V. ATM Switching Architecture

- VI. ATM Switching Techniques

- VII. Conclusion

#### I. Introduction

The telecommunications industry is rapidly becoming a high bandwidth and high speed network environment due to fast growing market demands for multimedia applications. New multimedia based applications (such as data, voice, video and image) require greater bandwidth with capability of handling multiservice traffic on the same network. One technology known as asynchronous transfer mode (ATM) was developed and is continually being further enhanced to meet this demand.

ATM is a high speed, packet switching network technology capable of supporting many classes of traffic. It incorporates the advantage of fiber optic techniques to transport a wide range of traffic types such as voice, video, image and various data traffic.

ATM is a standard being developed by 2 major organizations: the ATM Forum and the ITU-T. The ATM standards define guidelines needed to support cell-based voice, data, video, and multimedia communication in a public network under Broadband ISDN. Although ATM standards are very well defined, there is one area that is not included the overall standard. It is the area of ATM switching. By default, ATM switch vendors use a wide variety of techniques to build their switches based on their own research and development efforts. Therefore, this paper will provide the reader with ATM basics overview in addition to a general description of the major components of an ATM switch and various switch design techniques being implemented by ATM switch vendors.

#### II. ATM Basics

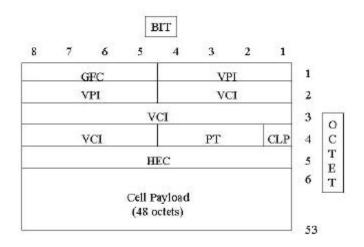

ATM is a cell based switching and multiplexing technology with high-bandwidth and low-delay characteristics designed to be a general-purpose connection-oriented transfer mode for a wide range of services. ATM segments and multiplexes user traffic into small fixed-length of 53-octets units called cells. Each 53 octets cell is further divided into 5 octets of header information and 48 octets of user information. User information is packed into each cell with a label in the header to allow the cell to be identified and switched throughout the ATM network. Figure 1 shows the ATM cell structure, at the user-network interface, as specified by the ATM standards.

Figure 1: ATM Cell Structure

The Generic Flow Control (GFC) field is 4-bit long to allow encoding of 16 states for flow control. No standardization has yet been defined for the coding values. However, the ITU-T is now considering several proposals. This 4-bit field is set to zeros when not in use.

The routing field comprises 24 bits with 8 bits assigned to the virtual path identifier (VPI) and 16 bits assigned to the virtual channel identifier (VCI). Currently, there are 2 reserved codes for signaling and broadcast virtual channel identification. Further studied is in progress to define the encoding methodology. The Payload Type (PT) field is 3-bits long and is used to indicate whether the cell contains user information or network information. It identifies the type of traffic residing in the cell. If PT field indicate user information, the payload consists of user information and service-adaptation function information. If PT field indicate network information, it contains management/control information.

The Cell Loss Priority (CLP) field is a 1-bit value that allows the user or network to optionally indicate the explicit loss priority of the cell. If CLP is set (CLP=1), it indicates that the cell is subject to discard depending on network conditions. If CLP is not set (CLP= 0), the cell has higher priority.

The Header Error Control (HEC) field is an error check field. It consists of 8 bits and is used for detecting and managing header errors.

An ATM switch performs the relaying function of each cell through the network by assigning connection identifiers such as the VPI/VCI to each link of a connection. The VPI/VCI constitutes a label used to allocate transmission resources and has local significance to the user. In other words, the VPI/VCI of an ATM cell may undergo translation as it is being transported to another interface across the network. Therefore, usable network capacity can be dynamically assigned allowing the network to take advantage of statistical fluctuations while maintaining an established grade of service.

#### III. ATM Adaptation Layers

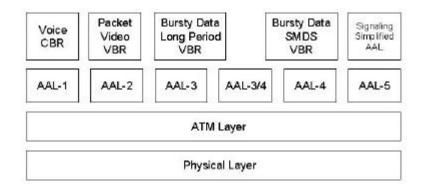

One key benefit of ATM is its capability to support many different types of user traffic including voice, data, video and image. ATM accomplishes this feature by utilizing the ATM Adaptation Layer (AAL). AAL is responsible for cell construction and reception and is used for the setup, operation, and teardown of virtual paths and circuits. Presently, there are five AALs with each AAL designed to optimally carry one type of traffic (figure 2). Each AAL is organized around a concept called service classes that

are defined to the following operations:

- Timing between sender and receiver (present or not present)

- Bit rate (variable or constant)

- Connectionless or connection-oriented sessions between sender and receiver

- Sequencing of user payload

- Flow control operations

- Accounting for user traffic

- Segmentation and reassembly (SAR) of user PDUs.

Figure 2: ATM Adaption Layer

Today, the ATM standards define four classes of traffic that are based on constant bit rate (CBR) and variable bit rate (VBR) services and is currently developing guidelines for available bit rate (ABR) service. ABR is a new class of service developed to make use of spare bandwidth that is not being used by CBR and VBR traffic. The four classes of traffic are:

- 1. Class A: CBR service with end-to-end timing, connection-oriented.

- 2. Class B: VBR service with end-to-end timing, connection-oriented.

- 3. Class C: VBR service with no timing required, connection-oriented.

- 4. Class D: VBR service with no timing required, connectionless.

#### IV. ATM Switching Functions

As described earlier in previous sections, user traffic information is routed through the network via virtual paths or channels. Therefore, one key function of an ATM switch is its ability to buffer cells and quickly relay them without cell loss. However, ATM switches not only relay cells but must also perform control and management functions in order to support both asynchronous and synchronous traffic as well as connectionless and connection-oriented traffic.

An ATM switch contains a set of input and output ports, which are utilized to interconnect to users, other switches, and other network elements. It also has interfaces to exchange control and management information with special purpose networks (i.e., network management systems).

According to ATM standards, the switching function of ATM switches are categorized into 3 planes based on the Broadband ISDN model: User plane (U-plane), Control plane (C-plane), and Management plane (M-plane).

The User plane relay user information cells from input ports to appropriate output ports by processing cell headers. It is useful to note that in the User plane, cell payloads are carried transparently through the network. Therefore, this cell relay function can be divided into 3 major blocks: the input module at the input port, the cell switch matrix that performs the routing function, and the output modules at the output ports. The Control plane deals with call establishment and release of virtual path/virtual channel connections. Information in control cells payload is not transparent to the network because it contains signaling information required for setting-up connections.

The Management plane provides management functions to ensure correct and efficient network operation. The management function can further be divided as follows:

- Fault management

- Performance management

- Configuration management

- Security management

- Accounting management

- Traffic management

#### V. ATM Switching Architecture

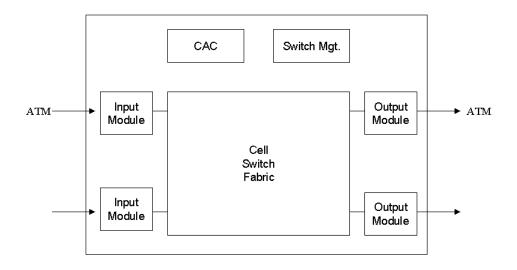

To simplify the discussion of various design concepts, a generic functional model for a switching architecture is presented in this section. The generic model consists of the following blocks: input modules, output models, cell switch fabric, connection admission control (CAC), and switch management (figure 3).

The input module performs the termination of incoming signals and the extraction of ATM cell stream. This task involves signal conversion and recovery, overhead processing, and cell delineation and rate decoupling. Furthermore, the input module performs the following function on each ATM cell:

- Error checking of the header information using HEC field

- Validation and translation of VPI/VCI values

- Determination of destination output ports

- Passing signaling cells to CAC and Operations and Management (OAM) cells to switch management

- Usage/network parameter control for each VPC/VCC

- Addition of internal tags with internal routing and performance monitoring information for use only within the switch

Figure 3: A Generic Switch Model

The output module prepares ATM cells into a format for transmission on the

physical network. It accomplishes this task by:

- Removing and processing internal tags

- Translating VPI/VCI values

- Generating HEC field

- Mixing CAC and Switch Management cells with outgoing cell streams

- Performing cell rate decoupling

- Mapping cells to physical transmission formats (i.e., such as SONET)

• Converting digital bit stream to optical signal

The cell switch fabric main task is to perform the routing of data cells and possibly signaling and management cells as well. This fabric consists of both hardware and software components. The cell switch fabric receives cells on an incoming port, reads the VPI/VCI value, and identifies an appropriate outgoing port for the next node that is to receive the traffic. Further in-depth explanation will be provided in the next section to cover the different switch fabric techniques.

The connection admission control (CAC) is a set of procedures that include actions taken by the network to grant or deny a virtual connection. In other words, CAC establishes, modifies, and terminates virtual path/virtual channel connections.

The Switch Management has the overall responsibility of providing key information for managing the switch and the network. It performs tasks that include the following:

- Configuration management of switch components

- Security control for switch database

- Usage measurements of switch resources

- Traffic management

- Administration of management information base

- Network Management

### VI. ATM Switching Techniques

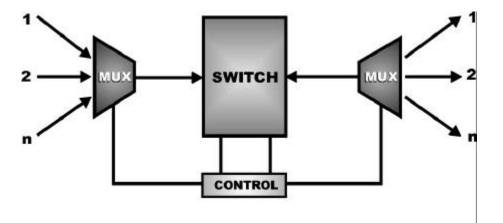

Within an ATM switch, the cell switch fabric plays a very key role. Its main responsibility is to relay ATM cells as quickly as possible. The cell switch fabric accomplishes this by performing 2 major functions:

• Concentration, expansion, multiplexing/demultiplexing of traffic

• Routing and buffering of traffic

The cell switch fabric concentrates traffic received at the input ports for better resource utilization. Lower bit rate traffic are aggregated and multiplexed onto higher bit rate for the switch to perform switching of traffic at standard interface speed from input to output ports. Let us now look at the various design techniques implemented by vendors to enable the switch to perform its main task of relaying ATM cells. Five switching alternatives will be explored in this document and they are Shared Memory Switch, Shared Bus Switch, Crossbar Switch, Multistage Switching, and Banyan/Delta Switching.

The Shared Memory Switch is a technique that uses a common memory for the storage of cells and switching fabric. Incoming cells are multiplexed onto a single line to the switch and are placed in queues. Then, based on cell headers information and internal tags, the switching function decides the order in which cells are move from the input queues to the output queues and ultimately onto the output ports (Figure 4).

Figure 4: Shared Memory Switch

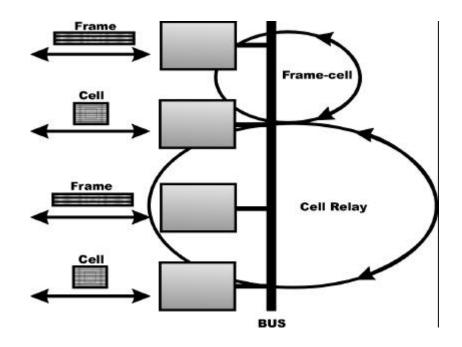

The Shared Bus Switch approach utilizes a bus or dual bus architecture to switch cell traffic. Cell traffic is carried through the bus for transmission. With this technique,

frame based traffic can also be supported since the busses operates in cell mode. Therefore, the traffic is diced into 48-octet pieces with 5-byte header attached for transmission onto the bus. It is easy to see that frame based traffic can be converted to ATM cells and vice versa with this approach (Figure 5).

Figure 5: Shared Bus Switch

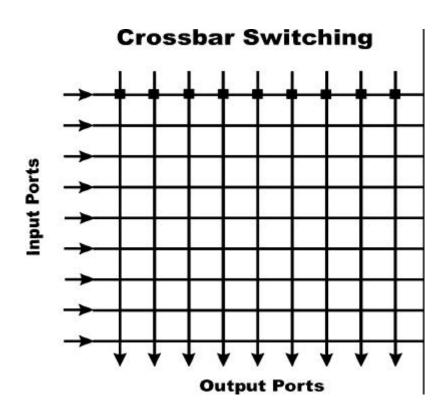

The Crossbar Switch is a simple matrix-like space division technique that physically interconnects any of the N inputs to any of the N outputs at crosspoints. Therefore, a crossbar switching fabric consists of N<sup>2</sup> crosspoints. It is easy to see that this approach will be difficult to implement for large switches (Figure 6).

Figure 6: Crossbar Switching

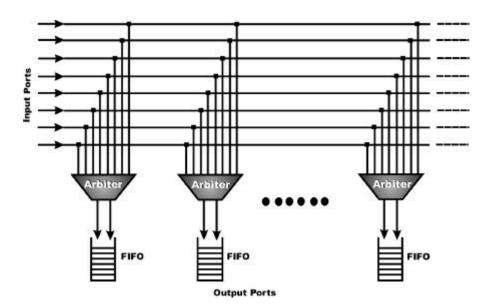

The Multistage Switching uses a similar concept to the crossbar switch technique. However, it is designed with a more tree-like structure to reduce the N squared crosspoints requirement yielding a more economical arrangement. Basically, the inputs and output lines are divided into subgroups of N inputs and N outputs (Figure 7).

Figure 7: Multistage Switching

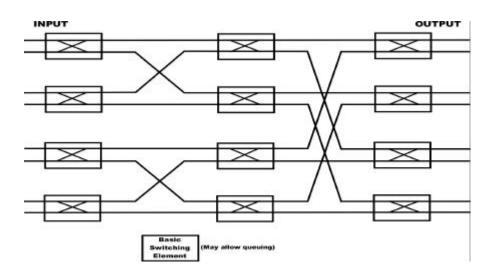

The Banyan/Delta Switching is a concept of an interconnection of stages of switching elements. This technique allows only one path of connection existing between an input to the final output port. With this approach, the routing of traffic is quite simple and straightforward. However, it has one major drawback in that cells may be blocked if more than one arrives at a switching element at the same time (Figure 8).

Figure 8: Banyan-Delta Switching

#### VII. Conclusion

The importance of ATM is much more than just a technology. It is one of the few networks that can provide real time and quality of service guarantees required for today's multimedia applications. ATM has become synonymous with communications in the information age and industry participants and users have widely accepted and promoted the use of ATM.

It is easy to see why ATM is gaining popularity. The main reason is that ATM provides adoption layers needed to support many types of data traffic. Voice, packet video, images, and bursty data are transportable on an ATM network. Therefore, this

paper has provided the reader with an introduction to ATM starting with the basics and leading to an overview of the various designs alternatives for ATM switches.

ATM will continue to play an important role in the future of telecommunications. Especially, with efforts currently in progress to further develop ATM to support service integration with existing packet-based technology such as Frame Relay, Internet, and SMDS. This will make ATM the ultimate backbone network for enterprise system in today's communication networks.

### REFERENCES

- 1. Uyless Black, "ATM: Foundation For Broadband Networks", Prentice Hall PTR, 1995.

- 2. Sonia Fahmy, "A survey of ATM Switching Techniques", <u>http://www.cis.ohio-state.edu</u>, 1995.

- 3. Daniel Minoli and Mark Raymond, "Technology Overview: Asynchronous Transfer Mode (ATM)", <u>http://www.be.datapro.com</u>, 1997.

- 4. The ATM Forum, "ATM-User-Network Interface", Prentice Hall PTR, 1993.