#### **Smart Card Tutorial - Part 1**

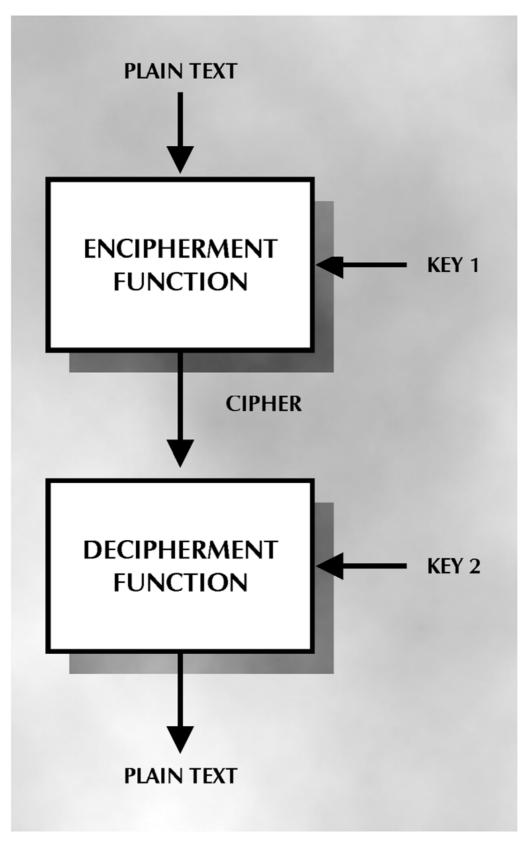

#### First Published in September 1992

#### **Introduction To Smart Cards**

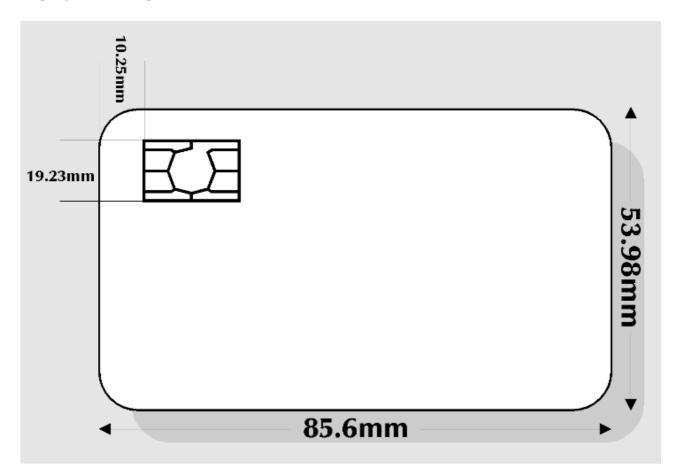

Even the name Smart Card captures the imagination, however such a term is ambiguous and is used in many different ways. ISO uses the term, Integrated Circuit Card (ICC) to encompass all those devices where an integrated circuit is contained within an ISO 1 identification card piece of plastic. The card is 85.6mm x 53.98mm x 0.76mm and is the same as the ubiquitous bank card with its magnetic stripe that is used as the payment instrument for numerous financial schemes.

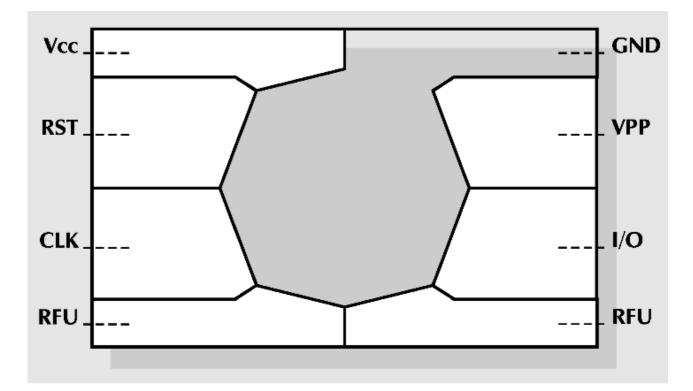

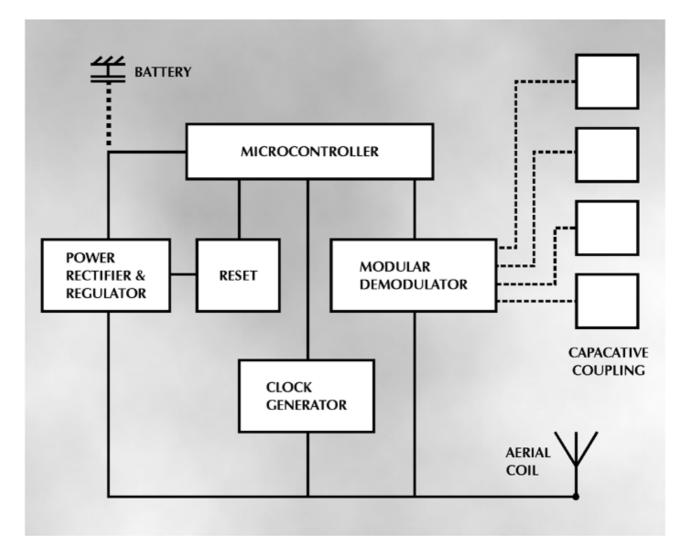

Integrated Circuit Cards come in two forms, contact and contactless. The former is easy to identify because of its gold connector plate (fig 1). Although the ISO Standard (7816-2) defined eight contacts, only 6 are actually used to communicate with the outside World. The Contactless card may contain its own battery, particulary in the case of a "Super Smart Card" which has an integrated keyboard and LCD display. In general however the operating power is supplied to the contactless card electronics by an inductive loop using low frequency electronic magnetic radiation. The communications signal may be transmitted in a similar way or can use capacitive coupling or even an optical connection.

Figure 1: ISO ID 1Card

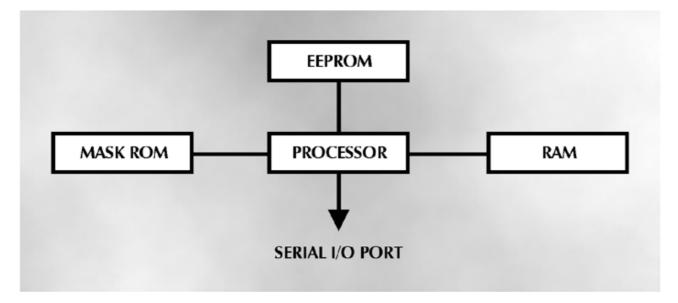

The Contact Card is the most commonly seen ICC to date largely because of its use in France and now other parts of Europe as a telephone prepayment card.. Most contact cards contain a simple integrated circuit although various experiments have taken place using two chips. The chip itself varies considerably between different manufacturers and for a whole gambit of applications. Let us consider first the purpose for the 6 contacts used by the ICC (fig 2)

Vcc is the supply voltage that drives the chips and is generally 5 volts. It should be noted however that in the future we are likely to see a move towards 3 volts taking advantage of advanced semiconductor technology and allowing much lower current levels to be consumed by the integrated circuit. Vss is the substrate or ground reference voltage against which the Vcc potential is measured. Reset is the signal line that is used to initiate the state of the integrated circuit after power on. This is in itself an integral and complex process that we shall describe later in more detail.

The clock signal is used drive the logic of the IC and is also used as the reference for the serial communications link. There are two commonly used clock speeds 3.57 MHZ and 4.92 MHZ. The lower speed is most commonly used to date in Europe but this may change in the future. One may be tempted to ask why these strange frequencies were chosen, why not just a straight 5 MHZ. The reason lies in the availability of cheap crystals to form the clock oscillator circuits. Both of these frequencies are used in the television world for the colour sub carrier frequency. The PAL system operates using 4.92 MHZ whilst the 3.57 MHZ is used by the American NTSC standard. The the Vpp connector is used for the high voltage signal that is necessary to program the EPROM memory. Last, but by no means least is the serial input/output (SIO) connector. This is the signal line by which the chip receives commands and interchanges data with the outside world. This is also a fairly complex operation and will be the subject of a more detailed discussion where symbols such as T0 and T1 will be fully explained.

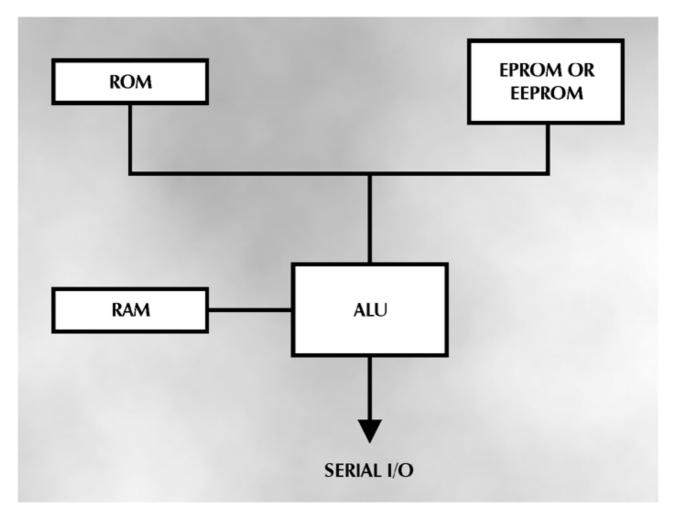

So what does the chip contain, well the primary use of the IC card is for the portable storage and retrieval of data. Hence the fundamental component of the IC is a memory module. The following list represents the more commonly used memory types,

- ROM Read only memory (mask ROM)

- PROM Programmable read only memory

- EPROM Erasable programmable ROM

- EEPROM Electrically erasable PROM

- RAM Random access memory

A particular chip may have one or more of these memory types. These memory types have particular characteristics that control their method of use. The ROM type of memory is fixed and can not be changed once manufactured by the semiconductor company. This is a low cost memory, in that, it occupies minimum space on the silicon substrate. The use of the silicon is often referred to as real estate because clearly one wants to get as much as possible into the smallest possible space. The snag however is that it can not be changed and takes several months to be produced by the semiconductor company. There is also effectively a minimum order quantity in order to achieve this low cost.

In order of increasing real estate the PROM comes next. This memory is programmable by the user through the use of fusible links. However high voltage and currents are required for the programming cycle and such devices are not normally used in Integrated Circuit Cards. The EPROM has been widely used in the past but the name for this application is something of a misnomer. Whilst the memory is erasable, by means of ultra violet light, the necessary quartz window is never available in the ICC and the memory is really used in one time programmable mode (OTP). Getting pretty heavy in real estate terms is the EEPROM. This memory is indeed erasable by the user and can be rewritten many times (between 10,000 and 1,000,000 in a typical implementation) All of these memories describe so far are non volatile. In other words when the power is removed they still retain their contents. The random access memory (RAM) is a different kettle of fish, this is volatile memory and as soon as the power is removed the data contents is lost.

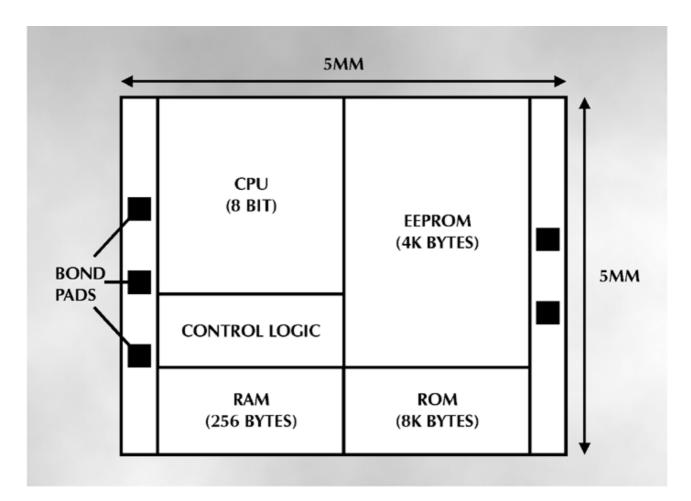

In order to pursue our studies further we must note that the cost of the IC at saturation (i.e when development costs have been recouped) is proportional to the square area of silicon used (assuming constant yield). The ISO connector is so designed to constrain the silicon die size to about 25mm<sup>2</sup> (although it is possible to handle 35mm<sup>2</sup> or more). However the important point is more concerned with reliability where clearly the larger die will be more prone to mechanical fracture. There is another bi- product that we will consider later where the cost of testing and personalisation are considerable altered by the complexity of the particular chip. It is clear however that we should attempt to minimise the contents of the chip on both cost and reliability grounds commensurate with the particular application .

Well of course you can't have something for nothing and although a telephone card may operate with a little EEPROM memory (128 - 512 bytes) and the memory control logic, more sophisticated applications will demand ROM, EEPROM, RAM and a CPU (Central Processing Unit) to achieve the necessary business. It is the addition of the CPU or micro-controller that really leads to the term "Smart" although we will not be rigorous in our use of the term.

The control logic should not be overlooked as this is necessary not only for communication protocols but also to offer some protection of the memory against fraudulent use. The ICC is probably the security man's dream because unlike most electronic storage and processing devices it has security intrinsically built in. The ICC really does provide a tamper resistant domain that is difficult to match with the some what larger security boxes that handle cryptographic processes.

So now we can differentiate the different types of ICC by their content,

■ Memory only

■ Memory with security logic

■ Memory with CPU

The security logic can be used to control access to the memory for authorized use only. This is usually accomplished by some form of access code which may be quite large (64 bits or more). Clearly the use of EEPROM memory must be strictly controlled where fraudsters can obtain a financial advantage by unauthorized use. This applies as much to telephone cards as applications using ICC for cryptographic key carriers. The security advantage of the CPU device is of course more significant because the CPU is capable of implementing cryptographic algorithms in its own right, but we will discuss this in more detail in due course.

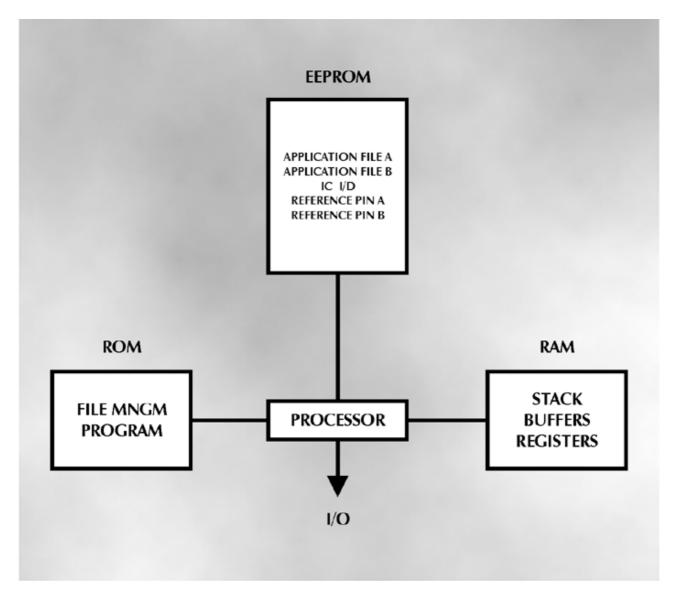

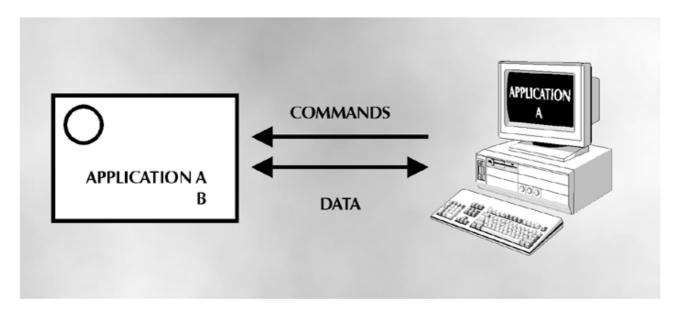

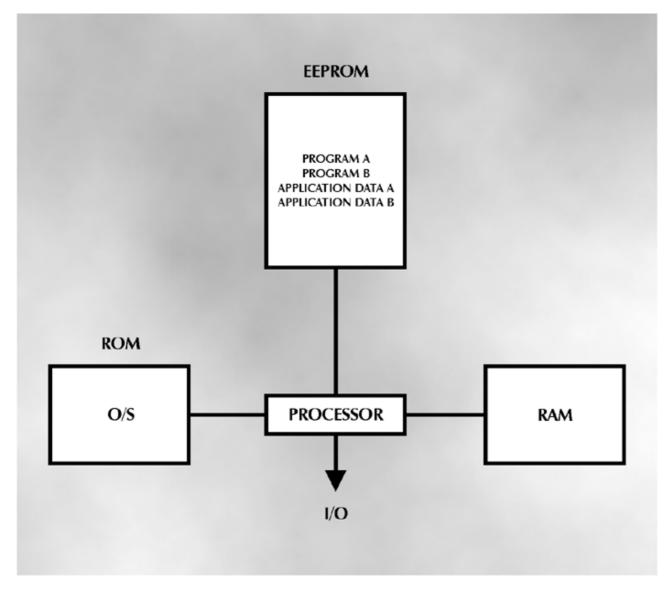

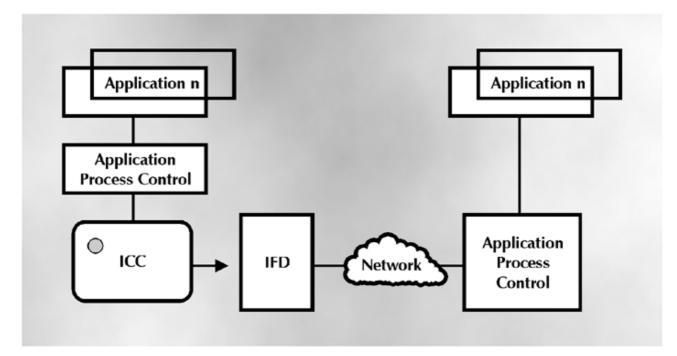

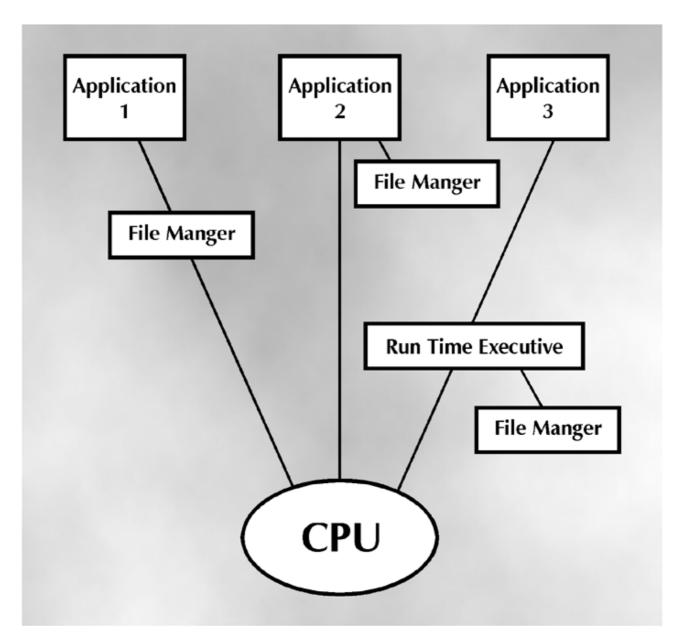

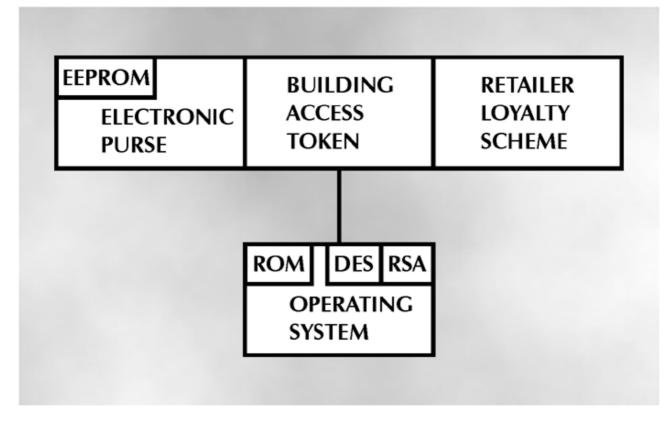

In the Smart Card world the term application is widely used to describe the software or programs that the IC implements. In the simplest case the application may be just a file manager for organising the storage and retrieval of data. Such an application may be totally implemented in the logic of the chip. Similarly the chip must contain the communications logic by which it accepts commands from the card acceptance device (CAD) and through which it receives and transmits the application data. The ICC which contains a CPU can handle more sophisticated applications and even multi applications since the CPU is also capable of processing the data and taking decisions upon the various actions that may be invoked. The subject of mult applications and particulary the implementation of security segregation is another subject for more detailed discussion in subsequent parts.

## Smart Card Tutorial - Part 2

### First Published in October 1992

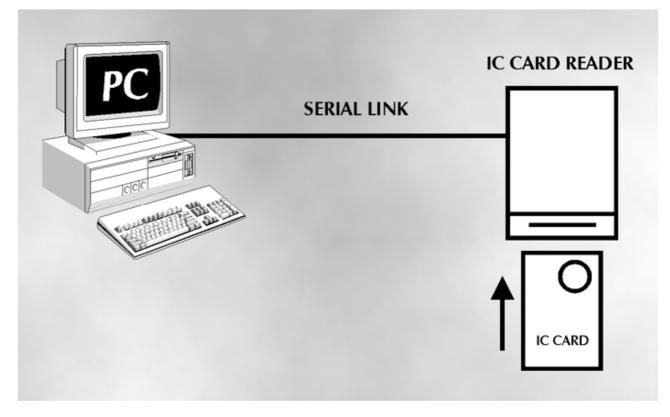

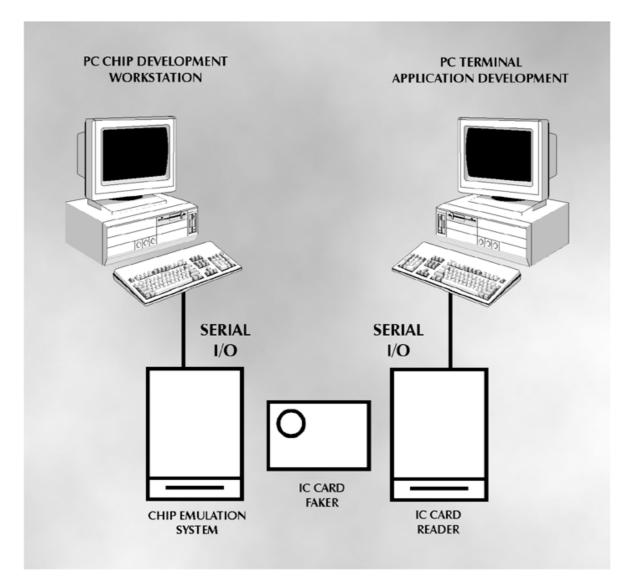

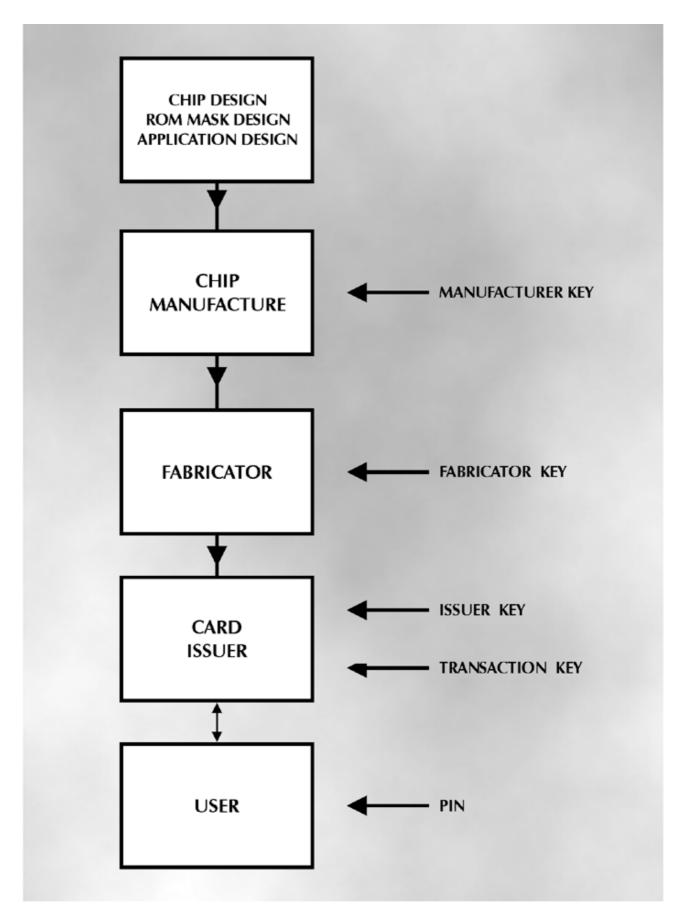

#### How the IC card is made

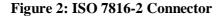

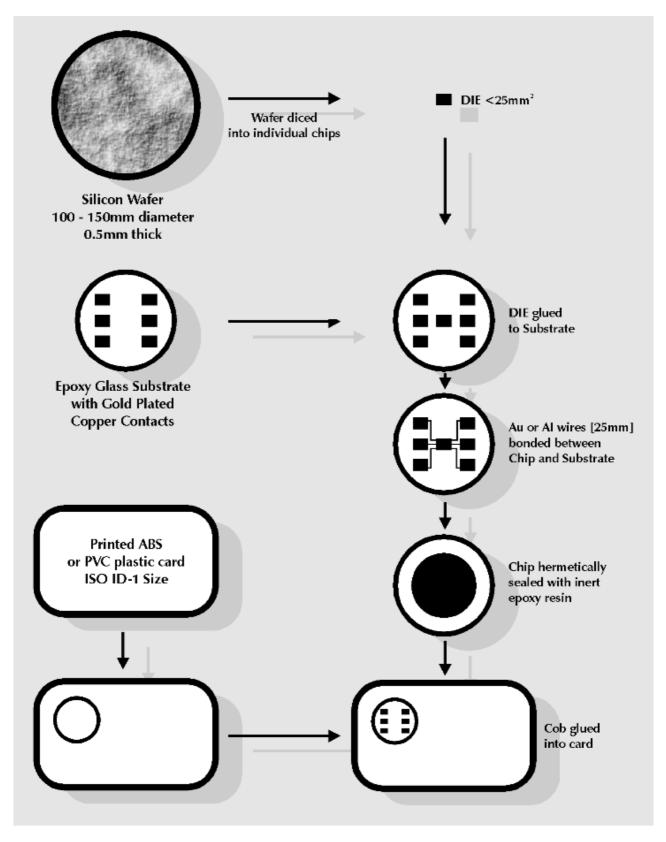

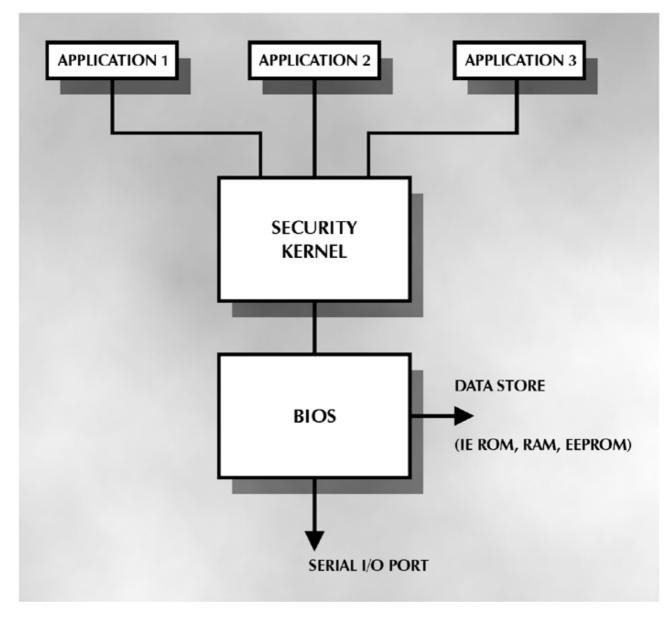

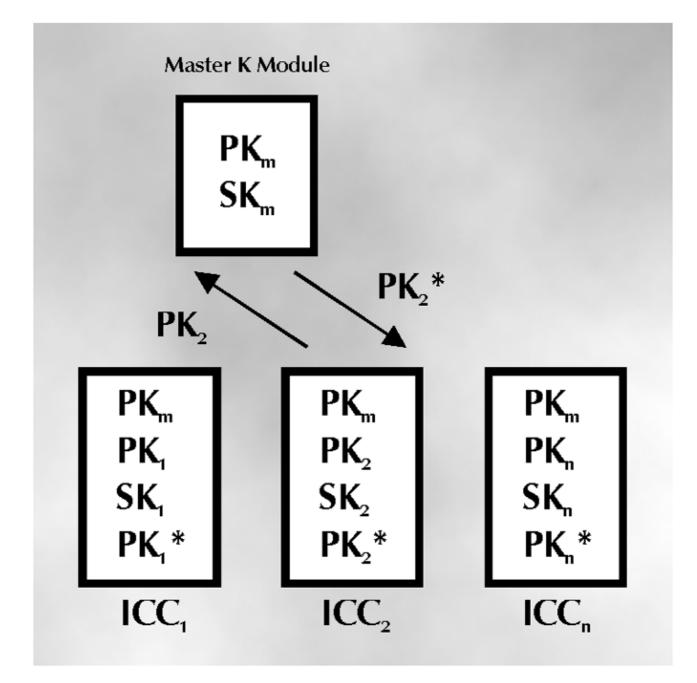

The manufacture of a smart card involves a large number of processes of which the embedding of the chip into the plastic card is key in achieving an overall quality product. This latter process is usually referred to as card fabrication. The whole operation starts with the application requirements specification. From the requirements individual specifications can be prepared for the chip, card, mask ROM software and the application software. The ROM software is provided to the semiconductor supplier who manufactures the chips. The card fabricator embeds the chip in the plastic card. It is also quite normal for the fabricator to load the application software and personalisation data. Security is a fundamental aspect in the manufacture of a smart card and is intrinsic to the total process. However we will consider security separately in subsequent articles in this series. We will look at each of the stages in the manufacture of the smart card as shown in figure. 1.

Figure 1: Stages in the manufacture of a Smart Card

## **Chip specification**

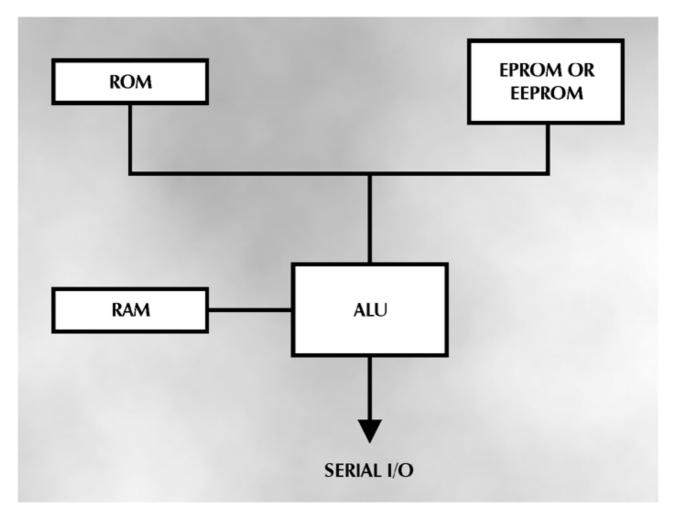

There are a number of factors to be decided in the specification of the integrated circuit for the smart card. For the purpose of this discussion we will consider a CPU based card although the manufacture of a memory card is substantially a subset of that described here. The key parameters for the chip specification are as follows,

- Microcontroller type (e.g 6805,8051)

- Mask ROM size

- RAM size

- Non volatile memory type (e.g EPROM, EEPROM)

- Non volatile memory size

- Clock speed (external, and optionally internal)

- Electrical parameters (voltage and current)

- Communications parameters (asynchronous, synchronous, byte, block)

- Reset mechanism

- Sleep mode (low current standby operation)

- Co-processor (e.g for public key cryptography)

In practice the semiconductor manufacturers have a range of products for which the above parameters are pre-defined. The task of the designer is therefore concerned with choosing the appropriate product for the particular application. As mentioned previously security may be an important issue for the application and accordingly there may be extra requirements on the physical and logical security offered by the particular chip. Conformance to ISO standards is also likely to be a requirement and in this area ISO 7816 - 3 (Electronic signals and transmission protocols) is the principle standard to be considered. It should be noted however that ETSI (European Telecommunications Standard Institute) are currently developing new standards for the CEN TC224 committee. These standards are more stringent than that described by the ISO standards. For example the ISO 7816-3 allows a card current supply of up to 200 mA. ETSI have recommended 20mA for normal use and 10mA for applications such as portable phones.

## Card specification

The specification of a card involves parameters that are common to many existing applications using the ISO ID-1 card. The following list defines the main parameters that should be defined,

- Card dimensions

- Chip location (contact card)

- Card material (e.g PVC, ABS)

- Printing requirements

- Magnetic stripe (optional)

- Signature strip (optional)

- Hologram or photo (optional)

- Embossing (optional)

- Environmental parameters

The characteristics of the smart card are part of the ISO 7816 part 1 (physical) and 2 (contact location) standards. The choice of chip location has been a difficult subject due largely to the use of magnetic stripes. The early French cards put the IC module further off the longitudinal axis of the card than the standard eventually agreed by ISO.

This was preferable because of the residual risk of chip damage due to bending. The French Transac tracks were lower on the card which also made this position preferable. The now agreed ISO standards for magnetic stripes resulted in the French chip position and the magnetic stripe being coincident. Hence the now agreed lower location which does of course result in higher bending stress on the chip. The ISO 7816-2 standard does however allow the position of the contacts to be either side of the card. More recently there have been moves to remove this option with the front (opposite to the side containing the magnetic stripe) being the preferred position for the IC connector.

The choice of card material effects the environmental properties of the finished product. PVC was traditionally used in the manufacture of cards and enabled a higher printing resolution. Such cards are laminated as three layers with transparent overlays on the front and back. More recently ABS has been used which allows the card to be produced by an injection moulding process. It is even proposed that the chip micromodule could be inserted in one step as part of the moulding process. Temperature stability is clearly important for some applications and ETSI are particulary concerned here, such that their higher temperature requirement will need the use of polycarbonate materials.

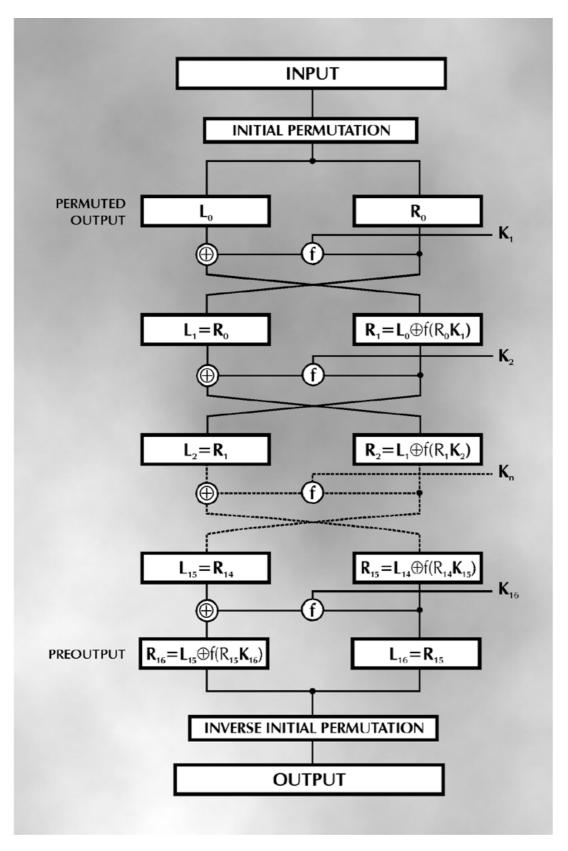

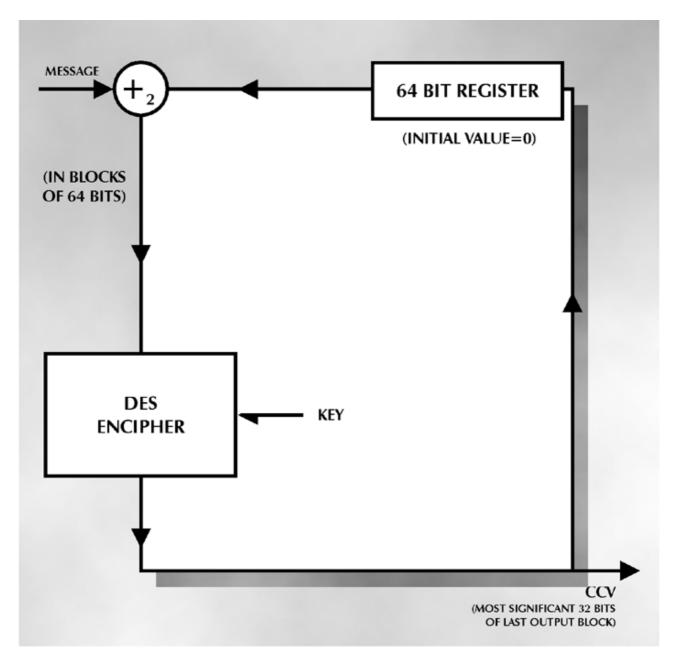

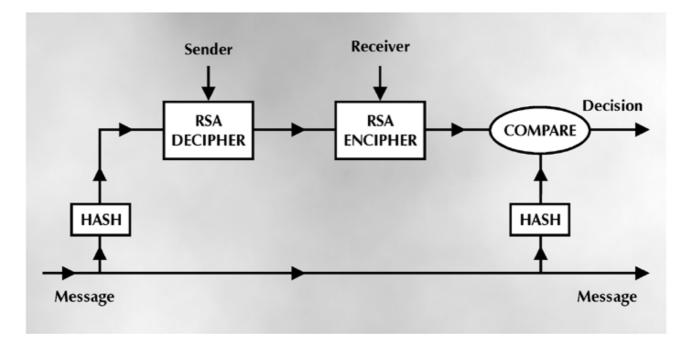

#### Mask ROM Specification

The mask ROM contains the operating system of the smart card. It is largely concerned with the management of data files but it may optionally involve additional features such as cryptographic algorithms (e.g DES). In some ways this is still a relatively immature part of the smart card standards since the early applications used the smart card largely as a data store with some simple security features such as PIN checking. The relevant part of the ISO standard is 7816-4 (commands). There is a school of thought that envisages substantial changes in this area to account for the needs of multi-application cards where it is essential to provide the necessary security segregation. The developed code is given to the supplier who incorporates this data as part of the chip manufacturing process.

#### **Application Software Specification**

This part of the card development process is clearly specific to the particular application. The application code could be designed as part of the mask ROM code but the more modern approach is to design the application software to operate from the PROM non volatile memory. This allows a far more flexible approach since the application can be loaded into the chip after manufacture. More over by the use of EEPROM it is possible to change this code in an development environment. The manufacturer of a chip with the users ROM code takes on average three months. Application code can be loaded into the PROM memory in minutes with no further reference to the chip manufacturer.

#### **Chip Fabrication**

The fabrication of the card involves a number of processes as shown in fig. 2. The first part of the process is to manufacture a substrate which contains the chip. This is often called a COB (Chip On Board) and consists of a glass epoxy connector board on which the chip is bonded to the connectors. There are three technologies available for this process, wire bonding, flip chip processing and tape automated bonding (TAB). In each case the semiconductor wafer manufactured by the semiconductor supplier is diced into individual chips. This may be done by scribing with a diamond tipped point and then pressure rolling the wafers so that it fractures along the scribe lines. More commonly the die are separated from the wafer by the use of a diamond saw. A mylar sheet is stuck to the back of the wafer so that following separation the dice remain attached to the mylar film.

# Figure 2: Smart Card fabrication process

Wire bonding is the most commonly used technique in the manufacture of smart cards. Here a 25uM gold or aluminium wire is bonded to the pads on the chip using ultrasonic or thermo compression bonding. Thermo compression bonding requires the substrate to be maintained at between 150C and 200C. The temperature at

the bonding interface can reach 350C. To alleviate these problems thermo sonic bonding is often used which is a combination of the two processes but which operate at lower temperatures.

The die mounting and wire bonding processes involve a large number of operations and are therefore quite expensive. Because in general only 5 or 6 wires are bonded for smart card applications this approach is acceptable. However in the semiconductor industry generally two other techniques are used, the flip chip process and tape automated bonding. In both cases gold bumps are formed on the die. In flip chip processing the dice are placed face down on the substrate and bonding is effected by solder reflow. With tape automated bonding the dice are attached by thermocompression to copper leads supported on a flexible tape similar to a 35mm film.

The finished substrate is hermetically sealed with an inert material such as epoxy resin. The complete micromodule is then glued into the card which contains the appropriately sized hole.

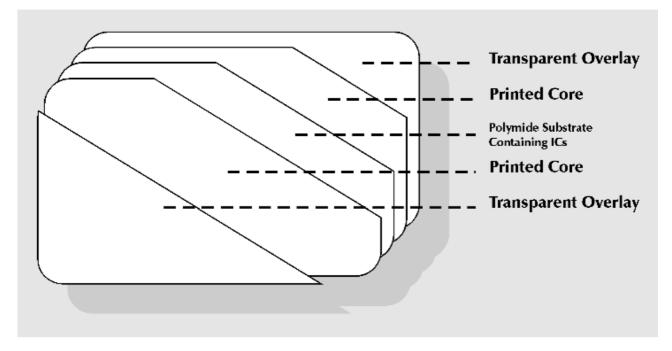

The fabrication of a contactless card is somewhat different since it always involves a laminated card as shown in fig. 3. The ICs and their interconnections as well as the aerial circuits are prepared on a flexible polyimide substrate.

#### Application load

Assuming the application is to be placed in the PROM memory of the IC then the next stage in the process is to load the code into the memory.

This is accomplished by using the basic commands contained in the operating system in the mask ROM. These commands allow the reading and writing of the PROM memory.

#### **Card Personalisation**

The card is personalised to the particular user by loading data into files in the PROM memory in the same way that the application code is loaded into memory. At this stage the security keys will probably be loaded into the PROM memory but as mentioned previously we will explore this in more detail later.

### **Application Activation**

The final operation in the manufacturing process is to enable the application for operation. This will involve the setting of flags in the PROM memory that will inhibit any further changes to be made to the PROM memory except under direct control of the application. Again this is an integral part of the overall security process.

## **Smart Card Tutorial - Part 3**

## First Published in November 1992

### Physical characteristics of the Contact Card

Many observers have commented that the widespread use of smart cards is being impeded by the lack of standards. Interoperability is of course the name of the game and is the primary purpose of standards. The problems of interoperability start at the bottom, in other words with the physical dimensions of the card and the location of the contacts.

These standards are well established and as we shall show in subsequent parts so are the more important characteristics of a smart card that form the basis of the existing and emerging standards. As you move higher in the architecture towards the specification of the application then the problems of interoperability are less relevant since it is not generally necessary to have compatibility between the applications themselves. The biggest hole in the current standards work is the lack of agreement in the security domain which one might argue is fundamental to the application platform. We will discuss this area however in more detail in a subsequent part of this series.

The physical characteristics of an IC card are defined in ISO 7816 part 1. This standard applies to the ID - 1 identification card specified in ISO 7810 and includes cards which may have embossing or magnetic stripes. Whilst we are all familiar with the use of imprinters to obtain a printed version of the embossed characters on some paper voucher, their viability on an IC card must be questionable. The IC module in a smart card is like any other electronic component and is not normally expected to be hit with a hammer at regular intervals. Even the embossing process itself is mechanically stressful and must raise serious doubts over the appropriate migration strategy.

The physical properties of the contact IC card are referenced against earlier card standards and we will look at each of them in turn.

#### ISO 7810 Identification cards - Physical characteristics (1985)

This standard specifies the physical characteristics of identification cards including card material, construction, characteristics and nominal dimensions for three sizes of cards (ID -1, ID -2 and ID -3). It is the ID -1 card that forms the basis of ISO 7816 -1.

The principal parameters of ISO 7810 are the dimensions of the ID -1 card which are defined to be, 85.6mm x 53.98mm x 0.76mm

#### ISO 7811 Identification cards - recording techniques (1985)

This standard is in five parts and covers the specification of the magnetic stripe and the card embossing.

#### Part 1 Embossing

This part specifies the requirements for embossed characters on identification cards for the transfer of data by imprinters or by visual or machine reading.

#### Part 2 Magnetic stripe

This part specifies characteristics for a magnetic stripe, the encoding technique and coded character sets which are intended for machine reading.

## Part 3 Location of embossed characters on ID -1 cards.

As the title implies this part of the standard specifies the location of embossed characters on an ID -1 card for which two areas are assigned. Area 1 is for the number identifying both the card issuer and the card holder. Area 2 is provided for the cardholder identification data such as his name and address.

#### Part 4 Location of magnetic read only tracks - tracks 1 and 2

This standard specifies the location of the magnetic material, the location of the encoded data tracks and the beginning and end of the encoding.

## Part 5 Location of read - write magnetic track - track 3

This standard has the same scope as part 4 except that it defines the read - write track 3. ISO 7812 Identification cards- numbering system and registration procedure for issuer identifiers (1987)

This standard relates to the card identification number or PAN (Primary Account Number) which consists of three parts, the issuer identifier number (IIN), the individual account identifier and the check digit.

## ISO 7813 Identification cards - Financial transaction cards (1987)

This standard defines the requirements for cards to be used in financial transactions. It specifies the physical characteristics, layout, recording techniques, numbering system and registration procedures. It is defined by reference to ISO 7810, ISO 7811 and ISO 7812.

In particular the standard defines more precisely the physical dimensions of the card as follows,

- Width 85.47mm 85.72mm

- Height 53.92mm 54.03mm

- Thickness 0.76mm  $\pm 0.08$ mm

The thickness of the card is particularly important for smart card readers because of the mechanical construction of the card connector mechanism.

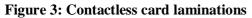

## Figure 1: Bending Test

This device often consists of a movable carriage that positions the card under the connector head whilst applying the necessary wiping and pressure action. Variation in thickness or even slight warping of the card can cause communications failure.

#### ISO 7816 Design and use of identification cards having integrated circuits with contacts (1987)

This standard in its many parts is probably the most important specification for the lower layers of the IC card. The first 3 parts in particular are well established and allow total physical and electrical interoperability as well as defining the communication protocol between the IC card and the CAD (Card Acceptor Device).

## Part 1 Physical characteristics

The physical dimensions of the IC card are defined as that specified in ISO 7813. It should be noted that the thickness dimension does not include any allowance for embossing. More particulary the slot for a card may include an extra indentation for the embossed area of the card. In effect it acts as a polarisation key and may be used to aid the correct insertion orientation of the card. This is an additional characteristic to the magnetic field sensor which operates off the magnetic stripe and is used to open a mechanical gate on devices such as ATM's where some vandal proofing techniques are required.

The part 1 standard also defines additional characteristics that should be met in the manufacturer of an IC card. These characteristics fall into the following categories:

- Ultra violet light

- X rays

- Surface profile of contacts

- Mechanical strength (of cards and contacts)

- Electrical resistance (of contacts)

- Electromagnetic interference (between magnetic stripe and integrated circuit)

- Electromagnetic field

- Static electricity

- Heat dissipation

It has to be said that this part of the standard could be improved and there is currently some work taking place in ISO on this very subject. The three most widely used tests applied by fabricators are specified in the annex to the standard,

- A1 Bending properties

- A2 Torsion properties

- A3 Static electricity

Whilst this is certainly one way of comparing cards fabricated by different companies, whether it bears any relationship to the use of IC cards in the field seems debatable.

The bending properties are tested by deflecting the card on each axis as shown in fig. 1. With a periodicity of 30 bendings per minute the card is deflected to 2 cm at its centre from the long axis and 1 cm from the short axis. The recommended test requires the card to withstand 250 bendings in each of the four possible orientations (i.e 1000 bendings in total).

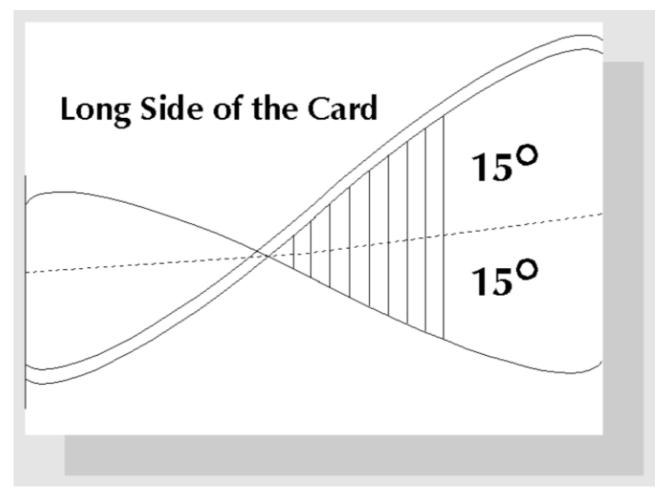

The torsion properties of the card are tested by displacing the card  $\pm 15^{\circ}$  about the long axis at a periodicity of 30 torsions per minute (fig 2). The standard requires the card to withstand 1000 torsions without chip failure or visible cracking of the card.

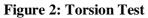

The resistance of the card to static electricity is defined by a test set up as shown in fig 3. The test voltage is defined to be 1.5KVolts. The specification requires this voltage to be discharged across each of the contacts in both normal and reverse polarity. The IC should still be operational at the end of the test.

One of the issues surrounding the use of the IC card relates to the temperature range for operational use. ISO 7810 defines that the ID-1 card should be structurally reliable and usable between  $-35^{\circ}$  C and  $+50^{\circ}$  C. The draft CEN standard on requirements for IC cards and terminals for telecommunications use, part 2 - application independent card requirements (EN 726-2) defines more stringent requirements for operational use as  $-25^{\circ}$  C to  $+65^{\circ}$  C with occasional peaks up to  $+70^{\circ}$  C. In addition the draft identifies multi-application cards for portable battery operated equipment to be used between  $-25^{\circ}$  C and  $+70^{\circ}$  C with occasional peaks of up to  $+85^{\circ}$  C. The word occasional is defined to mean not more than 4 hours each time and not over 100 times during the life of the card.

#### Figure 3: ESD Test

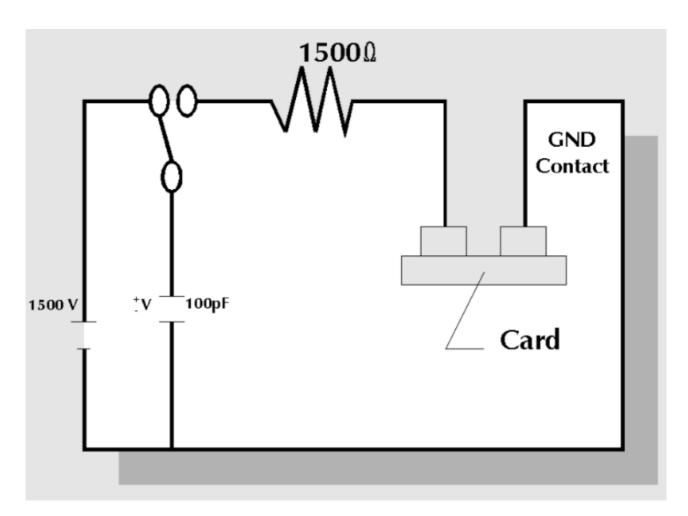

#### ISO 7816 Part 2 - Contact Locations and Minimum Size

This part of the standard has taken a lot of effort in order to reach agreement. Early applications of smart cards emanated in France where the Transac magnetic stripes were more central on the card than that eventually defined by ISO 7811. Unfortunately the French chip position overlaps the ISO magnetic stripe definition. As a result it was eventually agreed that after a transitional period (to the end of 1990) the position for the IC connector would be as shown in fig 4. This position is much closer to the longitudinal axis of the card. We might like to conjecture on which is the better position for the chip in terms of mechanical stress but perhaps we should just settle for agreement.

Figure 4: Contacts Location

## Figure 5: Relative Locations

Further problems arose in deciding on which face of the card the connector should be located. In order to avoid further delay in publishing the standard, two options were allowed to include both the front and back of the card. This anomaly has been a source of irritation and it is now widely agreed that the IC connector should be on the front of the card. For this purpose the back is defined to be the side with the magnetic stripe. The embossing is defined to be on the front of the card and therefore on the same side as the IC connector. The relative location of these components (when present) is shown in fig 5.

## Smart Card Tutorial - Part 4

### First Published in December 1992

#### Electronic Signals and Transmission Protocols.

The electronic properties and transmission characteristics of the IC card are fundamental to interoperability. These specifications are defined by ISO as part three of the 7816 standard. This standard is subject to an amendment for the T=1 transmission protocol and a proposed review for protocol type selection (PTS). The principal subjects to be considered are as follows,

- Electrical characteristics

- Character transmission

- Answer to reset (ATR)

- T=0 transmission protocol

- T=1 transmission protocol

- Protocol type selection (PTS)

We will consider each of these topics in turn.

#### **IC Card Electrical Characteristics**

We have previously discussed the position and definition of the IC connector and have identified 8 contacts of which 6 are currently defined,

- $\blacksquare$  V<sub>CC</sub> Power supply

- GND Ground or reference voltage

- CLK Clock

- $V_{PP}$  Programming voltage

- RST Reset signal

- I/O Serial Input/Output

#### **Power supply (VCC)**

The power supply to the IC is defined to be between 4.75 volts and 5.25 volts with a maximum current consumption of 200mA. Both of these parameters have problems. Newer chip fabrication technologies are moving sub micron, 0.8um is already commercially available and 0.5um is not that far away. These chips may operate with a supply voltage of 3 volts which results in lower current consumption. Most card acceptor devices (CAD) operate at 5 volts as specified in the ISO standard. Whilst a 3 volt IC may be designed to operate between 3 volts and 5 volts, running a 5 volt IC at 3 volts is a non starter.

A current consumption of 200mA is far too high for modern electronic equipment particulary when the equipment is portable and driven by a battery power supply. Most IC cards have a power consumption of between 10mA and 20mA (at 3.58MHz). ETSI in the development of their standards have adopted a far more rigorous specification of 20mA maximum for normal use and a 10mA maximum for use in portable equipment. They further defined the concept of sleep mode (not covered by ISO 7816-3) where the IC chip can reside in a latent mode preserving volatile memory contents with a maximum power consumption of 200uA.

#### Clock signal

Although the integrated circuit could contain its own clock circuit for driving the internal logic, in practice most IC chips are supplied with an external clock by the interface device. It should be noted that the speed of the serial communications on the I/O line is effectively defined by the frequency of this clock. The ISO standard aligns with the use of two widely used external clock frequencies, 3.579545 MHz and 4.9152

MHz. The former frequency is the more widely used (being based on the NTSC colour sub carrier frequency) and results in a clock divider of 372 in order to produce a 9600 bit per second (not exact but within tolerance) serial communication speed. The latter frequency has a simple divisor of 512 in order to achieve a 9600 bit per second communication speed. The standard defines the situation after reset whilst allowing the frequency to be selectively changed by means of protocol type selection.

## **Programming voltage V**<sub>PP</sub>

This signal is designed to provide the high voltage required to enable writing to the non volatile memory. The more popular IC'c use EEPROM memory where the high voltage is generated by a charge pump on chip. However the EPROM memory type needs the high voltage (usually 12.5V or 21V) to be externally provided on the IC connector. There have been problems in the past with terminals supplying the wrong programming voltage with somewhat drastic effects. Because of this and the significant advantages of having a rewriteable memory the EEPROM memory is by far the most popular for IC card applications, hence the role of  $V_{PP}$  is rapidly diminishing.

## The Reset Signal

The reset signal is asserted by the interface device and is used to start up the program contained in the IC ROM. The ISO standard defines three reset modes, internal reset, active low reset and synchronous high active reset. Most microprocessor ICs operate using the active low reset mode were the IC transfers control to the entry address for the program when the reset signal returns to the high voltage level. The synchronous mode of operation is more commonly met with the memory card ICs as used for telephone applications.

The sequence of operations for activating and deactivating the IC is defined in order to minimise the likelihood of damage to the IC. In particular the inadvertent corruption of the non-volatile memory (EPROM or EEPROM) must be avoided. The activation sequence for the interface device is defined as follows,

- Take RST low

- Apply V<sub>CC</sub>

- Put I/O in receive mode

- Put  $V_{PP}$  in idle mode

- Apply clock

- Take RST high (active low reset)

The IC deactivation sequence for the interface device is as follows,

- Take RST low

- Take clock low

- $\blacksquare$  Deactivate V<sub>PP</sub>

- Put I/O in the low state

- Deactivate V<sub>CC</sub>

#### Serial Input/Output (I/O)

The ISO standard defines a single line for the interchange of data between the IC and the interface device. This means that the line must change direction depending on whether the IC is transmitting or receiving. In practice this cannot be instantaneous and the expression 'line turnaround time' is commonly encountered in the modem world. The transmission protocol must take account of this need to turn the line around.

## Character Transmission.

The transmission characteristics operated by most microprocessor IC cards are based on an asynchronous half duplex mode of operation. In the T=0 communication protocol this involves the transmission of bytes whilst the T=1 protocol defines a block mode of operation. As we have already observed the serial communication is operated by the use of a single chip connector, where the direction of data transmission has to change depending on whether the IC card or interface is transmitting data. This is referred to as half duplex communication whereas two I/O signal connectors would be required for full duplex operation where transmission can take place in both directions concurrently.

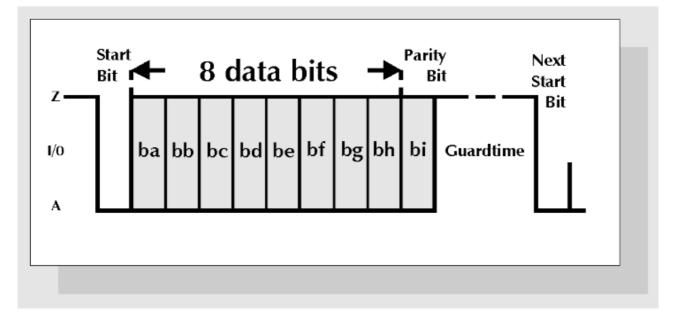

The asynchronous type of transmission is similar to that used by the serial RS232C connector met on the personal computer. Although the PC operates in full duplex mode. The transmission of a single character (defined as 8 bits) requires an overhead of several bits as follows,

- Start bit (used for character frame synchronisation)

- Parity bit (for error detection)

- Guardtime (separation between characters)

#### Figure 1: Asynchronous Character Frame

The format of a character frame is shown in fig.1. The receiver examines the I/O looking for the transition from the mark or high state to the space or low state. The sampling of the line is required to be such that the receiver monitors the state of the line in the centre of each bit period with a precision of + 20%. The parity bit is defined to achieve even parity which means that the number of 1's in the 8 data bits and the parity bit together results in an even number.

The guard time is defined to be equal to two bit periods (although for block mode it can be changed to a 1 bit period). This is similar to having two stop bits on a UART (Universal Asynchronous Receiver Transmitter) as used in the PC.

A more common definition of the asynchronous serial transmission at reset would be 9600 bits/second, 8 data bits, even parity, 2 stop bits with half duplex mode of operation. The half duplex refers only to data transmissions in one direction at a time which a PC is perfectly capable of managing with its UART. The RS232C interface however defines two separate wires for data transmission and reception which would need hardware modification in order to interface with the single wire IC card directly.

There is a further problem with the asynchronous character transmission that makes life difficult for a PC to act as the interface device. The 7816-3 standard defines an error detection and recovery operation (mandatory for T=0) that cannot be managed by the normal PC UART. When the receiver detects a parity error on reception it takes the I/O line to the space or low state in the middle of the first stop bit guard time. The transmitter is mandated to sample the I/O line at the start of the second stop bit guard time period. When the error condition is sensed then the transmitter should retransmit the erroneously received character. Clearly the transmitter cannot be outputting stop bits but must let the line go high during the guard time in order to sense the line state. Given the close coupling normally achieved between an IC card and the interface device one has to question whether this level of error control has sufficient benefits to outweigh the disadvantages. Error control at a higher level in the OSI model is preferable in this situation and although this could be handled at the application level the T=1 communication protocol applies error control at the frame level.

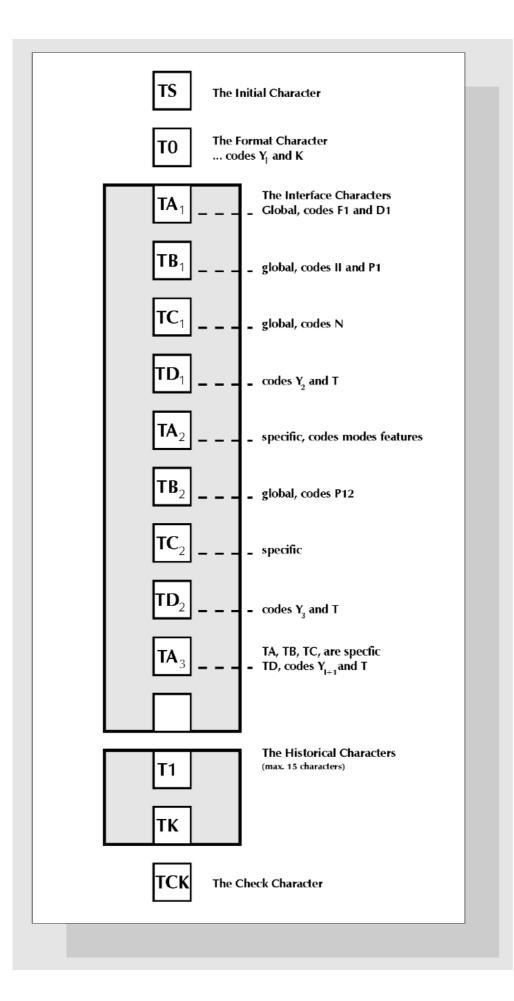

#### Answer to reset

After the reset signal is applied by the interface device the IC card responds with an answer to reset. For the active low reset mode the IC should respond between 400 and 40,000 clock cycles after the rising edge of the reset signal. The answer to reset is at most 33 characters (including the initial character) and consists of 5 fields,

- The initial character (TS)

- The format character (TO)

- $\blacksquare \qquad The interface characters (TA_i, TB_ii, TC_i, TD_ii,)$

- The historical characters (T1,T2. TK)

- The check character (TCK)

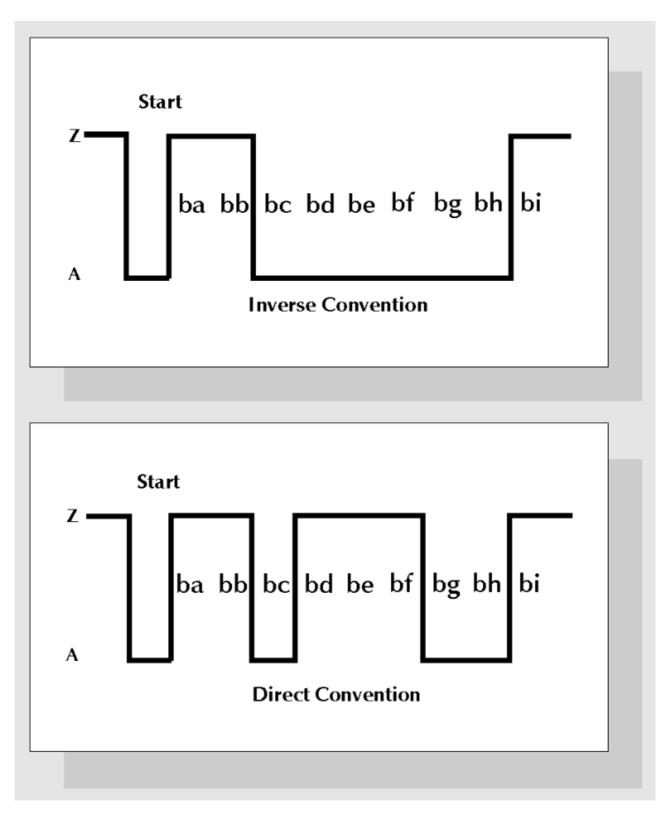

Figure 2: General Configuration of the Answer-to-Reset Each of these fields is sent in order as shown in fig.2. The initial character TS is really a bit synchronisation pattern which may be sent in order to determine the data transmission rate (auto baud rate sensing) and also to determine the sense of the logic. The format of the TS character is shown in fig. 3. This shows the two possibilities of the direct and inverse convention. In the inverse convention where the logic level 1 is the space or low state the most significant bit is transmitted first. With the direct convention where the logic level 1 is the mark or high state then the least significant bit is transmitted first. This means that the selection of the appropriate logic sense will result in the initial character being interpreted as `3F' for the inverse convention and `3B' for the direct convention in hexadecimal coding.

### **Figure 3: Initial Character TS**

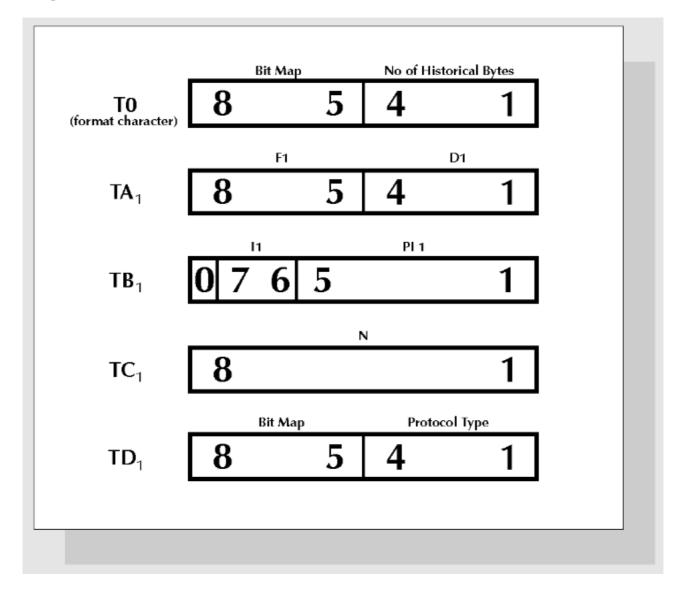

The format character TO provides information necessary to interpret the remaining answer to reset characters. The most significant 4 bits use a bit map to indicate the presence or otherwise of TA1, TB1, TC1 and TD1. For example if the most significant bit (b8) is set then TD1 is present in the interface characters field. Similarly the presence of TC1 is indicated by the state of the `b7' bit and so on.

The least significant 4 bits of the TO formal character give the number (binary encoded) of bytes in the historical field. The use of 4 bits restricts the maximum size of the historical character field to 15 bytes. The interface characters (TAi, TBi, TCi, TDi,) are the complex part of the answer to reset. They carry information relating to the available communication protocols as well as the programming voltage and current parameters for the EPROM. There is currently a proposed revision to the ISO 7816-3 to remove ambiguities and to ensure an effective method of operation for changing the protocol type and the protocol parameters. Much of the complexity is brought about by the desire to achieve backward compatibility with commercial implementations of the T=O communication protocol. At the current time there are commercial applications running either the T=O or T=1 communication protocol whilst multi-protocol operation is somewhat scarce.

The proposed revisions to the standard may alter this situation. We will discuss the interface bytes and protocol type selection against these proposed revisions but readers are warned that these recommendations are only provisional.

The interface bytes (which are optional) are defined in fig.4. The T0 and TDi characters contain bit maps which indicate the presence or otherwise of the following  $TA_1$ ,  $TB_1$ ,  $TC_1$ , and  $TD_1$  bytes.

The  $TA_1$ ,  $TB_1$ ,  $TC_1$ , and  $TB_2$  characters are referred to as the global interface bytes and are fundamental to the operation of the card.

$TA_1$  defines the basic characters of the serial transmission, FI is the clock rate conversion factor and DI is the bit rate adjustment factor. The binary encoded fields are compared against tables supplied in the standard to achieve actual values for F and D as defined below,

Initial  $etu = \frac{372}{f} \sec(f \text{ usually} = 3.579545MHz)$ Work  $etu = \frac{1}{D} x \frac{F}{f} \sec(\frac{1}{D} x \frac{F}{f})$

An elementary time unit (etu) is the nominal bit duration used in the character frame. Thus as described previously one character frame is equal to 12 etu (1 start etu, 8 data etu, 1 parity etu, 2 guard time etu).

The default values for F1 and D1 are 1 which is defined in the tables to give a value for F of 372 and D of 1. Hence the work and initial etu are the same. At these default values the frequency of the clock should be in the range 1MHz - 5MHz.

$TB_1$  is used to define the EPROM programming voltage and current. The value of II and PI1 are used against tables to obtain the value of I mA and P volts. It should be noted that  $TB_2$  is used to define the programming voltage with higher granularity (8 bits instead of 5).

$TC_1$  provides the value of N which defines the extra guard time to be used between successive characters. N can be in the range 0 - 254 etu. When N is equal to 255 this indicates that the minimum guard time (2 etu for T = 0 and 1 etu for T = 1) should be used. As noted previously the T = 0 communications protocol requires the extra guard time to enable the parity error detection and signalling to be implemented.

$TD_1$  indicates the protocol type TDI as between 0 and 15:

| T = 0   | Asynchronous half duplex byte transmission          |

|---------|-----------------------------------------------------|

| T = 1   | Asynchronous half duplex block transmission         |

| T = 2/3 | Reserved for full duplex operation                  |

| T = 4   | Reserved for enhanced half duplex byte transmission |

| T = 513 | Reserved for further use (RFU)                      |

| T = 14  | Non ISO protocols                                   |

| T = 15  | Reserved for future extension                       |

It should be noted that Japan uses T = 14 for a National block asynchronous protocol.

The  $TD_1$  byte also contains a bit map that indicates the presence or otherwise of  $TA_2$ ,  $TB_2$ ,  $TC_2$  and  $TD_2$ .

The proposed revision defines a new use for the  $TA_2$  interface byte which has a special role in the selection of communication protocols and parameters. We will discuss this further in the communications section.

#### The Historical Characters

The historical characters may be used to convey information relating to the life cycle of the card. There are clearly other possibilities and the use of these characters is still subject to agreement. This subject is being considered further as part of the emerging part 4 of the ISO 7816 standard.

## The Check Character (TCK)

The check character should not be sent when only the T = 0 protocol is indicated in the answer to reset. In all other cases TCK is sent as the last character of the ATR. The check character is calculated such that the Exclusive OR of all the bytes from T0 to TCK inclusive is equal to zero.

Next Edition: 1993 Volume

We will continue with a discussion of the T = 0 and T = 1 communications protocols along with an explanation of protocol type selection (PTS)

## Smart Card Tutorial

## First Published in January 1993

## **Part 5 - Communication Protocols**

At the current time there are two communication protocols that are in general use,

- $\blacksquare$  T = 0 asynchronous half duplex character transmission

- $\blacksquare T = 1 ext{ asynchronous half duplex block transmission}$

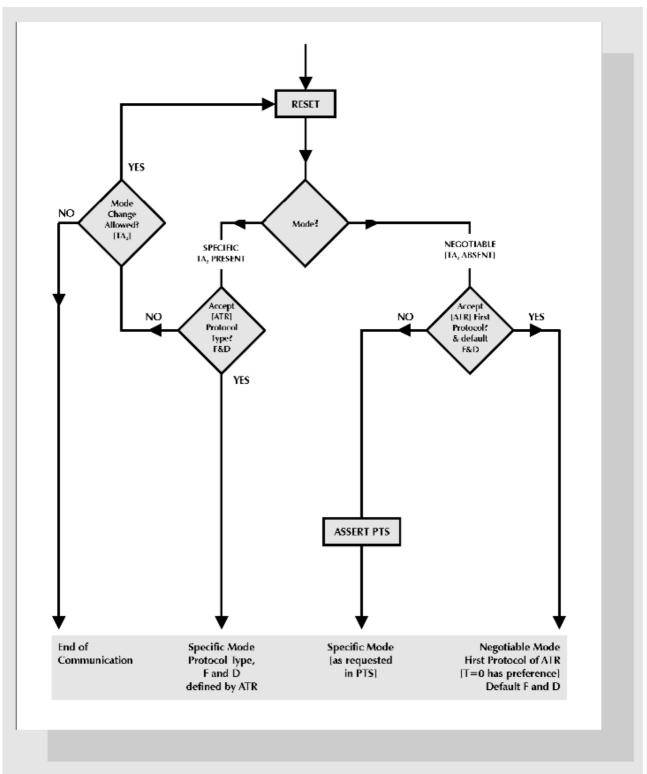

The T = 0 protocol is the predominant protocol in France and was the only protocol specified in ISO 7816 - 3. In 1992 ISO standardised the T = 1 protocol as amendment 1 to ISO 7816 - 3. Clearly the IC card and the interface device must operate with a common protocol. The method by which they achieve a common optimum configuration has been the subject of much discussion over the last few years. This principle is intended to be achieved by the use of protocol type selection (PTS). This is effectively a special command sent from the interface device to the ICC after the answer to reset. In order to maintain backward compatibility with existing commercial systems that may only be capable of handling the T=0 communication protocol some changes are necessary to the original ISO 7816-3 standard. A new concept is proposed which identifies the principle of two modes of operation,

- Negotiable mode

- Specific mode

An ICC that operates in a negotiable mode may have its communication protocol changed by the use of the PTS command. An ICC that operates in the specific mode cannot accept a PTS command but may be put into the negotiable mode by a further assertion of the reset command.

Although the ICC indicates to the interface device (by means of  $TA_2$ ) its capability to change to the negotiable mode, an existing device in the market place may however be unaware of these changes and therefore will not be prepared to reset the card.

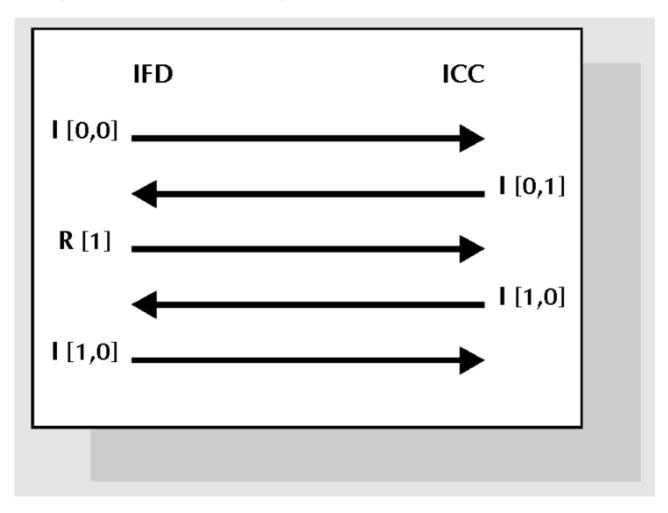

The operation of these mode changes are shown in fig.1. It should be noted that a multi protocol card which by definition offers the negotiable mode of operation should give priority to the T=0 communication protocol. In other words if the T=0 protocol is available it should be the default protocol offered in the answer to reset.

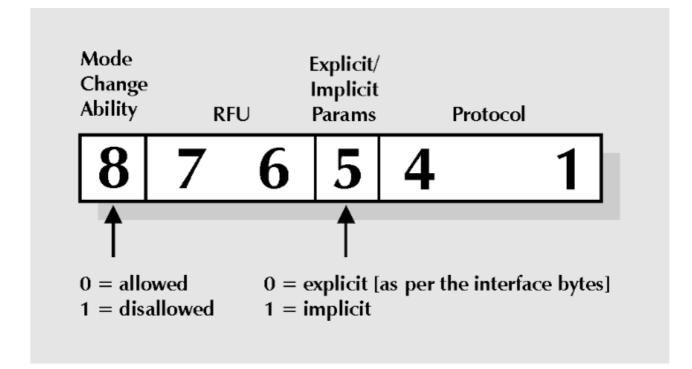

The  $TA_2$  interface byte which is part of the answer to reset data (discussed in part 4) gives the necessary information to allow the appropriate choice of protocol. The coding of this byte when present is shown in fig.2. In fact the presence or otherwise of this byte is used to determine the mode of operation of the card as follows,

- **T** $A_2$  present in ATR Specific mode

- **T** $A_2$  absent in ATR- Negotiable mode

It can be seen that bit 8 in the  $TA_2$  byte is used to tell the interface device whether the card can change to the negotiable mode.

#### Protocol Type selection (PTS)

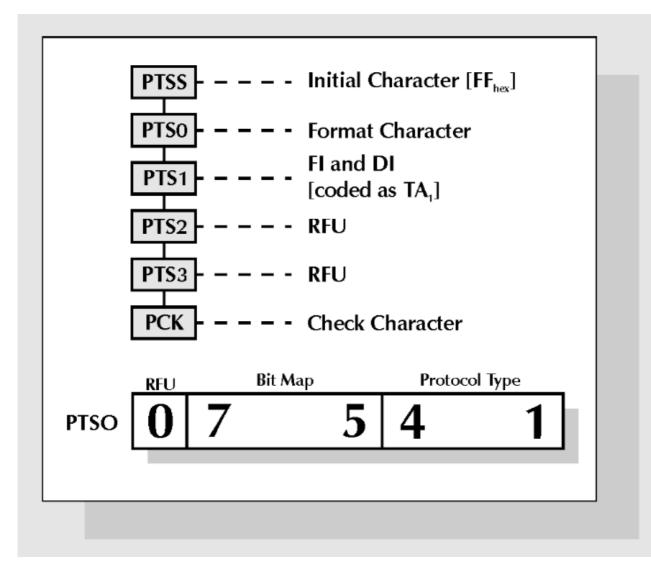

Protocol type selection is used by the interface device to change the communications protocol and/or the default values of FI and DI. The PTS command must be issued immediately after the answer to reset and only applies when the IC card is in the negotiable mode.

The interface device may choose to operate by using the first indicated protocol after the answer to reset and by using the default values of F and D. This results in an implicit selection of the protocol and the communication parameters. Should the interface device wish to effect any change to this situation then it must issue the PTS command.

The PTS request consists of an initial character PTSS (coded  $FF_{hex}$ ), followed by a format character PTSO, and three optional characters PTS1, PTS2, PTS3 and PCK the check character. This is shown in fig.3. The response from the ICC follows the same format as the request.

The PTS0 format character is encoded as shown in fig.3. The bit map is used to indicate the presence or otherwise of PTS1, PTS2 and PTS3. These are encoded by bits 5, 6 and 7 respectively where a logic `1' level indicates the presence of the character. The protocol type is indicated by bits 1, 2, 3 and 4 which are binary encoded for T=0 to T=15.

**Figure 1: Modes of Operation**

The PTS1 character when present is used to define the values for FI and DI as coded for  $TA_1$  (see part 4). These parameters are used for defining the work etu (elementary time unit).

## Figure 2: The TA2 Interface Byte

The check character PCK is computed such that the exclusive OR (XOR) of all the characters from PTSS to PCK inclusive is equal to zero.

When the ICC implements the PTS request message correctly it replies by echoing the same request as the response message. If bit 5 of the PTS1 response character is set to zero then the default values of F and D will be used.

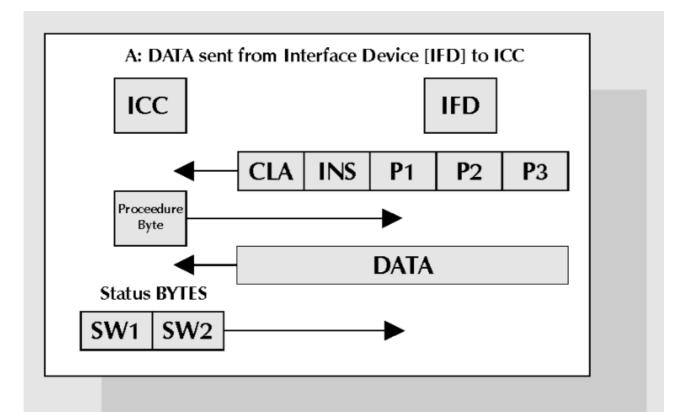

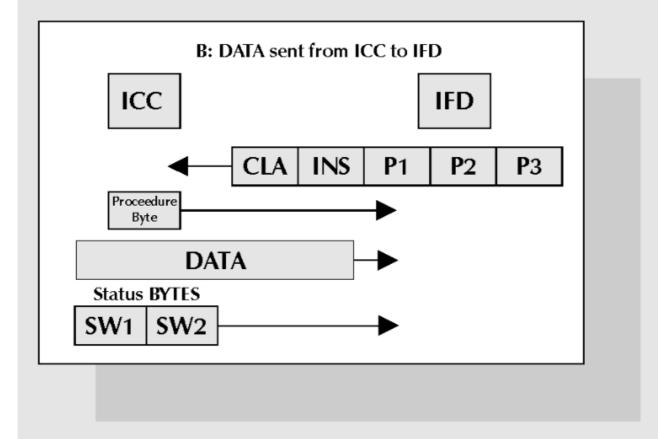

#### The T=0 communication protocol

The interface device always initiates the command for the T=0 protocol. Interaction between the interface device and the ICC results in successive commands and responses. For this protocol, data can only flow in one direction for the command response pair. In other words, either the command message contains data for the ICC or the command request data from the ICC which is then included in the response. The direction of data flow is implicit on the definition of the command and hence both the interface device and the ICC need to have the necessary a-priori knowledge. When it is required to transfer data in both directions for a particular command then a get response command may be used after the primary command to recover the response data.

Figure 3: PTS Request and response

Figure 4: The T=0 Protocol

The command message consists of a 5 character header which the interface device sends to the ICC. The ICC then replies with a procedure byte after which either data is sent to the ICC, or from the ICC, depending on the particular command. This procedure byte is to allow the interface device to control the  $V_{pp}$  EPROM programming voltage. In the case of EEPROM memory this procedure byte is effectively redundant. The message flow for the T=0 protocol is shown in fig.4. The command header consists of the following 5 bytes,

- CLA the instruction class (FF is reserved for PTS)

- INS the instruction code (e.g read memory)

- P1 instruction code qualifier (e.g memory address)

- P2 additional INS code qualifier

- P3 the length of the data block

When P3 is equal to zero the data from the card will be 256 bytes. When data is to be transferred into the card then a zero data transfer is implied.

The normal condition for the ACK procedure byte is for this byte to echo the instruction byte (INS). Other options allow the interface devices to control the  $V_{pp}$  programming voltage as required. The card may optionally send a NULL procedure byte ( $60_{hex}$ ) which allows further time for the processing of the command. In this situation the IFD should await a further procedure byte. The ISO standard also allows the card to send the first status byte (SW1) as the procedure byte.

There are two status bytes SW1 and SW2. These bytes are sent from the ICC to the interface device on completion of the command to indicate the current card status. The normal response is,

SW1, SW2 =  $90_{hex}$ ,  $00_{hex}$

When SW1 = 6X or 9X various error conditions are reported by the card. ISO 7816-3 defines 5 such error conditions,

| SW1  | = 6E - Card does not support instruction class |

|------|------------------------------------------------|

| = 6D | - Invalid INS code                             |

**SW1** = 6B Incorrect reference

= 67 Incorrect length

= 6F no particular diagnosis

The T=0 protocol also includes an error detection and correction mechanism. This was described in part 4 and relies on the receiver detecting a parity error upon which it takes the I/O line to the low logic level within the first etu guard time  $(10.5 \pm 0.2 \text{ etu})$  for a minimum of 1 etu and a maximum of 2 etu. The transmitter looks for this condition and retransmits the corrupt character.

Next month we shall complete the discussion on communications with the T=1 protocol.

## **Smart Card Tutorial**

## First Published in February 1993

## Part 6 - The T = 1 Comms Protocol

The T = 1 communication is an asynchronous half duplex block transmission protocol. In terms of the OSI model this protocol operates at layer 2, the data link layer. The physical layer (layer 1) operates in the same way as for the T = 0 protocol except for the error detection and correction. In essence this protocol puts an envelope around a block of characters which allows,

- flow control

- block chaining

- error correction.

The choice of communication protocol for the ICC is still a hot topic and one has to consider what advantages can be offered by the block protocol and then to examine the price that must be paid.

The most obvious advantage of the T = 1 protocol is the ability to manage data flow in both directions. In our discussion of the T = 0 protocol it was shown that for a particular command that the data is either sent to or received from the ICC. This limitation was really due to the use of a single byte for defining the length of the data related to the command.

The T = 1 protocol also removes the T = 0 restriction of the master slave relationship where the interface device (IFD) always initiates a command to which the ICC responds. For this block protocol a command may be initiated by either the IFD or the ICC albeit within the restrictions of the protocol.

A further advantage of the T = 1 protocol is the ability to chain the blocks of data such that an arbitrarily large block of data may be transferred as the result of a single command by the transmission of the appropriate number of frames chained in sequence.

The block protocol also has a more sophisticated error management system. This allows the use of a block error detection code (EDC) and the ability to re-transmit blocks that are subject to some error condition. By comparison the T = 0 protocol has a primitive character error detection and correction scheme as described previously in the tutorial (part 4).

Clearly there is a price to be paid for this higher layer protocol. Apart from the more complex software in both the ICC and the IFD the protocol is more demanding on the RAM memory of the ICC which needs to maintain the last sent block in case retransmission is required. In general the T = 1 protocol offers advantages where the application is managing large blocks of data, particularly when it is required to pass data in both directions as part of a particular command. The efficiency of the protocol is only really apparent for larger data transmissions since the underlying physical layer is still operating in character mode as for the T = 0 protocol. The reduction of the character frame to 11 etu (elementary time units) compared with the 12 etu demanded by T = 0 has to be balanced against the administrative overhead of the frame structure which has both a prologue and epilogue.

There can be no doubt that the error control is significantly improved over the T = 0 protocol but at the lower speed of 9600 bit/second operated by many ICC's over very short transmission paths the probability of communication errors is much reduced. However it is clear that there is a move towards the use of the T = 1 protocol and it seems highly likely that this will become the predominant protocol of the future. We should not however dismiss the use of the T = 0 protocol which in some situations may well offer a more optimum technical solution. The T = 1 protocol is specified in the ISO standard ISO 7816 - 3 / AMD.1

#### The block frame

The frame consists of three fields,

- prologue field

- information field (optional)

- epilogue field

| Prologue Field  | 1                           |        | Information Field | Epilogue Field                |

|-----------------|-----------------------------|--------|-------------------|-------------------------------|

| Node<br>Address | Protocol<br>Control<br>Byte | Length | Optional          | Error Detection<br>LRC or CRC |

| NAD             | PCB                         | LEN    | INF               | EDC                           |

| 1 Byte          | 1 Byte                      | 1 Byte | 0-254 Bytes       | 1/2 Bytes                     |

The prologue field consists of three bytes,

- NAD the node address

- PCB protocol control byte

- LEN the data length

The NAD byte uses bits 3 -1 to identify the source address and bits 7 - 5 to identify the destination address. The bits 4 and 8 are used for Vpp control which will not be discussed further here. The node address byte allows the use of multiple logical channels where required otherwise both addresses should be set to zero.

The PCB byte allows the identification of three types of block frame,

- An information block (I block)

- A receive ready block (R block)

- A supervisory block (S block)

The information block is the frame which is used to transmit application commands and data between the ICC and the IFD. The receive - ready block is used as an acknowledgment when the protocol is sending data as a sequence of chained blocks. The supervising block is used to establish control parameters and to effect a resynchronisation or abort status as the result of some error condition. The information block also acts as an acknowledgement byte in the non chaining mode.

The LEN byte indicates the number of bytes (if any) in the information field of the frame. Its allowed range of values are from 00 - FE hex. This allows a maximum information field of 254 bytes.

The information field is used to convey the application commands and data which we will discuss in the next part of the tutorial.

The epilogue field contains the block error detection code which may be either an LRC (longitudinal redundancy check) or a CRC (cyclic redundancy check). The LRC is 1 byte whilst the CRC occupies 2 bytes. This option is defined by the specific interface characters.

## Specific Interface Characters.

In a previous part of the tutorial (part 4) we discussed the specific interface characters given by the answer to reset (ATR). The T = 1 protocol uses three of these characters to establish the necessary options before communication can take place. These bytes are assigned as follows (where i > 2),

TAi = IFSC (default = 32)TBi (bit 4 - 1) (default = 13)CWI = (bit 8 - 5) = BWI (default = 4)TCi (bit 1 = 1) = CRC option option (default) (bit 1 = 0) = LRC

The IFSC is the information field size for the card. There is also an IFSD which is the information field size for the interface device. This has a default value of 32 bytes and can only be changed by means of an S - block request from the IFD to the ICC.

## Waiting Times

The T = 1 protocol uses two waiting time parameters to help flow control,

- Character Waiting Time (CWT)

- Block Waiting Time (BWT)

The character waiting time is the maximum time between successive characters in a block whilst the block waiting time is the maximum time between the leading edge of the last character in a block sent be the IFD and the leading character of the next block sent by the card.

The character waiting time may be used to detect an error in the length of a block whilst the block waiting time may be used to detect an unresponsive card. There is also a block guard time (BGT) which is defined as the minimum time between the leading edge of the last character of one block and the leading edge of the first character in the new block to be sent in the alternative direction. The CWT and BWT are calculated from the values of CWI and BWI coded as shown previously in the specific interface bytes by means of the following equations,

- $\blacksquare \quad \text{CWT} = (2^{\text{BWI}} + 11) \text{ etu}$

- BWT =  $(2^{BWI} \times 960 \times 372 / f)$  Sec + 11 etu

Where f is the clock frequency.

The minimum value for the BWT is 100 mS + 11 etu when the card operates with the default frequency of 3.58 MHz. The block guard time has a value of 22 etu such that the delay between the start of the last character of a received block and the start of a transmitted block is greater than BGT but less than BWT. Accordingly the minimum inter block time is 11 etu which is equal to one character time.

## **Protocol Control Byte**

The protocol control byte identifies the different types of block and carries some control information including a single bit sequence number (N) and a block chaining bit (M). Other bits are used to identify transmission errors. The PCB is coded as follows.

| Туре |   | F | PCB ( | bits 8 | -1) |   |   |   | Function           |

|------|---|---|-------|--------|-----|---|---|---|--------------------|

| Ι    | 0 | N | 0     | 0      | 0   | 0 | 0 | 0 | Standard I Block   |

| Ι    | 0 | N | 1     | 0      | 0   | 0 | 0 | 0 | Chain bit set      |

| R    | 1 | 0 | 0     | N      | 0   | 0 | 0 | 0 | No errors          |

| R    | 1 | 0 | 0     | N      | 0   | 0 | 0 | 1 | EDC / Parity error |

| R    | 1 | 0 | 0     | N      | 0   | 0 | 1 | 0 | Other errors       |

| S    | 1 | 1 | 0     | 0      | 0   | 0 | 0 | 0 | Resynch request    |

| S    | 1 | 1 | 1     | 0      | 0   | 0 | 0 | 0 | Resynch response   |

| S    | 1 | 1 | 0     | 0      | 0   | 0 | 0 | 1 | IFS request        |

| S    | 1 | 1 | 1     | 0      | 0   | 0 | 0 | 1 | IFS response       |

| S    | 1 | 1 | 0     | 0      | 0   | 0 | 1 | 0 | Abort request      |

| S    | 1 | 1 | 1     | 0      | 0   | 0 | 1 | 0 | Abort response     |

| S    | 1 | 1 | 0     | 0      | 0   | 0 | 1 | 1 | WTX request        |

| S    | 1 | 1 | 1     | 0      | 0   | 0 | 1 | 1 | WTX response       |

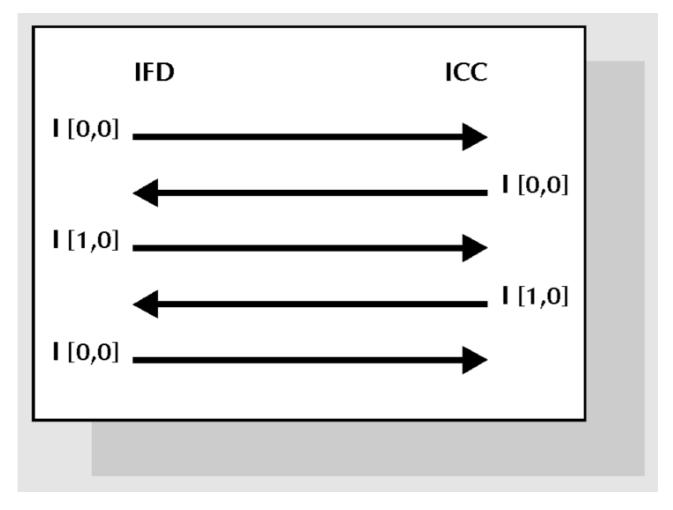

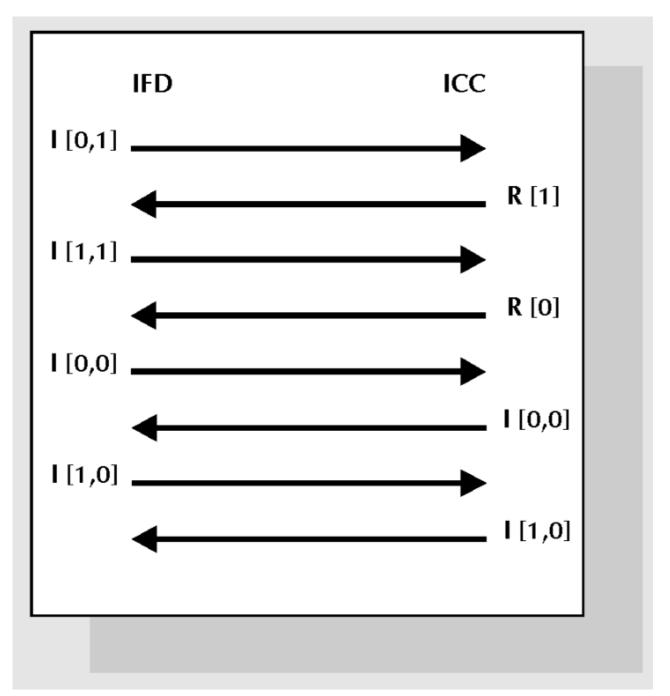

The I blocks can occur as independant blocks or as part of a chain. The 'More' bit is set to indicate that further blocks are to follow. The sequence number of the sender alternates between '0' and '1' starting with '0'.

The R blocks are used to acknowledge the successful or otherwise receipt of transmitted blocks. The sequence number N carries the value of the next expected value of N where the transmitter alternates the value as mentioned above. Whilst blocks transmitted as part of a chain must be acknowledged by an R block the receipt of a successful stand alone I block may be acknowledged by an I block response. The two correspondents manage the sequence numbers of their I blocks independently alternating between '0' and '1'. The R block has three possible states as shown in the table.

The S blocks are used to invoke four control states as shown in the table. The resynch request is used by the IFD (only) to force a reset of the block transmission parameters to their initial values. A chain may be aborted by either the IFD or ICC perhaps due to some physical error such as memory corruption. The ICC may send an IFS request to invoke a change in the IFSC it can support. Similarly the IFD may send an IFS request to indicate a new IFSD it can support. The S block control also allows the ICC to request an extension to the block waiting time (BWT) that may be necessary to execute a command received in an I block. The INF field in this block contains a single byte integer value which is to be calculated as a multiple of the BWT value. In all cases the receiver of an S block should send the appropriate response block.

## The T = 1 Protocol in Operation

Using the notation of the ISO 7816 standard we can show the basic operation of the protocol. A more complete definition can be obtained from the standard.

- I Blocks; I (N,M)

Where N = Sequence number (alternately`0' and `1')

- M = More data bit

The More data bit is set when an additional I block is to follow in the chain

$\blacksquare R Block; R(N)$

Where N = Sequence number of next expected block

The protocol defines that the IFD and the ICC each have the right to transmit in turn where communication commences with transmission of a block by the IFD.

Normal I block transmission

## I Block Transmission With Chaining

note that an I block was used by the ICC to acknowledge the last block in the chain sent by the IFD. The ICC may send chained blocks in the same way as shown for the IFD.

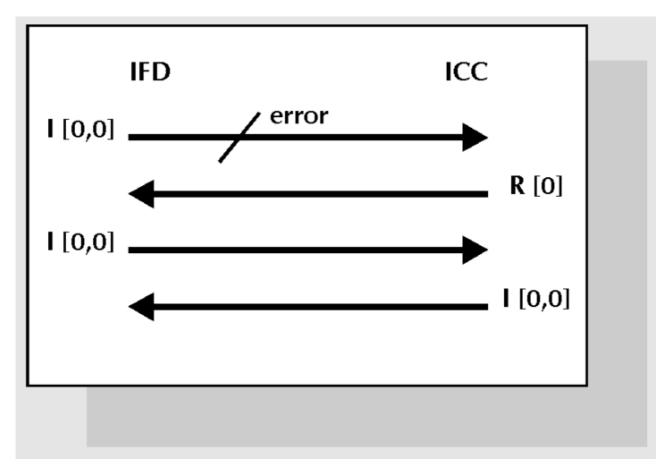

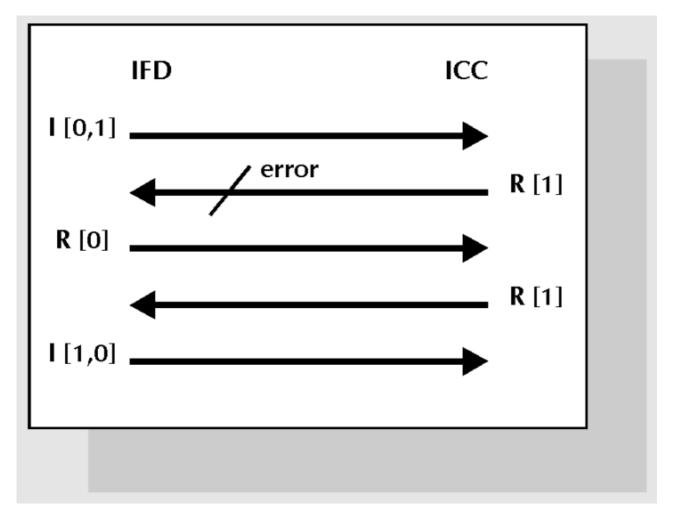

# Error Handling in I Block Transmission

Error in I block receipt

Error in I block chain response

In both cases the transmitter is notified to retransmit the block received in error. There are of course a large number of possible error scenarios but they are all based on the simple concepts shown above.

Next month we will look at the proposed Inter- Industry commands.

David Everett

## **Smart Card Tutorial Part 7**

## First Published in March 1993

#### Inter - Industry Commands for Interchange.

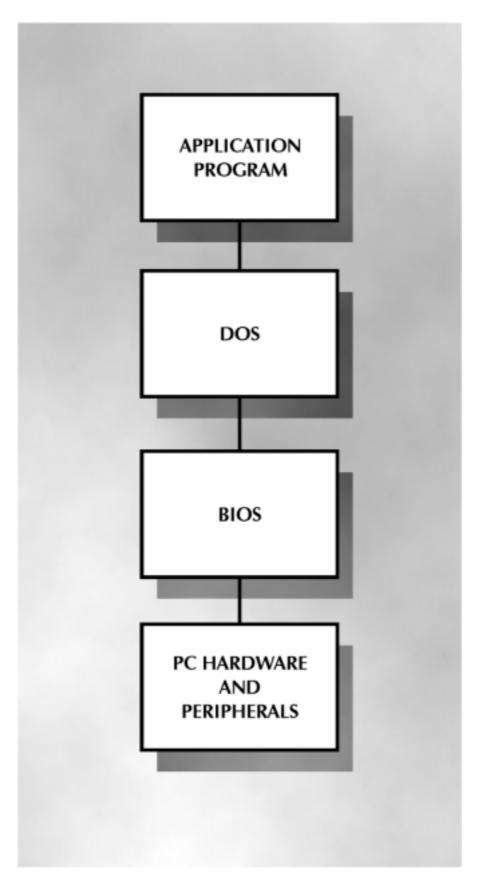

So far in the tutorial we have discussed the scope of the ISO Standard 7816 parts 1,2 and 3. As we have mentioned previously any concept of interoperability requires adherence to these basic standards for the physical and electronic properties of the IC card. Whilst we encountered problems, due largely to the need to maintain conformance with early comercial implementations of the IC card system, there is none the less an overwhelming industry acceptance of these standards. We are now going to have a look at the scope of the ISO 7816-4 draft standard which is still subject to significant disagreement.

For the purpose of the tutorial we will skate around the contentious areas and concentrate on the basic principle which is really the definition of a file management system and its interaction with a user. The following discussion will examine the four basic concepts of the ISO standard,

- File structure

- Message structure

- Basic commands

- Command and data transport.

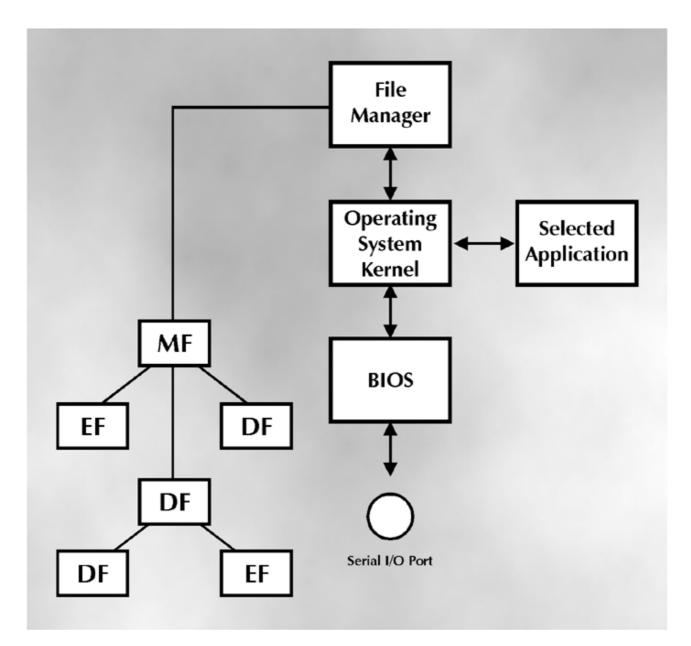

#### File structure

There are three categories of files,

- Master file (MF)

- Dedicated file (DF)

- Elementary file (EF)

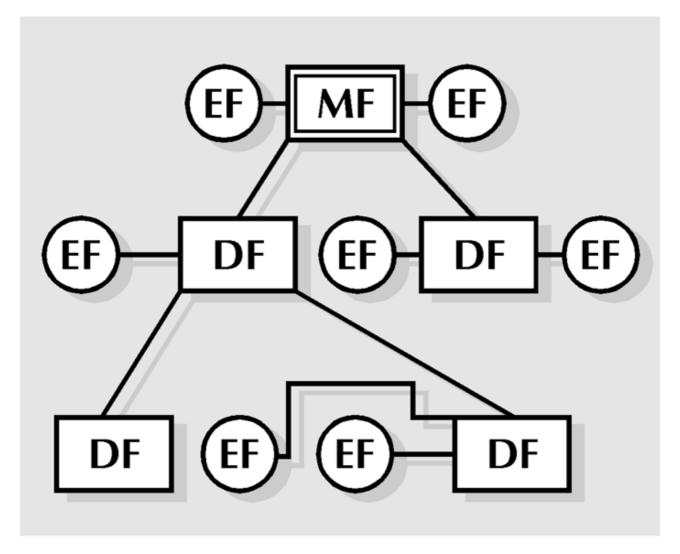

The Master file is a mandatory file for conformance with the standard and represents the root of the file structure. It contains the file control information and allocable memory. Depending on the particular implementation it may have dedicated files and /or elementary files as descendants (See fig 1).

A dedicated file has similar properties to the master file and may also have other dedicated files and/or elementary files as descendants.

#### **Figure 1: Logical File Organisation**

An elementary file is the bottom of any chain from the root MF file and may contain data as well as file control information. An elementary file has no descendants. A number of elementary file types are defined as follows,

- Working file

- Public file

- Application control file

- Internal secret file

The working file is for storing application data whilst the public file allows data to be accessed unconditionally. The application control file always allows read access whilst the internal secret file contains data not accessible outside of the IC.

Each file is referenced by a two byte identifier which allows the path to any file to be defined from the root directory. This path concept is the same principle as used in the PC by MSDOS. Dedicated files may also be referenced by file name.

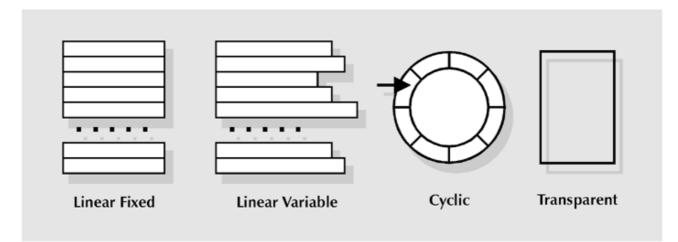

The data structure for an elementary file allows four options,

- Linear fixed

- Linear variable

- Cyclic

- Transparent

These four structures are shown symbolically in fig 2. The first three options are based on the use of records as encountered in any computer system. The transparent option just refers to a block of data without the record structure. In this case the data must be accessed by a relative address to the start of the data block. The first three structures would normally access data by reading and writing records. Where the file management system takes care of the absolute address of the data.

**Figure 2: Elementary File Structures**

This concept of a file structure really only permits the concept of reading and writing data into elementary files. The dedicated file concept allows a partition between data structures where a particular application may select a particular structure. This dedicated file may be used to control access to the data in the daughter elementary files by the use of password verification. In this sense the file structure supports the segregation of multi application data where the separate applications exist at the interface device.

This is really an incomplete picture which may support the historical use of IC cards as data carriers but does not define the principle of multi applications co-existing in the IC itself. What is really required is the concept of executing application programs in the IC and maintaining adequate security segregation between these applications. We shall return to this subject when we discuss the security of the IC card and we will show how this file structure concept may be extended in order to allow active multi - application operation.

The ISO 7816 - 4 proposed standard makes considerable use of the ASN.1 (Abstract Syntax Notation One) syntax rules for the encoding of data. These rules use the principle of TLV (Tag, Length, Value) encoding of the data field. The tag identifies this field, the Length parameter gives the size of the data (in bytes) whilst the value represents the field data. This concept allows variable length fields which may be individually identified. This is an alternative approach to a bit mapped structure where the fields and length are predefined and a single bit in a tag field is used to indicate the presence or otherwise of the field. A bit mapped approach was used in the ATR (Answer To Reset) data to indicate the presence or otherwise of the specific interface characters (see part 4 of the tutorial).

The ASN.1 encoding has a two byte overhead for each data field compared with the one bit of the bit mapped approach. Each encoding scheme has its benefits but it is clear that when data space is at a premium then the bit mapped approach is better whilst the ASN.1 encoding offers more general flexibility. Some concerns have been raised in that the use of ASN.1 may be subject to patent royalties.

The file control information referred to earlier for the MF and DF files is proposed to consist of two parts,

■ The file control parameters (FCP)

#### The file management data (FMD)

The file control parameters are defined as an ASN.1 encoded data field that describes the necessary parameters such as file size, file identifier and optionally the file name. It also defines the type of file (i.e MF, DF, or EF) and the data structure (i.e Linear fixed, linear variable, cyclic or transparent). The proposed coding tables are given in the standard.

The file management data is also constructed as an ASN.1 object and may contain Inter - Industry or provider specific objects. It may be used for example to store security data for encipherment or password checking.

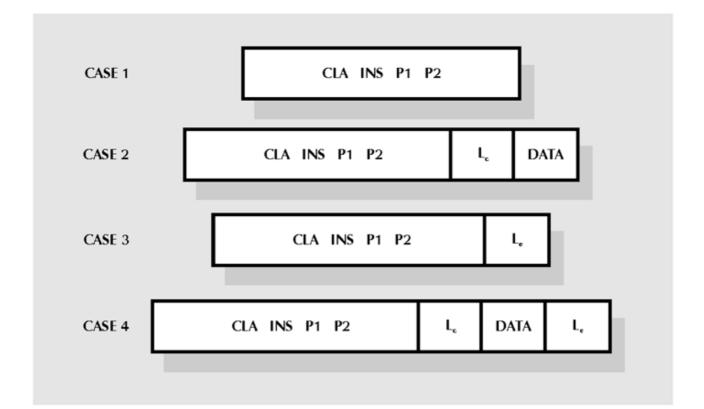

## Message Structure

This part of the standard builds on the command response structure described in part 3 of the standard by defining the concept of an application protocol data unit (APDU). This APDU contains the command or response message and allows for all options of data transfer, as shown in table 1.

The result is an APDU which can define the length of data to be transmitted in each direction. The structure of the APDU is shown in fig 3.

The fields in the APDU are an extension of those described earlier as shown in table 2. for a command APDU.

It should be noted that this allows a number of options. The data length field may be either 1 byte (the default) or up to three bytes. This extended operation is identified by an optional field contained within the historical bytes of the ATR. Depending on the command/response data type shown in table 1. the Lc and Le field may or may not be present, for the cases 1 and 3 there is no command data. The APDU only contains those fields that are used as shown in fig 4.

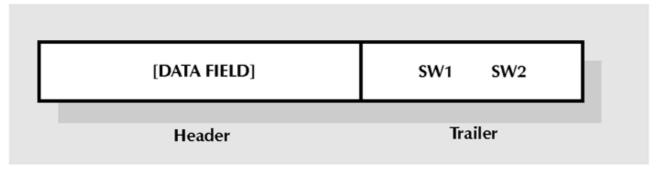

The response APDU contains the response data field (if present) and the status bytes referred to in part 4 of the tutorial as shown in fig 5. These status bytes have a normal response code of 9000 hex. A number of error conditions have been identified and are described in the proposed standard.

| CASE | COMMAND | RESPONSE |

|------|---------|----------|

| 1    | NO DATA | NO DATA  |

| 2    | DATA    | NO DATA  |

| 3    | NO DATA | DATA     |

| 4    | DATA    | DATA     |

Table 1. Command/Response Data Option

| Code          | Name          | Length          | Description                                       |

|---------------|---------------|-----------------|---------------------------------------------------|

| CLA           | Class         | 1               | Class of Instruction                              |

| INS           | Instruction   | 1               | Instruction code                                  |

| P1            | Parameter 1   | 1               | Instruction parameter 1                           |

| P2            | Parameter 2   | 1               | Instruction parameter 2                           |

| Lc            | Length of     | variable        | Number of bytes                                   |

| field         | Command Data  | ≤3              | present in the data field                         |

| Data<br>field | Data          | variable<br>=Lc | String of data bytes sent in the command          |

| Le            | Length of     | variable        | Maximum number of data bytes expected in response |

| field         | Response Data | ≤3              |                                                   |

Table 2. Fields in the application protocol data unit

| CLA INS P1 P2 | [L, FIELD] [DATA FIELD] [L, FIELD] |

|---------------|------------------------------------|

| Header        | Body                               |

Figure 3: Command APDU

## Figure 5: Response APDU Structure

Next month we will continue our analysis of the proposed Inter-Industry commands

David Everett

## **Smart Card Tutorial - Part 8**

## First Published in April 1993

## Inter Industry Communications for interchange - continued.

In this part of the tutorial we will look at the basic commands described in the draft ISO 7816-4 standard. As we have mentioned previously these commands really operate against the assumption of a passive file management architecture. In other words the application in the card is really a file management system with some attention paid to access control. This of course was the only situation possible with a memory type smart card. The advent of microprocessor chips in the smart card opens up new avenues for active applications within the card. Under these circumstances it seems unlikely that such applications would allow many of the commands described here, who for example would allow any terminal to write, uncontrollably to the memory of an electronic purse application. One of the main advantages of a smart card is as a secure data carrier and in our next part we will take an initial look at security to see how everything needs to fit together.

In part 7 we described the command APDU (Application Protocol Data Unit) as shown in fig 1.

The body of this command APDU contains the data (if present) and one or two bytes defining the length of the data sent or received (see part 7 for further detail).

Observant readers will have noticed that earlier in the series when we described the T=0 communication protocol (part 5), we refer only to a fixed 5 byte header. The command APDU shown in fig.1 has only 4 bytes. Well this new part to the standard is aimed at a more general purpose application protocol data unit which allows for data to be sent in both directions (not available when using T = 0). But this part of the standard is none the less upward compatible since the 5th byte was used to indicate the length of the data which now exists in the body of the command as the 1st byte of the body of the APDU.

| CLA | INS  | P <sub>1</sub> | Pa | Body |

|-----|------|----------------|----|------|

| CER | 1110 | • 1            | 12 | Body |

Header

Fig 1. Command APDU Structure

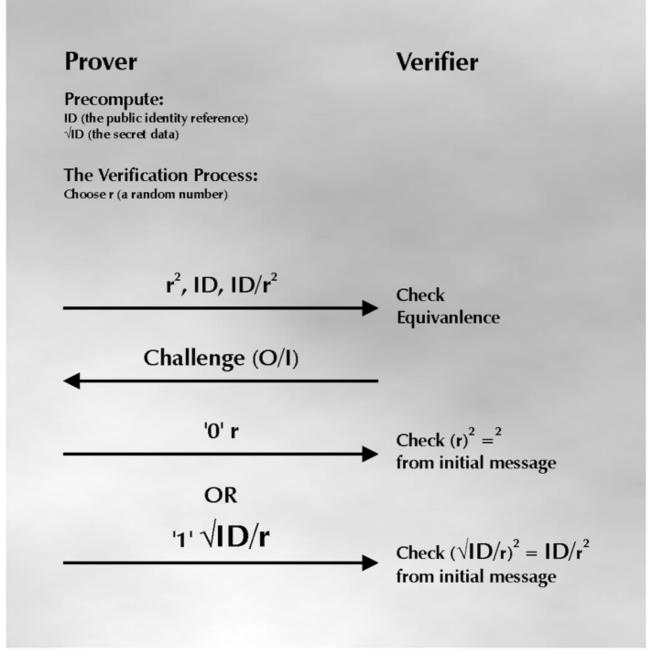

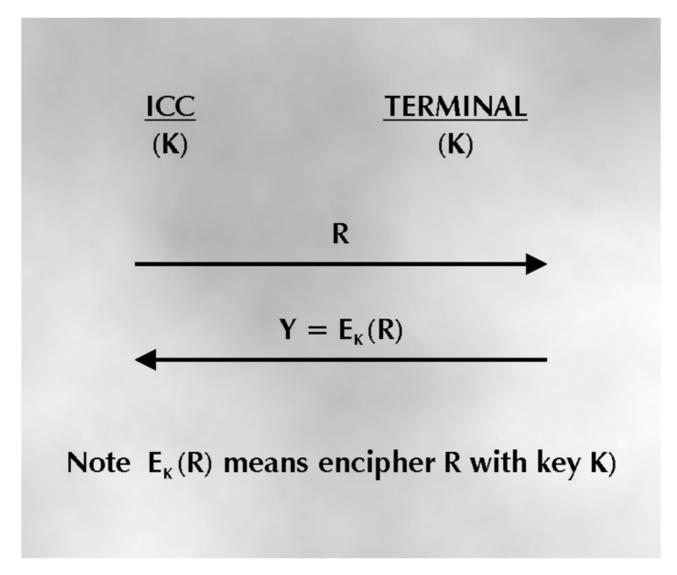

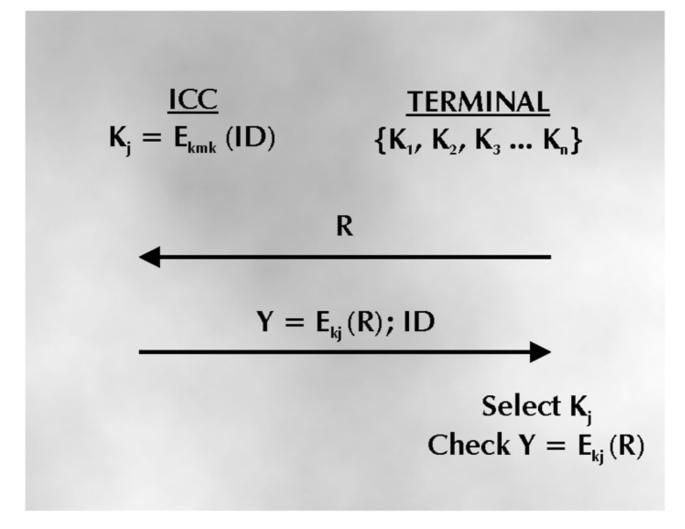

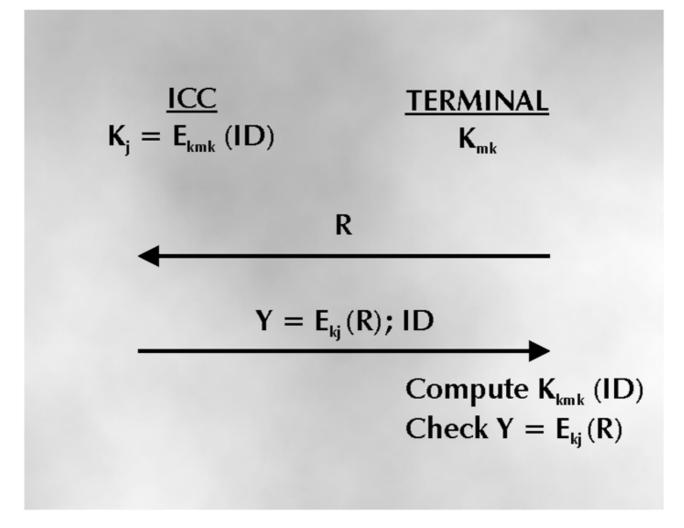

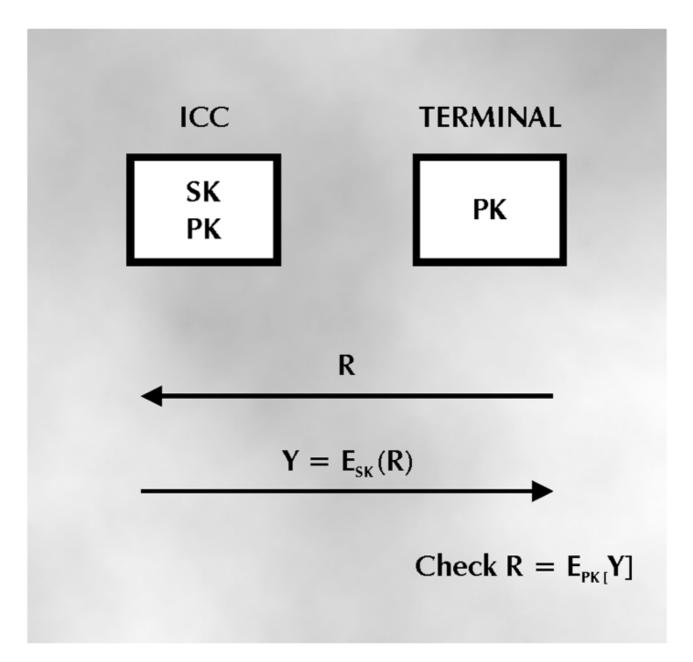

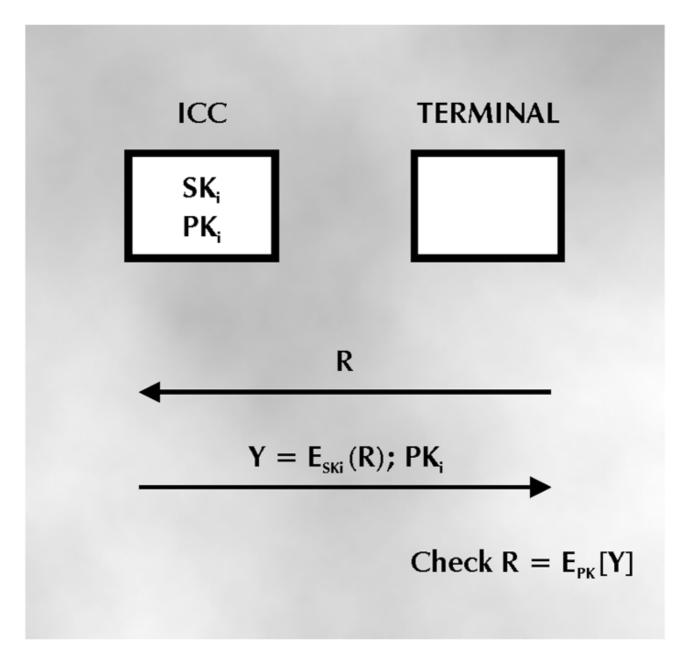

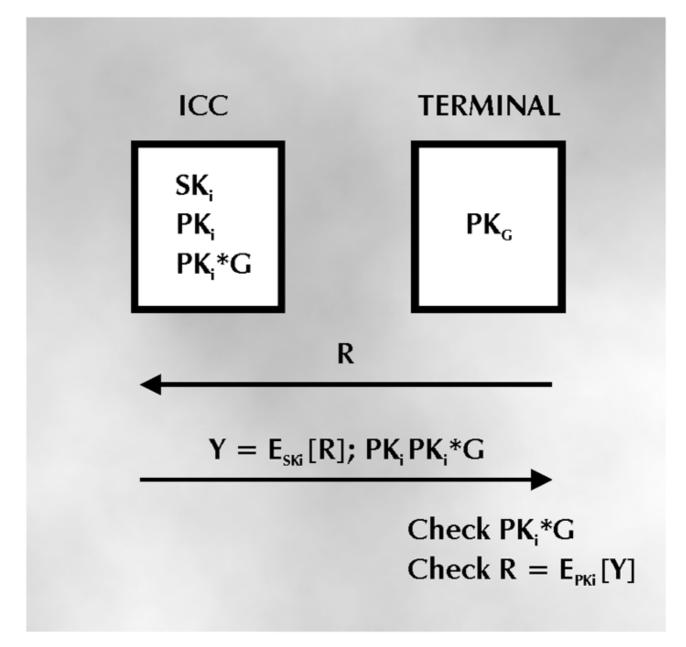

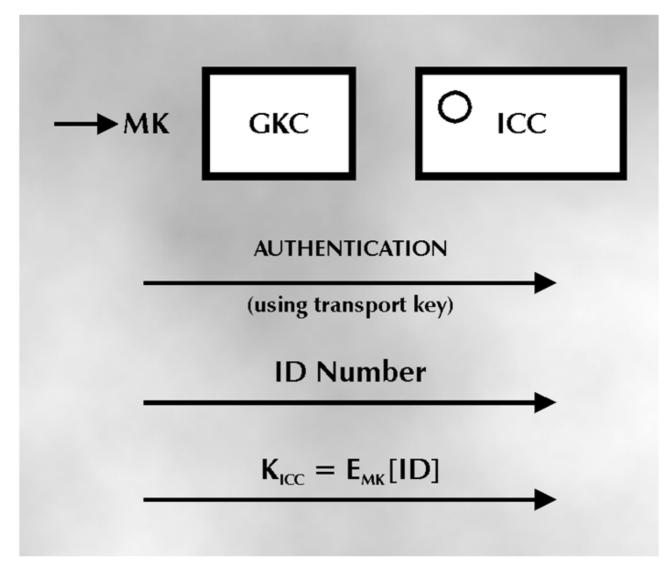

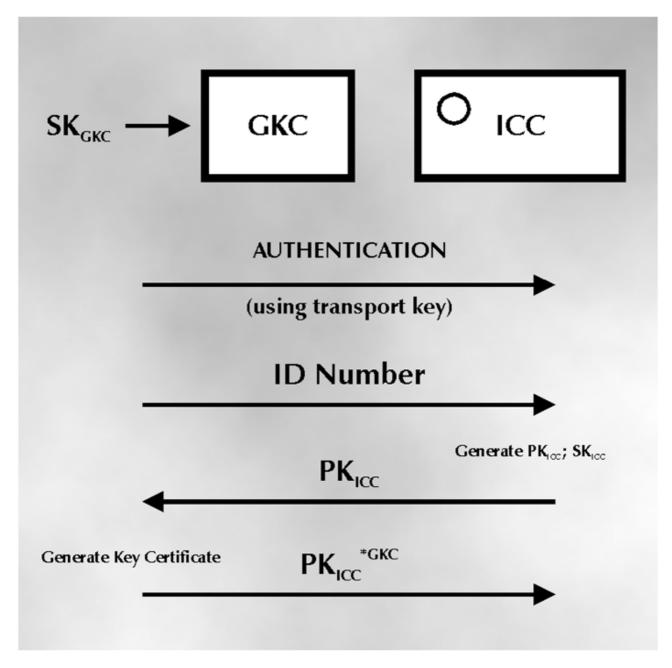

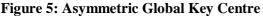

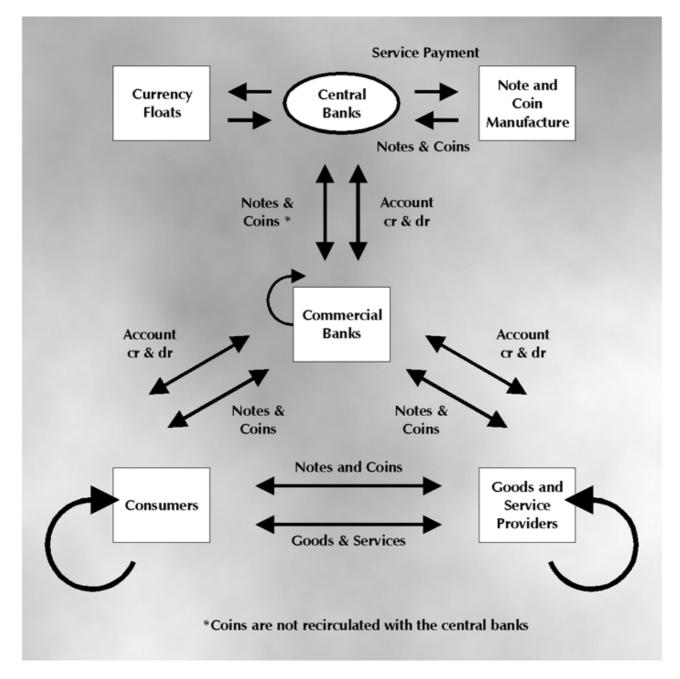

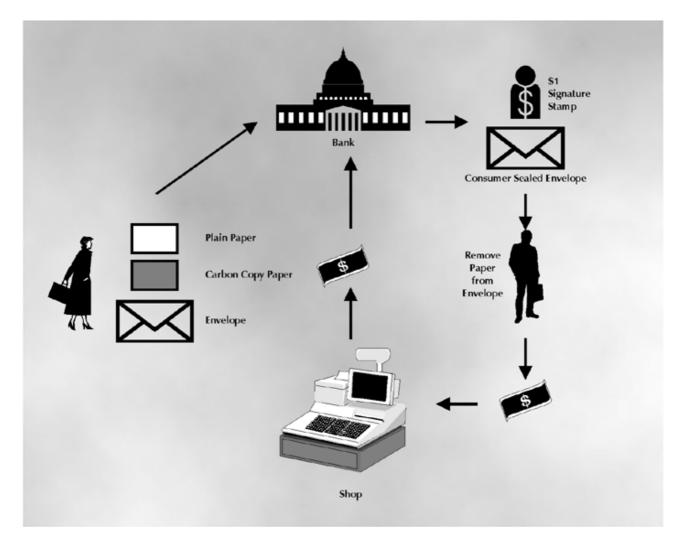

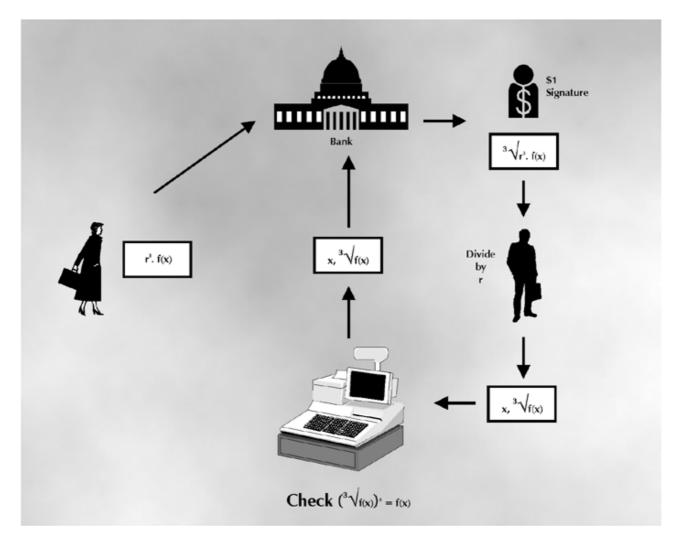

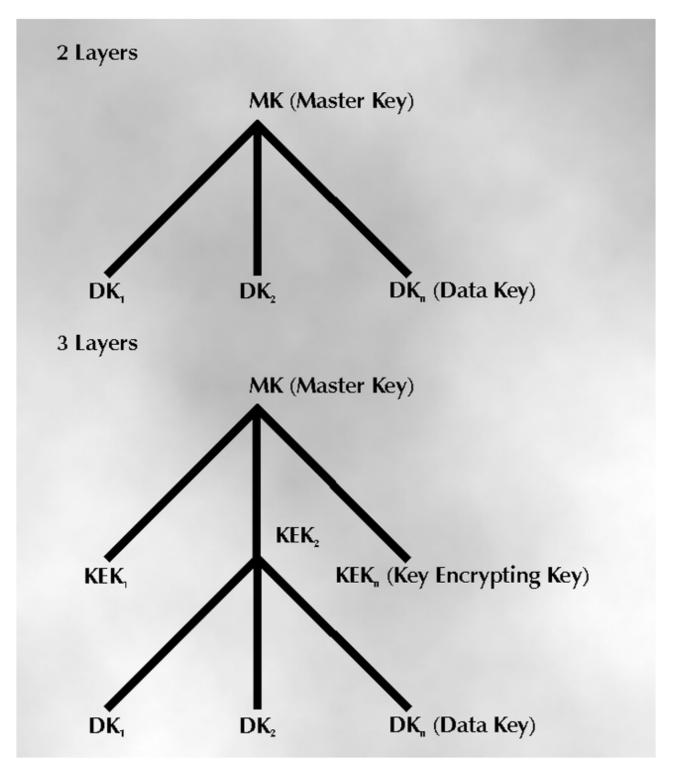

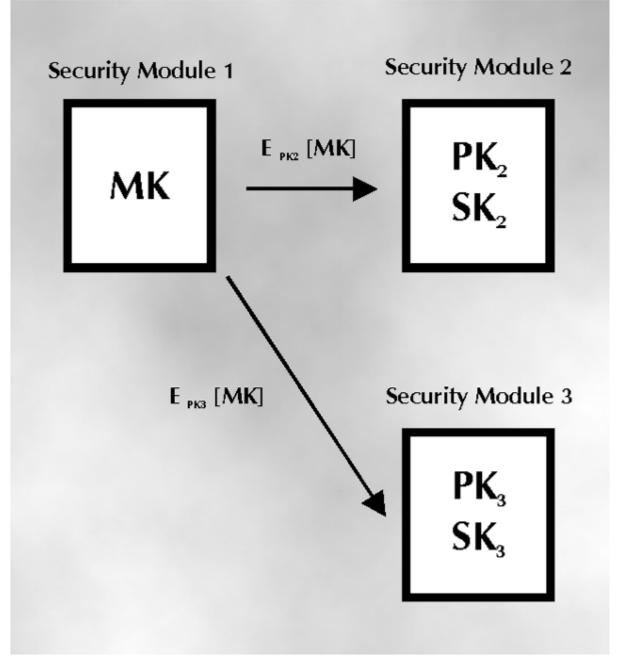

| b8 | b7 | b6 | b5 | Meaning                                                                                      |